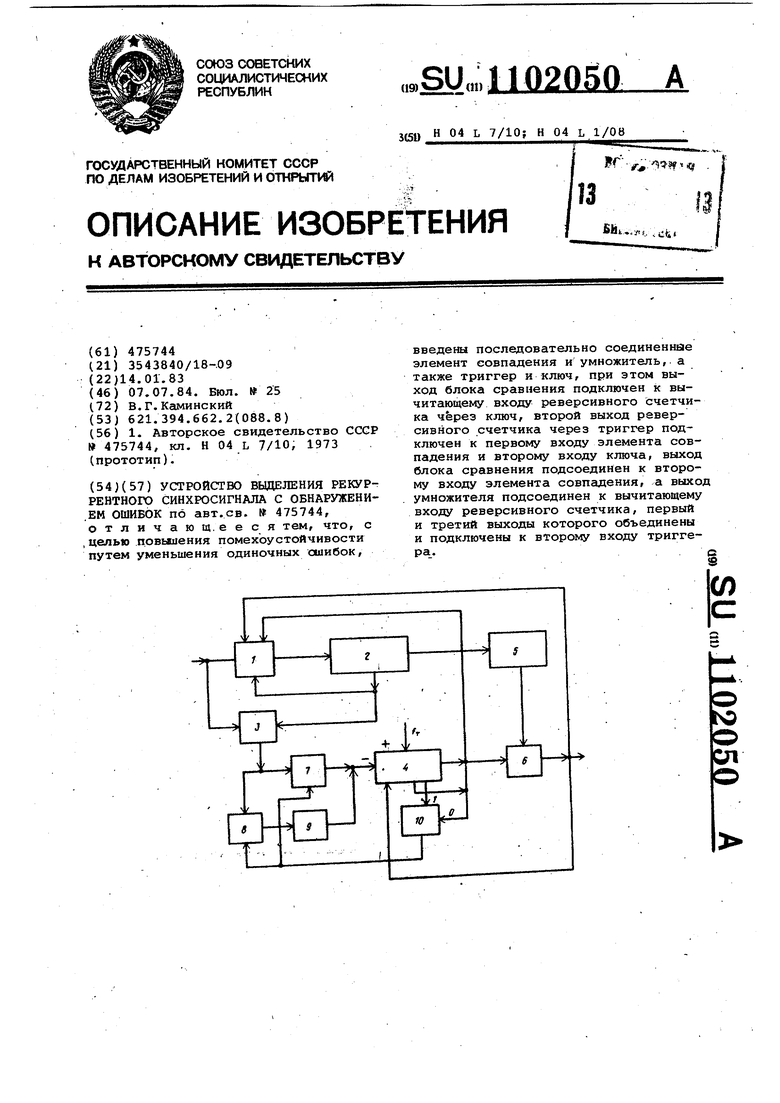

Изобретение относится к области передачи телеграфной информации и передачи данных и может быть исполь зовано для обеспечения помехоустойч вой синхронизации систем передачи двоичной информации. По основному авт.св. № 475744 известно устройство выделения рекур рентного синхросигнала с обнаружение ошибок, содержащее последовательно соединенные переключатель режимов работы, блок проверки на рекуррентность, селектор и элемент К, причем второй выход блока проверки на рекур рентность подключен к первым входам переключателя режимов работы и блока сравнения, к второму входу которого подключен второй вход переключателя режимов работы, а также реверсивный счетчик, при этом выход блока сравне ния через реверсивный счетчик подклю чей к третьему входу переключателя режимов работы и к второму входу эле ментд И,выход которого подключен к четвертому входу переключателя режимов работы и второму входу реверсивнего счетчика, на суммирующий вход которого подана тактовая частота Щ Однако при приеме искаженного дво ичного знака синхронизации возможно многократное размножение ошибки, что приводит к недостаточной помехоустой чивости устройства выделения рекуррентного синхросигнала с обнаружением ошибок. Цель изобретения - повышение по.мехоустойчивости путем уменьшения одиночных ошибок. . Эта цель достигается тем, что в устройство выделения рекуррентного синхросигнала с обнаружением ошибок содержащее последовательно соединенные переключатель режимов работы, олрк проверки на рекуррентность, селектор и элемент И, причем второй выход блока проверки на рекуррентность подключен к первым входам пере ключателя режимов работы и блока сравнения, к,второму входу которого подключен второй вход переключателя режимов работы, а также реверсивный счетчик, при этом -выход блока сравнения через реверсивный счетчик подключей к третьему входу переключателя режимов работы и к второму входу элемента И, выход которого подклю чен к четвертому входу переключателя режимов работы и второму входу ревер сивного счетчика, на суммирующий вход которого подана тактовая частота, введены последовательно соединен ные элемент совпадения и умножитель, а также триггер и ключ, при этом выход блока сравнения подключен к вычитающему входу реверсивного счетчика через ключ, второй выход реверсивного счетчика через триггер подключен к первому входу элемента совпадения и второму входу ключа, выход блока сравнения подключен к второму входу элемента совпадения, а выход умножителя подсоединен к вычитающему входу реверсивного счетчика, первый и третий выходы которого объединены и подключены к второму входу триггера. На чертеже представлена структурно-электрическая схема устройства выделения рекурретного синхросигнала с обнаружением ошибок. Устройство выделения рекуррентного синхросигнала с обнаружением ошибок содержит переключатель 1 режимов работы, блок 2 проверки на рекуррентность, блок 3 сравнения, реверсивный счетчик 4, селектор 5, элемент И 6, ключ 7, элемент 8 совпадения, умножитель 9 и триггер 10. Устройство вьаделения рекуррентного синхросигнала с обнаружением ошибок работает следующим образом. Принимаемая последовательность двоичных знаков через переключатель 1 поступает в блок 2 проверки на рекуррентность; В этом узле, содержащем триггер сдвига на К знаков с точками съема на сумматоры по модулю 2 (в соответствии с многочленом Р/х/) , принимаемые знаки проверяются на соответствие закону построения рекуррентного кода. Так, например, для Р(Х) л +Х 1 уравнение проверки имеет вид 1 U-5) ®(i-6) где.Х - принимаемые знаки из канала связи; © - сложение по модулю 1. Результаты сравнения образуются в блоке 3 сравнения и далее просчитываются реверсивным счетчиком 4. Причем просчет ведется в двух режимах. Первоначально, когда после очередного фазирования сигналом с первого ВЕЛХода реверсивного счетчика 4 триггер 10 устанавливает в положение О, сигналы с блока 3 сравнения через ключ 7 поступают на отрицательную шину реверсивного счетчика 4. При этом каждое несравнение, определяемое наличием единицы на выходе блока 3, производит сдвиг реверсивного счетчика 4 на один шан. После набора реверсивным счетчиком 4 определенного объема, когда до порога его срабатывания остается К единиц, сигналом с выхода реверсивного счетчика 4 триггер 10 устанавливается в единичное состояние. Начиная с этого момента, единичный сигнал с блока 3 сравнения через элемент 8 совпадения поступает на умножитель 9, с выхода которого формируется серия единиц в К двоичных знаков, которые, поступая на отрицательную шину реверсивного счетчика .4 производят его сдвиг на к знаков. Это i гарантирует то, что искаженный знак успевает, выйти из регистра сдвига блока 2 и, следовательно, не влияет на правильность выделения фазиругощего сигнала. При каждом удовлетворении рекуррентному закону по суммирую щей шине на вход реверсивного счетчи ка 4 подается импульс тактовой часто ты и при наборе заданного порога сра батывания на его первом выходе появляется сигнал, который на переключателе 1 отключает поступление знаков из канала связи и переводит регистр сдвига блока 2 на автономное генерирование рекуррентной последовательности. Селектор 5, подключенный к блоку 2, при достижении селектируемой К значной комбинации через элемент И 6 выдает фазируюший сигнал. Этот сигнал возвращает устройство выделения рекуррентного синхроимпуль са с обнаружением ошибок к исходному состоянию, размыкая цепь обратной связи блока 2 через переключатель 1 и сбрасывая реверсивный счетчик 4 в О. Таким образом, на первичном этапе фазирования реверсивный счетчик 4 при наличии несовпадения сбрасывается на один знак, а не на К знаков. Это приводит к тому, что по рассматриваемому примеру при наличии одного искаженного двоичного знака фазирующей посылки, поступившего из канала связи на вход блока 2 проверки на рекуррентность, реверсивный счетчик 4 сбросится на 3 шага, а е на 18, как в известном устройстве, за счет чего ускоряется процесс набора необходимого количества знаков реверсивным счетчиком 4 и увеличивается вероятность приема фазирующей посылки, т.е. ее помехоустойчивость при работе на каналах связи с помехами. При наборе реверсивным счетчиком 4 просчитанного объема в (Е -к) знаков, где f - предельный объем счета, с целью обеспечения гарантии заполнения регистра в блоке 2 только проверенными знаками, сброс реверсивного счетчика 4 при каждом несовпадении производится на К знаков. При проведении вычитания при прохождении через отметку (f -V -1) сигналом с выхода реверсивного счетчика 4 триггер 10 устанавливается в исходное нулевое состояние,обеспечивая вычитание в реверсивном счетчике 4 при появлении каждого несовпа-дения только на одну единицу. Технико-экономическая эффективность устройства вЕзщеления рекуррентного синхросигнала с обнаружением ошибок заключается в повышении поме-хоустойчивости за счет уменьшения влияния одиночных ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU604173A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1975 |

|

SU566380A2 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для выделения рекуррентного синхросигнала | 1976 |

|

SU576672A1 |

| Устройство выделения рекурентного сигнала с обнаружением ошибок | 1978 |

|

SU758552A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU559426A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1973 |

|

SU502516A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1986 |

|

SU1363510A1 |

УСТРОЙСТЮ ВЫДЕЛЕНИЯ РЕКУРРЕНТНОГО СИНХРОСИГНАЛА С ОБНАРУЖЕНИ.ЕМ ОШИБОК по авт.св. № 475744, отличающ.ееся тем, что, с ,целью повышения помехоустойчивости путем уменьшения одиночных сшибок. введены последовательно соединенные элемент совпадения и умножитель,. а также триггер и ключ, при этом выход блока сравнения подключен к вычитающему входу реверсивного счетчика через ключ, второй выход реверсивного счетчика через триггер подключен к первому входу элемента совпадения и второму входу ключа, выход блока сравнения подсоединен к второму входу элемента совпадения, а выход умножителя подсоединен к вычитающему входу реверсивного счетчика, первый и третий выходы которого объединены и подключены к второму входу триггерэ.-с (Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1973 |

|

SU475744A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-07-07—Публикация

1983-01-14—Подача