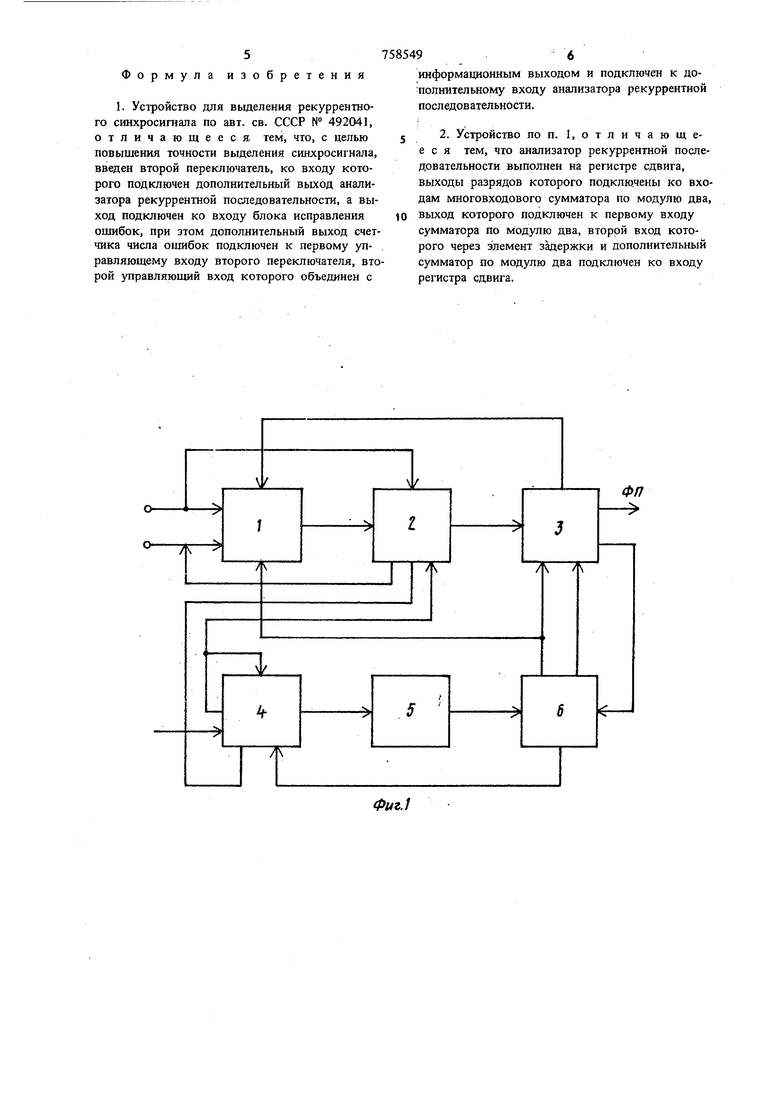

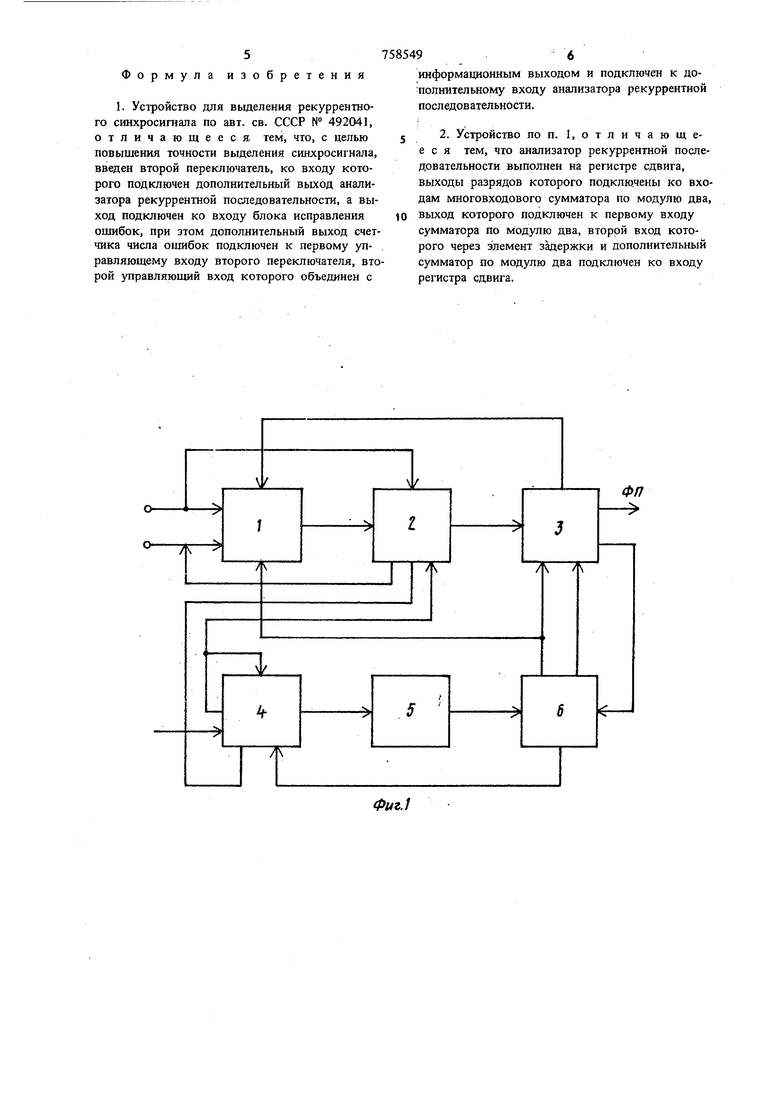

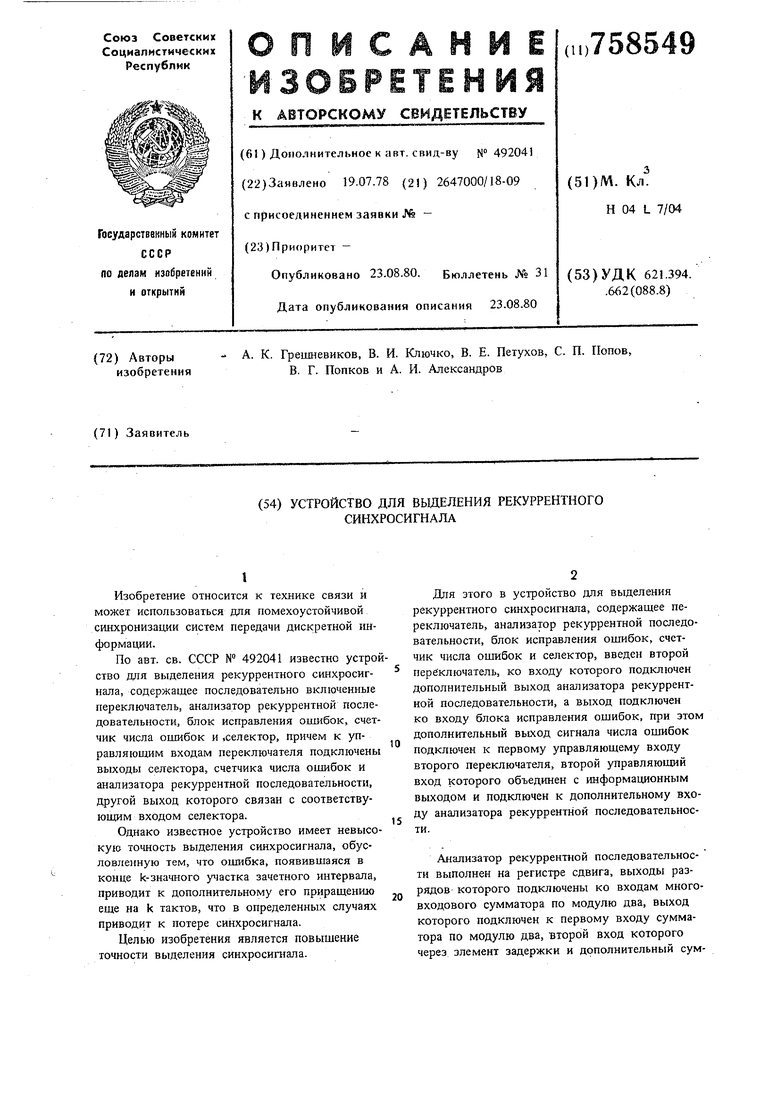

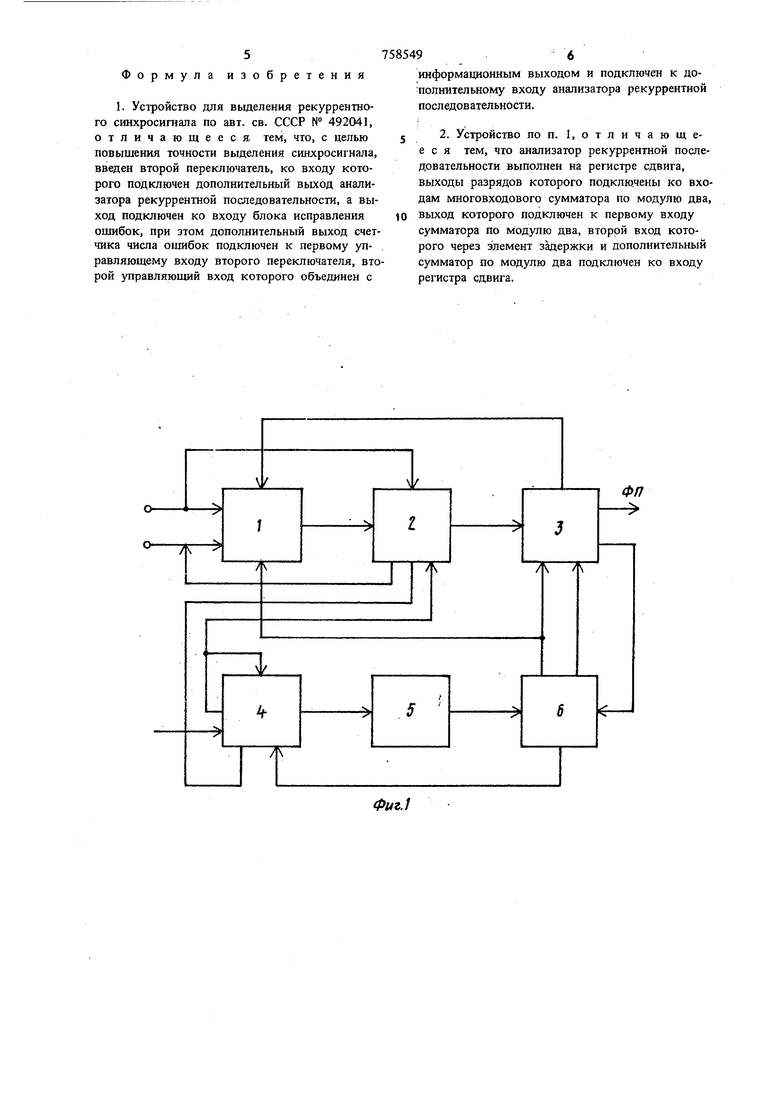

Изобретение относится к технике связи и может использоваться для помехоустойчивой сШ1хронизации систем передачи дискретной информации. По авт. св. СССР № 492041 известно устро ство для выделения рекуррентного синхросигнала, содержащее последовательно включенные переключатель, анализатор рекуррентной последовательности, блок исправления ошибок, счетчик числа ошибок и .селектор, причем к управляющим входам переключателя подключены выходы селектора, счетчика числа ошибок и анализатора рекуррентной последовательности, другой выход которого связан с соответствующим входом селектора. Однако известное устройство имеет невысокую точность выделения синхросигнала, обусловленную тем, что ошибка, появившаяся в конце k-значного участка зачетного интервала, приводит к дополнительному его приращению еще на k тактов, что в определенных случаях приводит к потере синхросигнала. Целью изобретения является повышение точности выделения синхросигаала. Для этого в устройство для выделения рекуррентного синхросигнала, содержащее переключатель, анализатор рекуррентной последовательности, блок исправления ошибок, счетчик числа ошибок и селектор, введен второй переключатель, ко входу которого подключен дополнительный выход анализатора рекуррентной последовательности, а выход подключен ко входу блока исправления ошибок, при этом дополнительный выход сигнала числа ошибок подключен к первому управляющему входу второго переключателя, второй управляющий вход которого объединен с информационным выходом и подключен к дополнительному входу анализатора рекуррентной последовательности. Анализатор рекуррентной последовательности выполнен на регистре сдвига, выходы разрядов которого подключены ко входам многовходового сумматора по модулю два, выход которого подключен к первому входу сумматора по модулю два, второй вход которого через элемент задержки и дополнительный сумматор по модулю два подключен ко входу регистра сдвига. На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема анализатора рекуррентной последовательности. Устройство для выделения рекуррентного синхросигнала содержит первый переключатель анализатор 2 рекуррентной последовательности, селектор 3, второй переключатель 4, блок 5 исправления ошибок и счетчик 6 числа ошибок. Первый переключатель 1 обеспечивает вклю чение анализатора 2 рекуррентной последовател ности в автономньш режим генерации рекуррен ной последовательности. В анализаторе 2 рекуррентной последовател ности принимаемые элементы последовательнос ти проверяются на соответствие закону построения рекуррентного кода. Селектор 3 определяет момент окончания выделения синхросигнала. Второй переключател коммутирует цепь выхода анализатора 2 рекур рентной последовательности 2. Блок 5 исправления ошибок обеспечивает запрет выдачи в счетчик 6 числа ошибок ложных импульсов несовпадения. Счетчик 6 числа ошибок осуществляет подсчет нулей зачетиого интервала рекуррентного синх-росигнала. Анализатор 2 рекуррентной последовательности выполнен на регистре сдвига 7 (7-1 7-К, где К - число разрядов), выходы разрядов которого подключены ко входам многовходового сумматора 8 по модулю два, выход которого соед1шеи с первым входом сумматора 9 по модулю два, другой вход которого через элемент задержки 10 и дополнительный сумматор 11 по модулю два подключен ко входу регистра сдвига. Предложенное устройство работает следующим образом. В режиме дежурного приема первый переключатель 1 находится в таком положении, что его первый вход подключен к информационному входу анализатора 2 рекуррентной последователыюсти и двоичные знаки принимаемой последовательности поступают одновременно на оба входа рекуррентной последовательности цифрового фильтра, в котором по символам, записанным в соответствии с поступающей дво ичной последовательностью, формируются по рекуррентному закону контрольные бинарные знаки и производится сравнение принимаемых и контрольных знаков. При возникновении в принимаемом синхросигнале ошибки в резул тате его сравнения с контрольным, сигналом анализатором 2 рекуррентной последовательнос 4 ти через второй переключатель 4 в блок 5 исравления ошибок выдается импульс. Импульс с левого плеча, соответствующего прямому направлению счета счетчика 6 числа ошибок, переводит первый переключатель 1 в другое состояние и открывает по выходу сеектор 3. При этом анализатор 2 рекуррентной последовательности переходит в режим автономного формирования последующей части рекуррентного синхросигнала. В момент считывания с анализатора 2 рекуррентной последовательности комбинации кода синхросигнала селектор 3 выдает на выход импульс фазового пуска (ФП) и переводит первый переключатель 1 в исходный режим дежурного приема. Чтобы уменьшить вероятность потери синхросигнала вследствие приращения длины анализируемого интервала при возникновении одиночной ошибки в последних k разрядах рекуррентной последовательности и совпадения конца анализируемого участка с окончанием синхросигнала, предлагаемое устройство обеспечивает исправление ошибочного знака. Для этого за k тактов до окончания своей работы счетчик 6 числа ошибок вьщает сигнал на второй переключатель 4, который коммутирует выход анализатора 2 рекуррентной последовательности со входа блока 5 исправления ошибок на свой дополнительный вход. В результате появившийся в канале связи ошибочный знак на сумматоре 9 по модулю два исправляется, а второй переключатель 4 возвращается в исходное состояние, что позволяет обнаружить многократную ошибку. Элемент задержки 10 обеспечивает одновремешюе поступление сигналов, подаваемых на его оба входа. Предлагаемое. устройство имеет более высокую -точность выделения синхросигнала, чем известное. В известном устройстве синхросигнал не выделяется при условии, что конец зачетного интервала совладает с концом рекуррентной последовательности и имеет место ошибка в k последних разрядах последовательности. Если зачетный интервал равен длине последовательности п и качество канала связи характеризуется вероятностью искажения одного элемента РО, то вероятность потери синхросигнала в известном устройстве определяется выражением Pf- пРо в предложенном устройстве эта вероятность будет Рп2 (n-k)Po.. Таким образом имеет место уменьшение потери синхросигнала на величину Р - Р 100% Формула изобретения 1. Устройство для выделения рекуррентного синхросигнала по авт. св. СССР № 492041, отличающееся тем, что, с целью повышения точности выделения синхросигнала, введен второй переключатель, ко входу которого подключен дополнительный выход анализатора рекуррентной последовательности, а выход подключен ко входу блока исправления ошибок, при этом дополнительный выход счетчика числа ошибок подключен к первому управляющему входу второго переключателя, вто рой управляющий вход которого объединен с 7585 5 )0 9. 6 информационным выходом и подключен к до полнительному входу анализатора рекуррентной последов ательности. 2. Устройство по п. 1, о т л и ч а ю щ ее с я тем, что анализатор рекуррентной последовательности выполнен на регистре сдвига, выходы разрядов которого подключены ко входам многовходового сумматора по модулю два, выход которого подключен к первому входу сумматора по модулю два, второй вход которого через элемент задержки и дополнительный сумматор по модулю два подключен ко входу регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекурентного сигнала с обнаружением ошибок | 1978 |

|

SU758552A1 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для выделения рекуррентного синхросигнала | 1973 |

|

SU492041A1 |

| Устройство для выделения рекуррентного синхросигнала с исправлением ошибок | 1976 |

|

SU568189A1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Устройство для выделения рекуррентоного синхросигнала с исправлением ошибок | 1976 |

|

SU618859A1 |

| Устройство для цикловой синхронизации с исправлением одиночных ошибок в рекуррентной последовательности | 1971 |

|

SU454705A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU559426A1 |

Авторы

Даты

1980-08-23—Публикация

1978-07-19—Подача