{54)УСТРОЙСТВО ВВДЕЛЕНИЯ РЕКУРРЕНТНОГО СИГНАЛА С ОБНАРУЖЕНИЕМ ОШИБОК

1

Изобретение относится к электросвязи и может использоваться в системах передачи двоичной информации.

Известно устройство выделения рекурентного сигнала с обнаружением ошибок, содержащее последовательно соединенные переключатель режимов работы, блок проверки на рекуррентность, селектор и элемент И, выход которого подключен к одному из входов переключателя режиМов работы, управляющий вход которого соединен с выходом реверсивного счетчика и другим входом элемента И, причем другой выход блока проверки на рекуррентность подключен к другому вхо ду переключателя режимов работы и первому входу блока сравнения, к второму входу которого подключен другой выход переключателя режимов работы 1 .

Однако, известное устройство имеет невысокую, точность выделения рекуррентного синхросигнала.

Цель изобретения - повышение точности выделения рекуррентного синхросигнала.

Для этого в устройство выделения рекуррентного сигнала с обнаружением .ошибок, содержащее последовательно

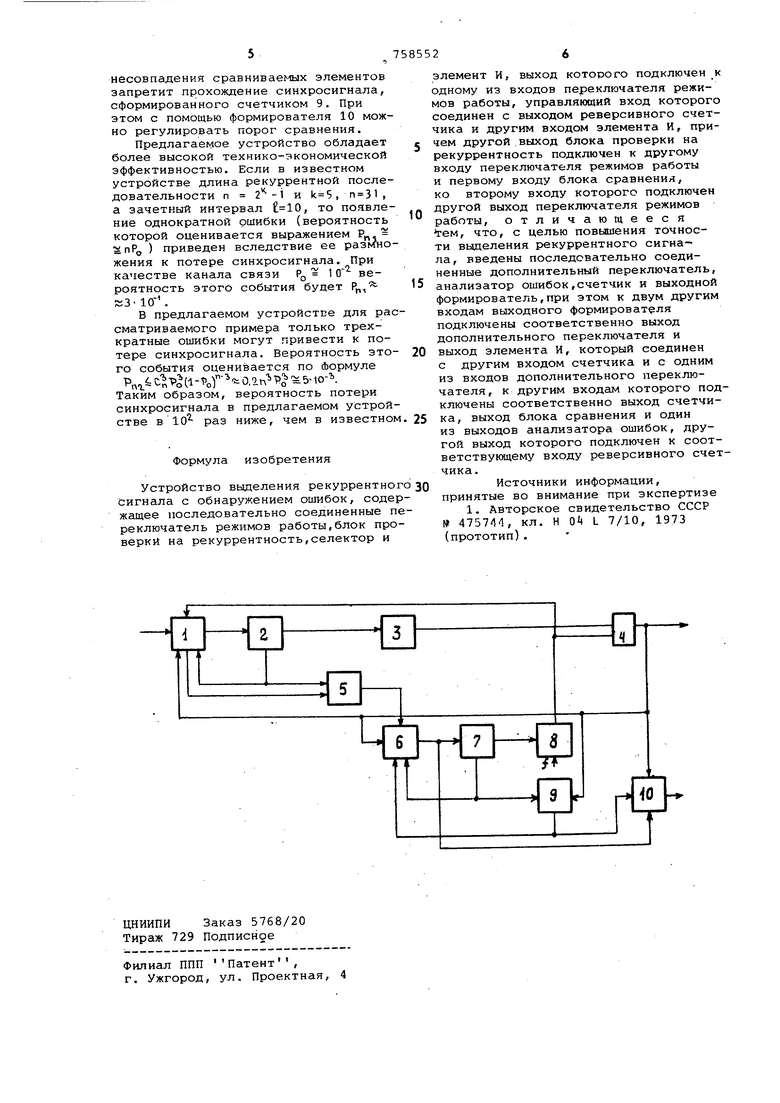

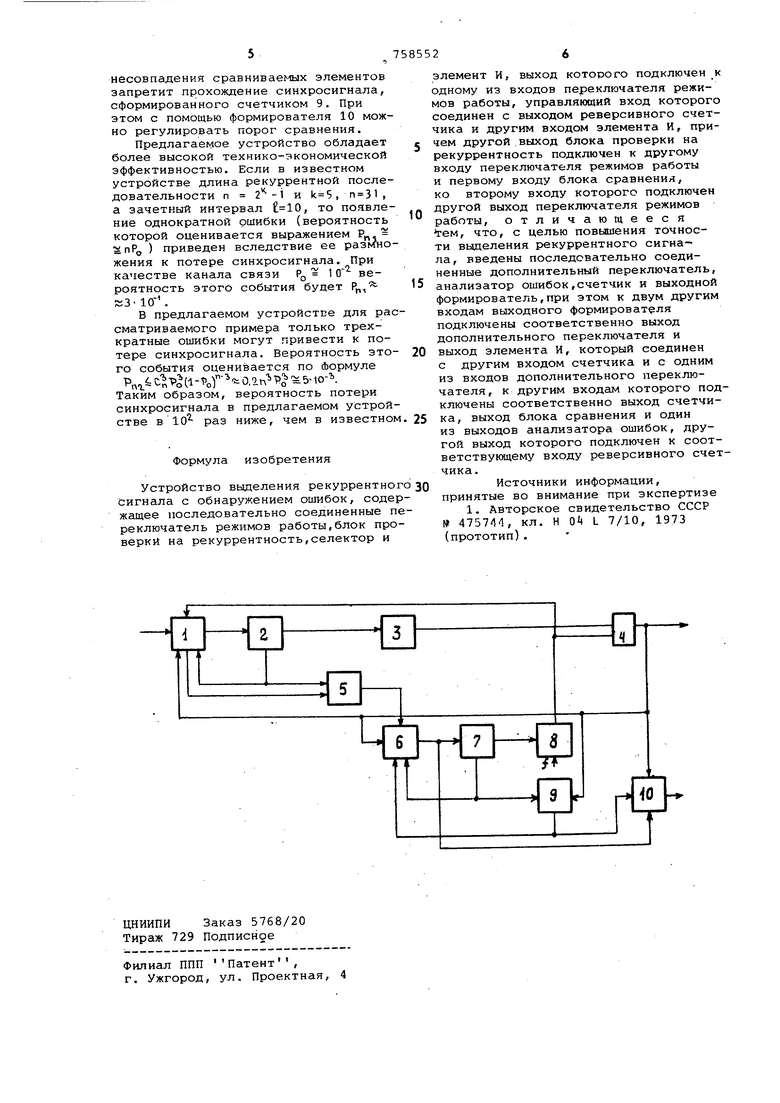

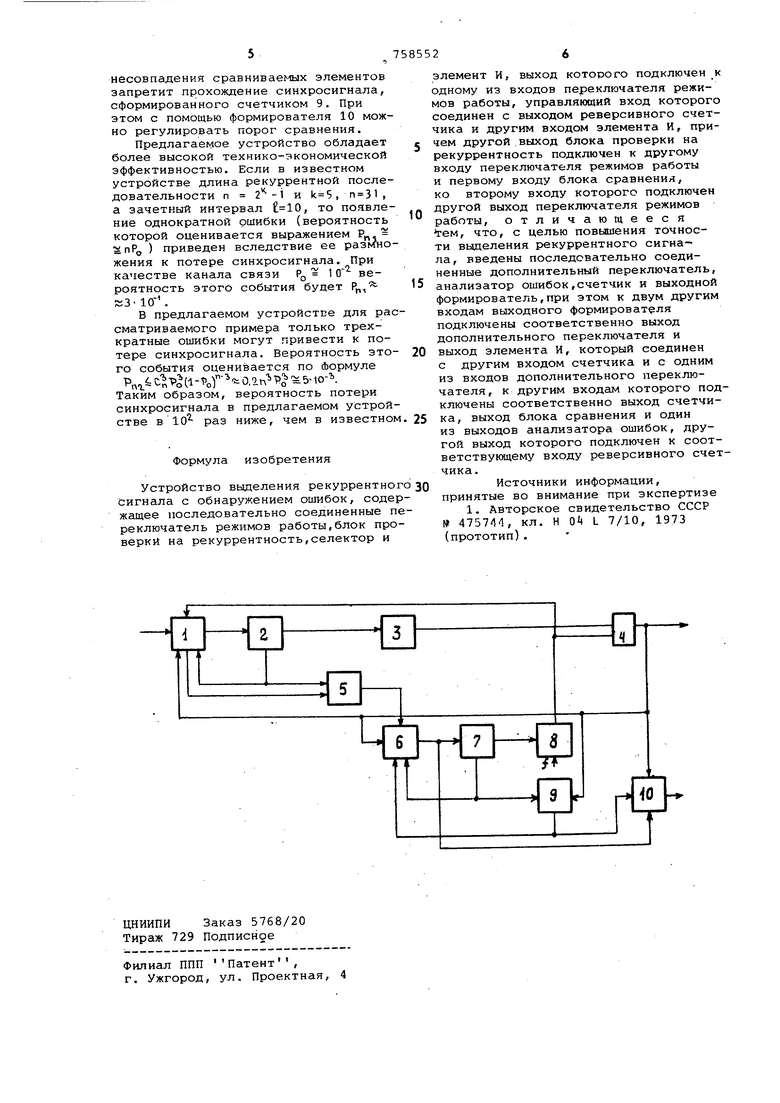

соединенные переключатель режимов , работы, блок проверки и рекуррентность, селектор и элемент И, выход которого подключен к одному из входов переключателя режимов работы, управляющий вход которого соединен с выходом реверсивного счетчика и другим входом элемента И, причем выход блока проверки на рекуррентность подключен к другому входу переключателя режимов работы и первому входу блока сравнения, к второму входу которого подключен другой выход переключателя режимов работы, введены последовательно соединенные дополнительный переключатель, анализатор ошибок, счетчик и выходной формирователь, при этом к двум другим входам вЪкюдного формирователя подключены соответственно выход дополнительного переключателя и выход элемента И, который соединен с другим входом счетчика и с одним из входов дополнительного переключателя, к другим входам которого подключены соответственно выход счетчика, выход блока сравнения и один из выходов анализатора ошибок, другой выход которого подключен к соответствующему входу реверсивного счетчика. На чертеже представлена структу ная электрическая схема предлагаем го устройства. Устройство содержит переключате 1 режимов работы, блок 2 проверки рекуррентность, селектор 3, элемен 4, блок 5 сравнения, дополнительны переключатель-б, анализатор 7 ошиб реверсивный счетчик 8, счетчик 9 и выходной формирователь 10. Устройство работает следующим образом. Принимаемая последовательность двоичных символов через переключат 1 поступает в блок 2 проверки на р куррентность, в этом блоке, содерж регистр сдвига на к-разрядрв с то ами съема на сумматоры по модулю д (в соответствии с многочленом Р{х) принимаемые символы проверяются на соответствие закону рекуррентного к да. Так, например, для Р{х) х + X + 1 уравнение проверки имеет вид i V5® где Xj- - принимаемые из канала связи элементы последовательности; © - сложение по модулю два. Результаты проверки формируются в блоке 5 сравнения и подсчитываются реверсивным счетчиком 8. Поскольку одиночный ошибочный элемент, проходя по к-значному регистру сдвига блока 2, образует на выходе блока 5 сравнения к-разрядную последовательность из едини и нулей (причем вес этой последова тельности ), то нецелесообразно, чтобы каждая единица сбрасывала счетчик 8 на к-тактов. Поэтому реверсивный счетчик 8 сбрасывается только первой единицей появившейся, на выходе блока 5. А с помощью анализатора 7 продолжается дальнейший анализ к-разрядного интервала рекуррентной последовательное ти. Если анализатор 7 определит, что последовательность, образованная на выходе блока 5, по своей кон фигурации соответствует одиночной ошибке, то реверса счетчика 8 боль ше не происходит. Это обуславливае ся отсутствием необходимости исключать из анализа рекуррентной последовательности интервал, превышающий к-разрядов, поскольку ошибочный эле мент, обеспечивший реверс счетчика на к-тактов, успеет выйти из регист ра блока 2 до того, как счетчик 8 отсчитает сброшенные к-разрядов. Если анализатор 7 определит наличие пакета ошибки на интервале к-разряд то на св.оем втором выходе выдает си нал, который одновременно закроет переключатель б, включит в работу счетчик 9 и обеспечит реверс счетчи ка 8 еще на V тактов (где V 0 ,1, 2 Величина V выбирается из условий обеспечения требуемой достоверности выделения синхросигнала. Дополнительный реверс счетчика 8 обусловлен тем, что последний искаженный элемент пакета ошибки не успеет выйти из регистра блока 2 проверки на рекурректность до того, как счетчик отсчитает k тактов, прибавленные ранее. Блокировка выхода блока 5 необходима для исключения нежелательного воздействия последнего искаженного разряда пакета на анализатор 7, поскольку каждый оишбочный элемент последовательности влечет размножение ошибок на выходе блока 5. Дальнейший анализ продолжается по сигналу переполнения счетчика 9 (емкость счетчика равна к), который подключает выход блока 5 ко входу анализатора 7 ошибок. Таким образом, анализатор 7 продолжит анализ рекуррентной последовательности после того, как последний искаженный знак пакета ошибки выйдет из регистра блока 2 проверки на рекуррентность. По окончании зачетного участка рекуррентной последовательности происходит срабатывание счетчика 9. В этом случае импульс переполнения счетчика 9, воздействуя на переключатель 1, отключает поступление элементов синхросигнала из канала связи и переводит регистр сдвига блока 2 в автономное генерирование рекуррентной последовательности. Селектор 3, подключенный к блоку 2 проверки на рекуррентность, при достижении селектируемой k-значной комбинации, через элемент И 4 выдает фазирующий сигнал. Этот сигнал возвращает устройство в исходное состояние, размыкая цепь обратной связи блока 2 через переключатель 1 режимов работы и сбрасывая счетчик 8 до нуля. Для уменьшения ложной синхронизации в устройстве производится дополнительная проверка на точность выделения синхросигнала. Это осуществляется путем поэлементного сравнения на блоке 5 генерируемых блоком 2 двоичных знаков с последними k-разрядами рекуррентной последовательности, поступающей из канала связи. Поэтому для определения начала сравнения селектор 3 настраивается не на последнюю k-значную комбинацию рекуррентной последовательности, а на комбинацию, следуемую на k-разрядов раньше (предыдущую). Сигнал с селектора 3 через элемент И включает счетчик 9 (в данном случае он определяет конец вьщеления синхросигнала) , а блок 5 сравнения соединяет со входом -устройства. Результат сравнения поступает на вход выходного формирователя 10, который в случае

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1976 |

|

SU604173A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1983 |

|

SU1102050A2 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1988 |

|

SU1518905A2 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство для выделения рекуррентного синхросигнала с обнаружением ошибок | 1986 |

|

SU1363510A1 |

| Устройство для выделения рекуррентного синхросигнала | 1976 |

|

SU576672A1 |

| Устройство для выделения рекуррентного синхросигнала | 1973 |

|

SU492041A1 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1973 |

|

SU475744A1 |

Авторы

Даты

1980-08-23—Публикация

1978-08-03—Подача