лителя, выход которого является аналоговым выходом логарифма отношения входных сигналов устройства, выход

каждой схемы сравнения соединен с входом управления режимом работы соответствующего интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Устройство для асинхронного управления вентильным преобразователем | 1991 |

|

SU1786621A1 |

| Адаптивный нейроноподобный элемент | 1982 |

|

SU1103259A1 |

| Пирометр спектрального отношения | 1976 |

|

SU646204A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Логарифмический преобразователь отношения сигналов | 1978 |

|

SU723602A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| СПОСОБ И УСТРОЙСТВО АНАЛОГОВОГО ВЫДЕЛЕНИЯ И НАКОПЛЕНИЯ ИМПУЛЬСНЫХ СИГНАЛОВ | 2001 |

|

RU2212111C2 |

| Аналоговый частотомер | 1980 |

|

SU943595A1 |

УСТРОЙСТВО ДЛЯ ЛОГАРИФМИЧЕСКОЙ ОБРАБОТКИ ДВУХ СИГНАЛОВ, содержащее первый и второй ключи, информационные входы которых являются входами устройства, а выходы соединены с входами соответствующих зарядно-разрядных RC-цепей, третий и четвертый ключи, информа1щонный вход каждого из которых соединен с выходом соответствующей зарядно-разрядной iiC-цепи, две схемы сравнения, первые входы которых соединены с выходом источника опорного напряжения, соединенные последовательно элемент И, счетчик и блок цифровой индикации, генератор счетных импульсов, выход которого соединен с первым входом элемента И и с входом генератора тактовых импульсов, прямой выход которого подключен к управляющим входам первого и второго ключей, а его инверсный выход подключен к управляющим входам третьего и четвертого ключей, отличающееся тем, что, с целью повьш1ения точности, помехоустойчивости и расширения функциональньк возможностей путем формирования как логарифмов отношения двух сигналов, так и логарифмов самих сигналов, а также логарифмов их степеней, в него введены два интегратора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, регулируемый источник напряжения, два запоминающих блока, два элемента Ш1И-НЕ, дополнительный элемент И и суммирующий усилитель, причем входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами схем сравнения, а его выход подключен к второму входу элемента И, вторые входы схем сравнения соединены соответственно с выходами третьего и четвертого ключей, вход источника регулируемого напряжения подключен к выходу источника опорного напряжения, соединенному с вхо- j дами задания начальных условий интега раторов, информационные входы которых соединены с выходом регулируемого источника напряжения, прямой выход генератора тактовых импульсов подключен к входам управления заданием начальных условий интеграторов и к первым входам элементов ИЛИ-НЕ, второй вхпд каждого из которых соединен ее ю ел с выходом соответствующей схемы сравнения, а их выходы подключены к входам дополнительного элемента И, выход которого соединен с управляющими входами запоминающих блоков, вход каждого из которых соединен с выходом соответствующего интегратора, выход первого запоминающего блока является аналоговьпу выходом логарифма первого входного сигнала устройства и соединен с неинвертирующим входом суммирующего усилителя, выход второго запоминающего блока является аналоговым выходом логарифма второго входного сигнала устройства и соединен с инвертирующим входом суммирующего уси

1

Изобретение относится к измерителной и вычислительной технике и может быть использовано, например, в цветовой пирометрии.

Известны аналоговые устройства, содержащие в цепи отрицательной обратной связи нелинейный активный логарифмирующий элемент, выполненный н биполярном транзисторе С

Недостатками данных устройств являются низкая точность, неустойчивость, самовозбуждение.

Наиболее близким по техническому решению к предлагаемому является устройство, содержащее первый и второй ключи, информационные входы которых являются входами устройства, а выходы соединены с входами соответст вующих зарядно-разрядных RC-цепей, третий и четвертьй ключи, информационный вход каждого из которых соединен с выходом соответствующей зарядно-ра рядной RC-цепи, две схемы сравнения, первые входы которых соединены с выходом источника опорного напряжения, соединенные последовательно элемент И, счетчик и блок цифровой индикации, генератор счетных импульсов, выход которого соединен с первым входом элемента И и с входом генератора тактовых импульсов, прямой выход которого подключен к управляющим входам первого и второго ключей, а его инверсный выход подключен к управляющим входам третьего и четвертого ключей C2J.

Недостатком такого устройства является низкая точность перекрестного режима работы схем сравнения первого и второго каналов, что приводит также к ухудшению помехоустойчивости устройства и возможности ложных срабатываний. Выходная информация имеет только цифровой вид и не отражает логарифмов собственно входных сигналов что необходимо при применении устройства в пирометрии.

Целью изобретения является повышение точности, помехоустойчивости и расширение функциональных возможностей устройства путем формирования как 5 логарифмов отношения двух сигналов, так и логарифмов самих сигналов J а также логарифмов их степеней.

Поставленная цель достигается тем, что в устройство для логарифмической

o обработки двух сигналов, содержащее первый и второй ключи, информационные входы которых являются входами устройства, а выходы соединены с входами соответствующих зарядно-разрядных RC5 цепей, третий и четвертый ключи, информационный вход каждого из которых соединен.с выходом соответствующей зарядно-разрядной RC-цепи, две схемы сравнения, первые входы которых сое0 динены с выходом источника опорного напряжения, соединенные последовательно элемент И, счетчик и блок цифровой индикации, генератор счетных импульсов, выход которого соединен с первым

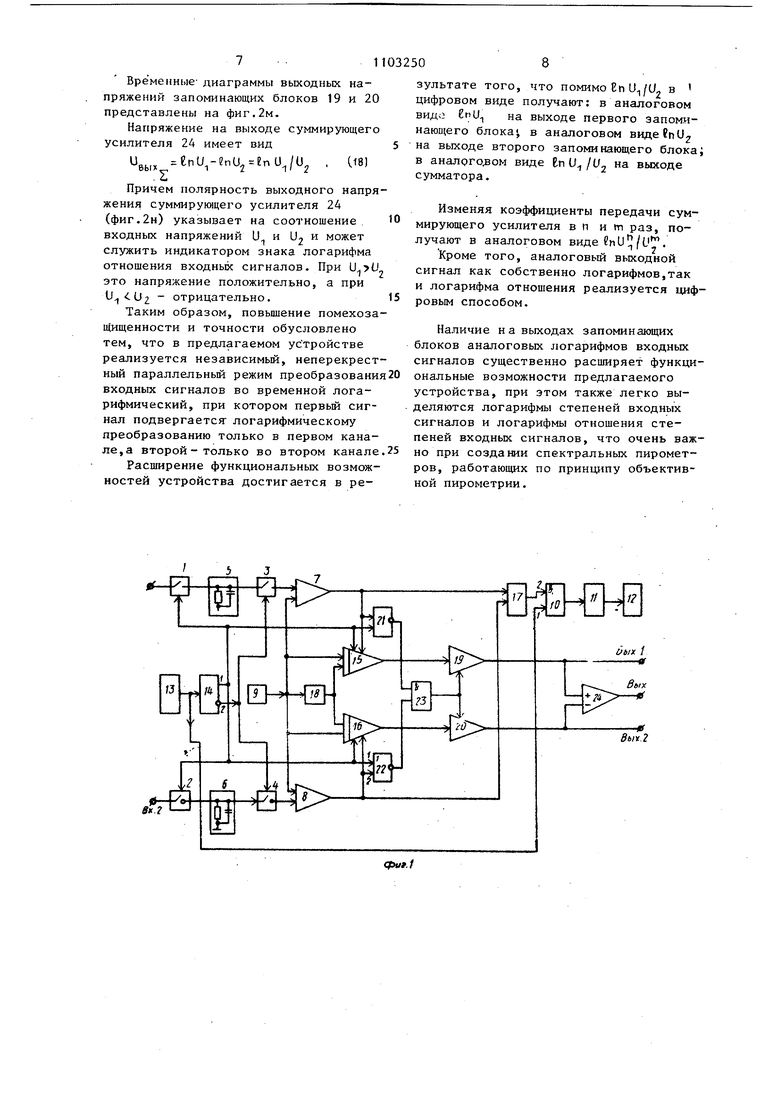

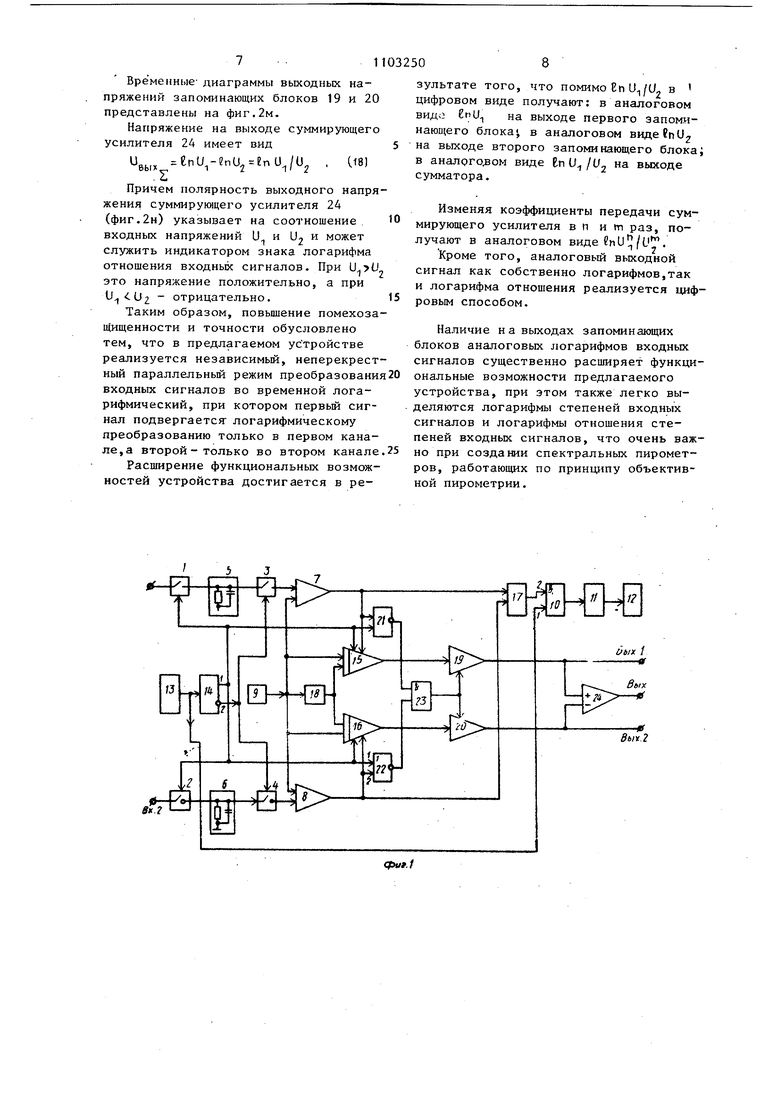

) входом элемента И и с входом генератора тактовых импульсов, прямой выход которого подключен к управляющим входам первого и второго ключей, а его инверсный выход подключен к управляющим входам третьего и четвертого ключей, введеш два интегратора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, регулируемый источник напряжения, два запоминающих блока, два элемента .ИЛИ-НЕ, дополнительный элемент И и суммирукнций усилитель, причем входы элемента ИСКЛЮЧАЩЕЕ ИЛИ соединены с выходами схем сравнения, а его выход подключен к второму входу элемента И, вторые входы схем сравнения соединены соответственно с выходами третьего и четвертого ключей, вход источника регулируемого напряжения подключен к выходу источника опорного напряжения, соединенному с входами задания начальных условий интеграторов, информационные входы которых соединены с выходом регулируемого источника напряжения, прямой выход генератора тактовых им. пульсов подключен к входам управления заданием начальных условий интеграторов и к первым входам элементов ИЛИ-НЕ, второй вход каждого из которых соединен с выходом соответствующей схемы сравнения, а их выходы подключены к входам дополнительного элемента И, выход которого соединен с управляющими входами запоминающих .блоков, вход каждого из которых соединен с. выходом соответствующего интегратора, выход первого запоминающе го блока является аналоговым выходом логарифма первого входного сигнала устройства и соединен с неинвертирую щим входом суммирующего усилителя, выход второго запоминающего блока яв ляется аналоговым выходом логарифма .второго входного сигнала устройства и соединен с инвертирующим входом суммирующего усилителя, выход которого яв ляется аналоговым выходом.логарифма от ношения входных сигналов устройства,вы ход каждой схемы сравнения соединен с входом управления режимом работы соответствующего интегратора. На фиг.1 представлена блок-схема устройства для логарифмической обработки двух сигналов; на фиг.2 - диаг раммы, поясняющие работу устройства. Предлагаемое устройство содержит. четыре ключа 1-4, две зарядно-разряд ные RC-цепи 5 и 6, две схемы сравнения 7 ii 8, источник 9 опорного напряжения, элемент И 10, счетчик 11, блок 12 цифровой индикации, генерато 13 счетных импульсов, генератор 14 тактовьк импульсов, два интегратора 15 и 16, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17, регулируемый источник напряжения 18, два запоминающих блока 19 и 20, два элемента ИЛИ-НЕ 2.1 и 22, дополнитель ньш элемент И 23, суммирующий усили тель 24. Предлагаемое устройство работает следующим образом. В первом полуцикле замыкаются ключи 1 и 2, при этом зарядно-разряд ные RC-цепи 5 и 6 заряжаются до входных напряжений ,2 (Фиг.2а,в). Во втором полуцикле ключи 1 и 2 размыкаются, а ключи 3 и 4 замыкаются, подключая зарядно-разрядные RC-цепи 5 и 6 к входам схем сравнения 7 и 8 (фиг.25). Начинается разряд зарядно1504 разрядных RC-цепей, напряжения них имеют вид: .,e.p( (,,) где время с начала второго по луцикла; .S..V параметры соответствующих зарядно-разрядных RC-цеВ момент времени t срабатывает схема сравнения 8 второго канала (рассмотрен случай, когда ,фиг.-2д). В момент времени i срабатывает ма сравнения 7 первого канала (фиг.2г). Длительности временных интервалов на выходах соответственно первой и второй схем сравнения: .Te.uju . опорное напряжение на выходе источника 9 опорного напряжения. На выходе элемента 17 ИСКЛЮЧАЮЩЕЕ ИЛИ длительность интервала 4t равна (фиг.2е). S« / 0- 2 2/ oЕсли Т., -С- , то t tnUjU2 (6) В счетчике 11 записывается число forenUJU f - частота импульсов генератора где 13 счетных импульсов. Это число N отображается в блоке 12 цифровой индикации, причем при 0-I/ 2 Выделение аналоговых напряжений, пропорциональных логарифмам напряжений входных сигналов, производится с помощью интеграторов 15 и 16, запоминающих блоков 19 и 20, элементов 21, 22 и 23 управления запоминаюЕцими блоками и суммирующего усилителя 24 следующим образом. Интеграторы 15 и 16, являясь идентичными, могут быть реализованы по-разному. В предлагаемом устройстве входы задания начальных условий интеграторов 15 и 16 подключены к выходу источника 9 опорного напряжения, напряжение которого равно (Jo з входы управления заданием начальных условий интеграторов подключены к прямому вы ходу генератора 14 тактовых импульсов. Следовательно, в первом полутак те происходит задание начальных уело ВИЙ интеграторов, и напряжение на вы ходе интеграторов принимает вид R. ВЫХ R Мин Входы управления режимом работы и теграторов подключены к выходам соот ветствующих схем сравнения 7 и 8. Следовательно, режим интегрирования производится за время -t или 2 , пропорциональное логарифму соответст вующего входного сигнала (фиг.2г,д) В момент прекращения интегрирования перехода интегратора в режим хранени напряжение на выходе первого интегра тора с учетом выражений (5) и (6) равн 2ин ,.(2) Ъ ВЫх ин о R I 1мн , 2ин,л2) о R вх о V 0 MH-HH Соответственно, напряжение на вых де второго интегратора равно 2V1H (2) + OR вх.... 1ИН Из анализа выражений (10) и (11) следует, что при выполнении условий ) «,Лн Чн - постоянная времени зарядно разрядных RC-цепей 5-6; напряжение на информационн входах интеграторов (на вы ходе регулируемого источни ка напряжения 18). Напряжение на выходе первого интегр тора принимает вид

ивых,,

(1)

для второго интег(151

,

(6)

а на выходе второго запоминающего блока 20 соответственно

07) Условие (12) выполняется при подборе номиналов соответствующих элементов интеграторов и при настройке предлагаемого устройства, а условие (13) - в процессе настройки всего устройства регулированием коэффициента передачи регулируемого источника напряжения 18, который представляет собой, например, неинвертирующий уси.литель, к входу которого приложено напряжение U , а коэффициент передачи определяется из выражения (13). Временные диаграммы, поясняющие работу первого и второго интеграторов, приведены на фиг.2 ж и з соответственно. Причем на .2 отображены два случая: в первом такте входное напряжение первого канала больше, а во втором такте меньше входного напряжения второго канала. Запоминающие блоки 19 и 20 являются идентичными . В предлагаемом устройстве (фиг.1) информационньй вход запоминающих блоков 19 и 20 подключен к выходу соответствующего интегратора 15 или 16, а входы управления подключены к -выходу элемента И 23. Элемент ИЛИ-НЕ 21 первого, канала вырабатывает на своем выходе импульс (фиг.2и), длительность и фаза которого соответствуют режиму хранения первым интегратором 15 напряжения, величина которого определяется из выражения (14) . Аналогично выходной импульс второго элемента ИЛИ-НЕ 22 (фиг.2к) соответствует режиму хранения вторым интегратором 16 напряжения (15). Элемент И 23 представляет собой схему совпадения, которая выделяет импульс соответствующий наименьшему времени хранения интеграторами 15 и 16 (фиг.2л), поступающий на входы управления запоминающих блоков 19 и 20. Это обеспечивает синхронную- работу запоминающих блоков, что является необходимым в случае изменения по амплитуде входных напряжений Напряжение на выходе первого, запоминающего блока 19 имеет вид 7 . 1 Временные- диаграммы выходных напряжений запоминающих блоков 19 и 20 представлены на фиг.2м. Напряжение на выходе суммирующего усилителя 24 имеет вид и„.,. enU..-EnUjU. , (.18) 6b,, Причем полярность выходного напря жения суммирующего усилителя 24 (фиг.2н) указывает на соотношение входных напряжений U. и U2 и может служить индикатором знака логарифма отношения входных сигналов. При это напряжение положительно, а при ( - отрицательно. Таким образом, повьшение помехоза щищенности и точности обусловлено тем, что в предлагаемом устройстве реализуется независимый, неперекрест ный параллельньй режим преобразовани входных сигналов во временной логарифмический, при котором первый сигнал подвергается логарифмическому преобразованию только в первом канале, а второй - только во втором канале Расширение функциональных возможностей устройства достигается в ре5J 0 зультате того, что помимо En в цифровом виде получают: в аналоговом видо €r)U на выходе первого запоминающего блока, в аналоговом видеРпО на выходе второго запоминающего блока; в аналоговом виде tn на выходе сумматора. Изменяя коэффициенты передачи суммирующего усилителя впит раз, получают в аналоговом виде . Кроме того, аналоговый вькодной сигнал как собственно логарифмов,так и логарифма отношения реализуется цифровым способом. Наличие на выходах запоминающих блоков аналоговых логарифмов входных сигналов существенно расширяет функциональные возможности предлагаемого устройства, при этом также легко выделяются логарифмы степеней входных сигналов и логарифмы отношения степеней входных сигналов, что очень важно при создании спектральных пирометров, работающих по принципу объективной пирометрии.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексеенко А.Г | |||

| и др | |||

| Приме-нение прецизионных ИС | |||

| М., -Радио и связь, 1981, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Зубов Б.Г | |||

| и Кнышев А.П | |||

| Логарифмический аналого-цифровой преобра-зователь отношения двух сигналов | |||

| Отбор и передача информации, 1979, № 57, с.76 (прототип) | |||

Авторы

Даты

1984-07-15—Публикация

1983-02-28—Подача