(5) АНАЛОГОВОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Оптикоэлектронный координатор для автоматического вождения мобильных агрегатов | 1986 |

|

SU1378086A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

1

Изобретение относится к аналоговой вычислительной технике и может быть использовано в устройствах автоматики, измерительной и вычислительной техники.

Известно аналоговое запоминаюи ее устройство по авт. ев, № 799013, которое содержит накопитель, входы которого подключены к выходам блока выборки адресов, блок поочередной выдачи кодов адресов, первые входы которого соединены с ин(1юрмационными шинами устройства, второй вход блока поочередной выдачи кодов адресов подключен к шине управления и к одному из входов генератора тактовых импульсов, первый выход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из входов блока выборки адресов, другие входы которого соединены с выходами блока поочеред ной выдачи кодов адресов, четыре

элемента стробирования, причем один из входов первого элемента стробирования соединен со вторым выходом генератора тактовых импульсов, суммирующий усилитель, выход которого соединен с ойходом устройства, нульорган, фиксатор уровня, ключи, интегрирующие усилители (интеграторы), переключатели, при этом одни из

fg входов второго и третьего элементов стробирования соединены с выходом накопителя и через первый переключатель - с одним из входов первого и четвертого элементов стробирова15 ния, другие входы элементов стробирования соединены с третьими выходами генератора тактовых импульсов, выходы элементов стробирования соединены с одним из входов интеграторов,

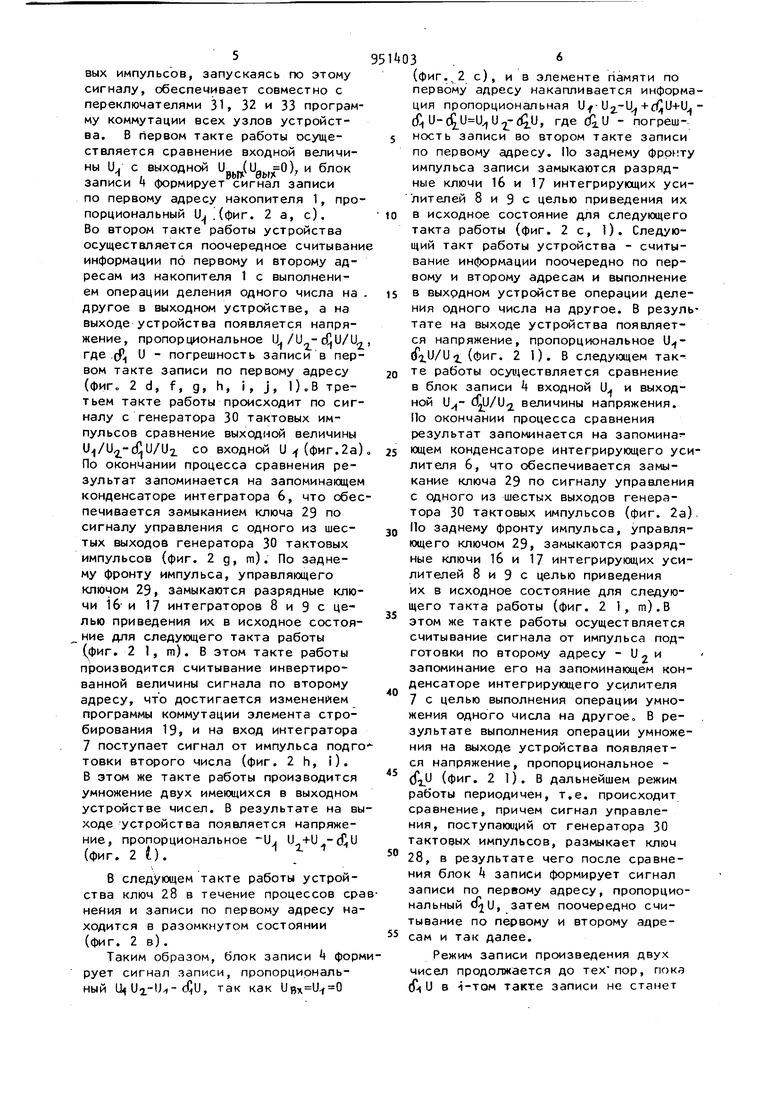

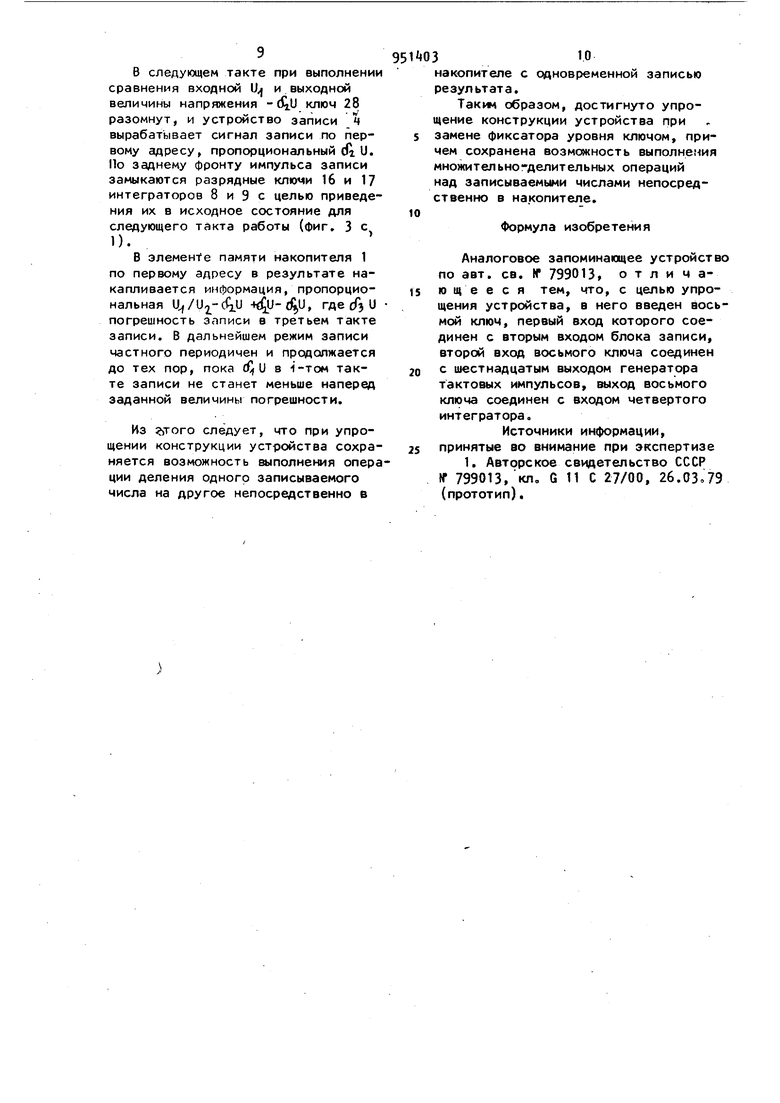

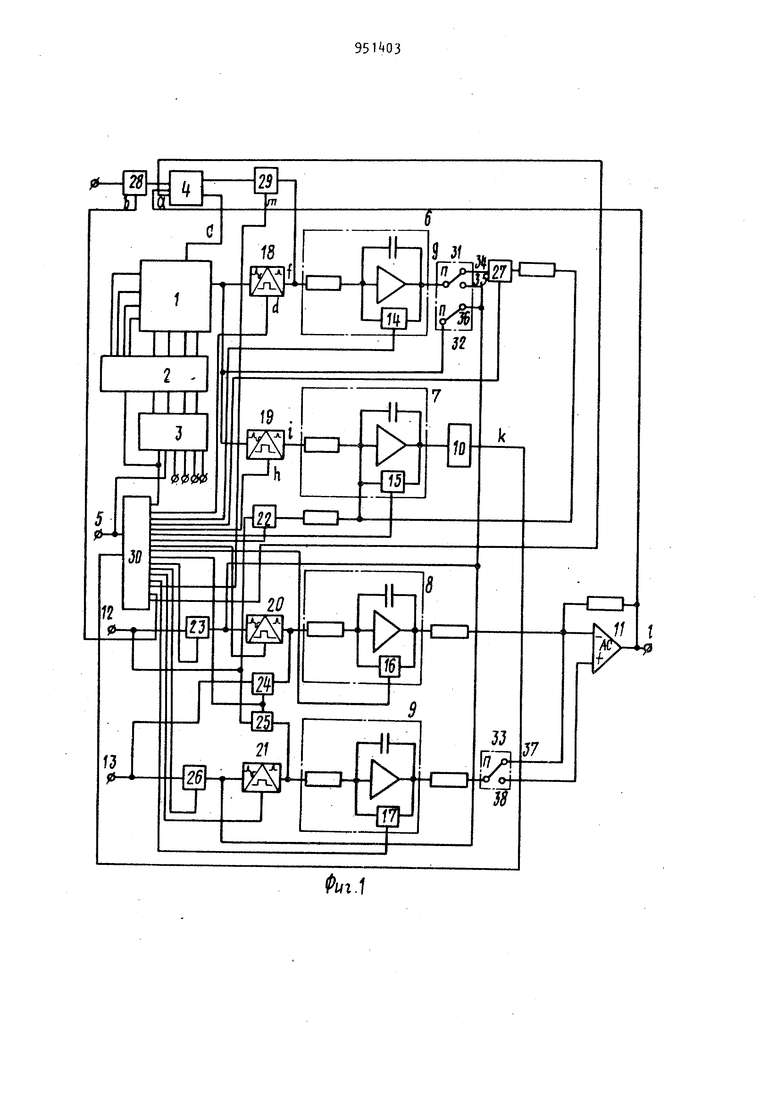

20 другие входы которых подключены к четвертым выходам генератора тактовых импульсов, выход первого интегратора через второй переключатель соединен со входами суммирующего 39 усилителя и выходом второго интегра тора, выход третьего интегратора со динен через нуль-орган со вторым входом генератора тактовых импульсов, выход четвертого интегратора ч рез третий переключатель соединен с одним из входов первого ключа, выход которого соединен с третьим входом третьего интегратора и выходом второго ключа, вход второго клю ча соединен со входом третьего и четвертого ключей и шиной, напряжения первого операнда, входы пятого и ше сторого ключей соединены с шиной напряжения второго операнда, выходы третьего и шестого ключей соответственно подсоединены к выходам первого и четвертого элементов стробирования, выходы четвертого и пятого ключей соединены со входами первого и четвертого, элементов стробирования управляюсцие входы ключей, с первого по шестой включительно, соединены с пятыми выходами генератора тактовых импульсов, при этом первый вход фиксатора уровня соединен с выходом устройства, выход фиксатора уровня соединен с первым входом устройства записи, второй вход которого соединен с выходом устройства, причем первый вход седьмого ключа является аналогичным входом устройстваj а вы ход его подключен к первому входу устройства записи и входу шестого и тегратора, управляющие же входы фик сатора уровня, устройства записи и седьмого ключа соединены с шестыми выходами генератора тактовых импуль сов соответственно. Накопитель данного устройства может быть реализован как на аналог вых элементах памяти замкнутой стру туры, так и на аналоговых элементах памяти разомкнутой структуры. Принцип считывания при этом не меняется 1. Недостатком данного устройства является усложненность конструкции, требующая для выполнения множительно-делительных операций над записываемыми числами наличия фиксатора уровня. Цель изобретения - упрощение конструкции устройства. Поставленная цель достигается тем что в известное аналоговое запоминающее устройство введен восьмой ключ, первый вход которого соединен со вторым входом блока записи. второй вход восьмого ключа соединен с шестнадцатым выходом генератора тактовых импульсов, выход восьмого ключа соединен со входом четвертого интегратора. На фиГо 1 изображена функциональная схема устройства; на фиг. 2,3 временные диаграммы, поясняющие работу устройства в режимах умножения одного записываемого числа на , другое с записью произведения в накопитель и деления одного записываемого числа на другое с записью частного в накопитель соответственно. Предлагаемое устройство содержит накопитель 1, блок 2 выбора адреса, блок 3 поочередной выдачи кодов адресов, блок записи, шину 5 управления, интеграторы 6, 7, 8 и 9, нуль-орган 10, суммирующий усилитель 11, шины 12 и 13 напряжений первого и второго операндов, разрядные ключи Tt, 15, 16 и 17, входящие в интеграторы, элементы стробирования 18, 19, 20 и 21, ключи 22-29, генератор 30 тактовых импульсов, переключатели 31, 32 и 33, контакты переключателей 31, 32 и 33. Устройство (.фиг, ) работает следующим образом. Режим записи одного числа задается положением переключателей 31, 32, 33 и сигналом задания операции на шине 5 управления генератора 30 тактовых импульсов. Принцип записи аналогичен известному принципу записи в элементы памяти с замкнутой структурой. В этом режиме работы ключ 28 постоянно замкнут, а ключ 29 разомкнут. Процесс считывания записываемого в накопитель 1 числа также аналогичен уже известному, за исключением коммутации разрядными ключами 16 и 17 запоминающих конденсаторов интегрирующих усилителей 8, 9 по заднему фрон ту импульса записи, с целью подготовки выходного устройства к следующему такту считывания. Сравнение входной и выходной величин в блок k записи и запись разности в накопитель 1 происходят по сигналам управления, формируемым генератором 30 тактовых импульсов. В режиме умножения одного записываемого числа на другое, находящееся в накопителе (фиг. 2), на шину 5 управления поступает сигнал задания операции Генератор 30 такто5вых импульсов, запускаясь по этому сигналу, обеспечивает совместно с переключателями 31, 32 и 33 программу коммутации всех узлов устройства, В первом такте работы осуществляется сравнение входной величины Uj с выходной U.), и блок Itjblf tУD17 записи ч формирует сигнал записи по первому адресу накопителя 1, пропорциональный Ui .(фиг. 2 а, с). Во втором такте работы устройства осуществляется поочередное считывани информации по первому и второму адресам из накопителя 1 с выполнением операции деления одного числа на другое в выходном устройстве, а на выходе устройства появляется напряжение, пропорциональное Ц./U -dJU/U где .(fl, и - погрешность записи в первом такте записи по первому адресу (фиг. 2 d, f, g, h, i, j, 1),B третьем такте работы происходит по сигналу с генератора 30 тактовых импульсов сравнение выходной величины U /U -cfjU/Ui со входной (фиг.2a По окончании процесса сравнения результат запоминается на запоминающем конденсаторе интегратора 6, что обес печивается замыканием ключа 29 по сигналу управления с одного из шестых выходов генератора 30 тактовых импульсов (фиг. 2 g, m). По заднему фронту импульса, управляющего ключом 29, замыкаются разрядные ключи 16 и 17 интеграторов 8 и 9 с целью приведения их в исходное состояние для следующего такта работы (фиг. 2 1, т). В этом такте работы п| оизводится считывание инвертированной величины сигнала по второму адресу, что достигается изменением программы коммутации элемента стробирования 19 и на вход интегратора 7поступает сигнал от импульса подг товки второго числа (фиг. 2 h, i), 8этом же такте работы производится умножение двух имеющихся в выходном устройстве чисел. В результате на в ходе устройства появляется напряжение, пропорциональное U, U +U (фиг. 2 ().1X1 В следующем такте работы устройства ключ 28 в течение процессов ср нения и записи по первому адресу на ходится в разомкнутом состоянии (фиг. 2 в). Таким образом, блок записи фор рует сигнал записи, пропорциональный Щиг-и - и, так как З . (фиг., 2 с), и в элементе памяти по первому адресу накапливается информация пропорциональная .-LU+f U+U d; и- и .- 4U, где dl и - погрешность записи во втором такте записи по первому адресу. По заднему импульса записи замыкаются разрядные ключи 16 и 17 интегрирующих усилителей 8 и 9 с целью приведения их в исходное состояние для следующего такта работы (фиг. 2с, 1). Следующий такт работы устройства - считывание информации поочередно по первому и второму адресам и выполнение в выхрдном устройстве операции деления одного числа на другое. В результате на выходе устройства появляется напряжение, пропорциональное (фиг. 2 1). В следующем такте работы осуществляется сравнение в блок записи Ц входной U и выходной величины напряжения. По окончании процесса сравнения результат запоминается на запоминав ющем конденсаторе интегрирующего усилителя 6, что обеспечивается замыкание ключа 29 по сигналу управления с одного из шестых выходов генератора 30 тактовых импульсов (фиг. 2а). По заднему фронту импульса, управляющего ключом 29, замыкаются разрядные ключи 16 и 17 интегрирующих усилителей 8 и 9 с целью приведения их в исходное состояние для следующего такта работы (фиг. 2 1, т).В этом же такте работы осуществляется считывание сигнала от импульса подготовки по второму адресу - U 2 и запоминание его на запоминающем конденсаторе интегрирующего усилителя 7 с целью выполнения операции умножения одного числа на другое В результате выполнения операции умножения на выходе устройства появляется напряжение, пропорциональное (f, (фиг. 2 1). В дальнейшем режим работы периодичен, т.е. происходит сравнение, причем сигнал управления, поступающий от генератора 30 тактовых импульсов, размыкает ключ 28, в результате чего после сравнения блок Ц записи формирует сигнал записи по первому адресу, пропорциональный и, затем поочередно считывание по первому и второму адресам и так далее. Режим записи произведения двух чисел продолжается до техпор, пока (f, и в i-TQM такте записи не станет

79

меньше наперед заданный величины погрешности.

Таким образом, при упрощении конструкции устройства, оказывается возможным осуществление операции умножения одного записываемого ла на другое непосредственно в накопителе одновременно с записью результата.

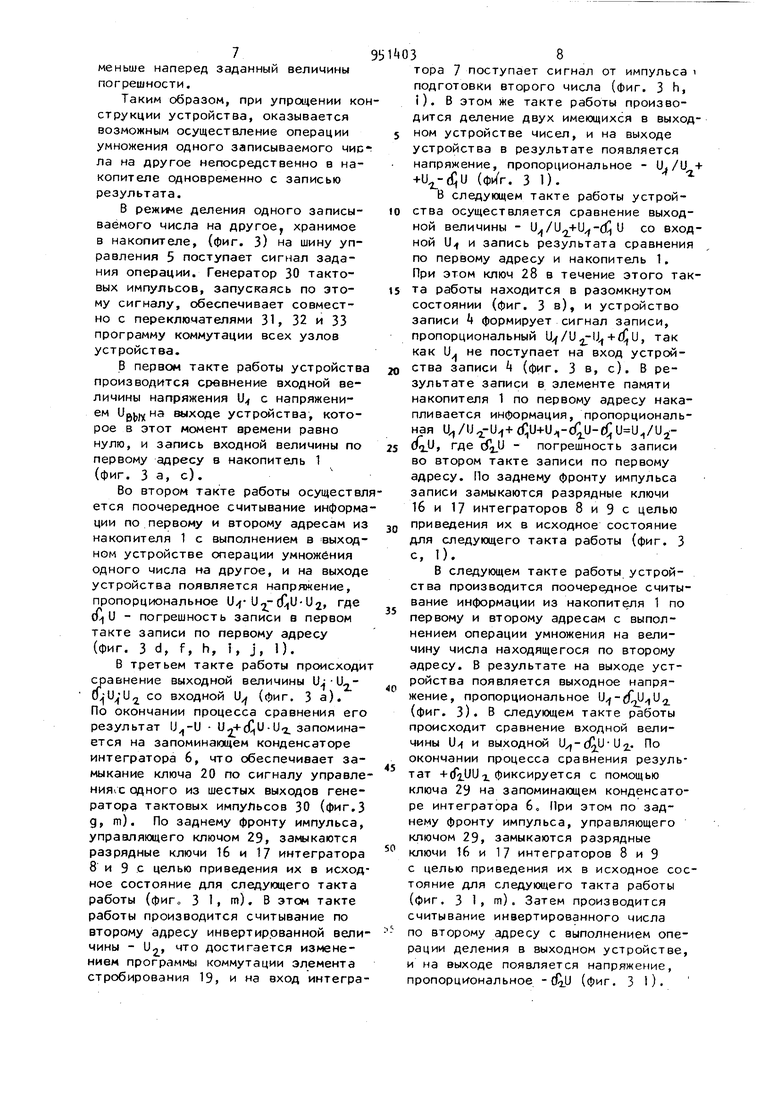

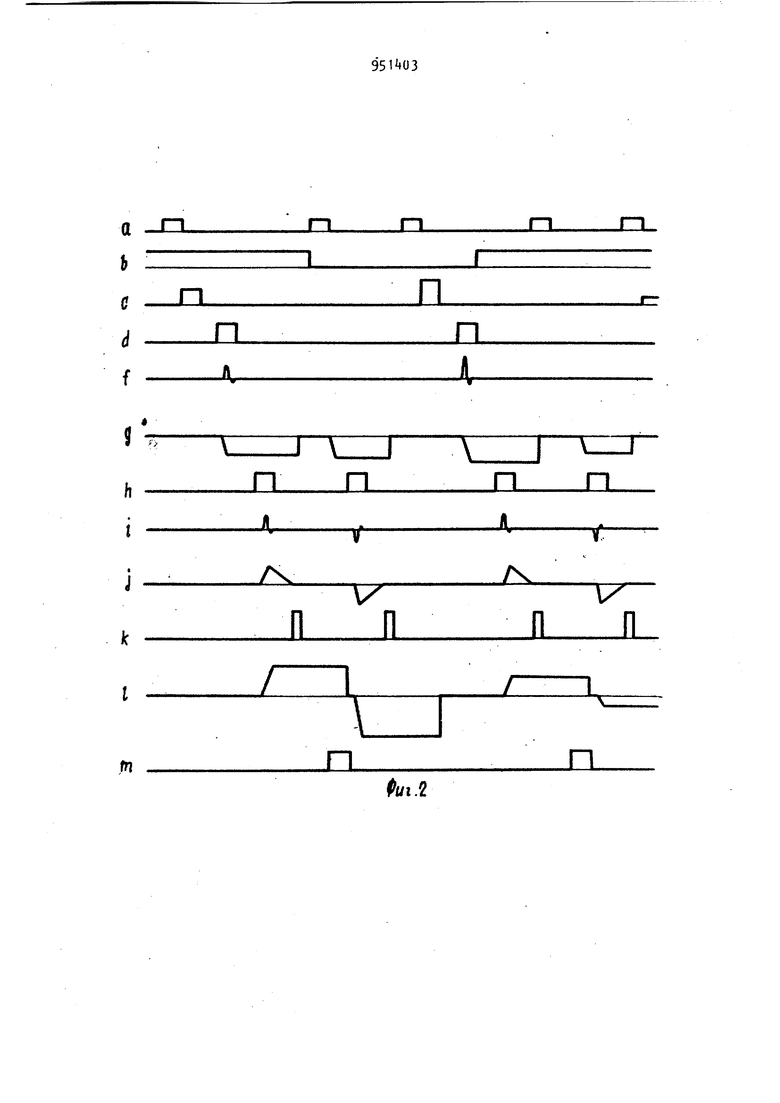

В режиме деления одного записываемого числа на другое, хранимое в накопителе, (фиг. 3) на шину управления 5 поступает сигнал задания операции. Генератор 30 тактовых импульсов, запускаясь по этому сигналу, обеспечивает совместно с переключателями 31, 32 и 33 программу коммутации всех узлов устройства.

В первом такте работы устройства производится сравнение входной величины напряжения U с напряжением Ugjjjy на выходе устройства, которое в этот момент времени равно нулю, и запись входной величины по первому адресу в накопитель 1 (фиг. 3 а, с).

Во втором такте работы осуществлется поочередное считывание информации по первому и второму адресам из накопителя 1 с выполнением в выходном устройстве операции умножения одного числа на другое, и на выходе устройства появляется напряжение, пропорциональное U2-cC(U-U2, где сС| и - погрешность записи в первом такте записи по первому адресу (фиг. 3 d, f, h, i, J, 1).

В третьем такте работы происходи сравнение выходной величины U U-C jU U со входной и (фиг. 3 а). По окончании процесса сравнения его результат . запоминается на запоминающем конденсаторе интегратора 6, что обеспечивает замыкание ключа 20 по сигналу управлеНИЯ1С одного из шестых выходов генератора тактовых импульсов 30 (фиг.З д, т). По заднему фронту импульса, управляющего ключом 29, заг мкаются разрядные ключи 16 и 17 интегратора 8 и 9с целью приведения их в исходное состояние для следующего такта работы (фиго 3 1, fn). В этом такте работы производится считывание по второму адресу инвертированной величины - Uj,, что достигается изменением программы коммутации элемента стробирования 19, и на вход интеграОЗ8

тора 7 поступает сигнал от импульса подготовки второго числа (фиг. 3 h, i). В этом же такте работы производится деление двух имеющихся в выход5 ном устройстве чисел, и на выходе устройства в результате появляется напряжение, пропорциональное - IL/U +

+u, (. 31).

в следующем такте работы устройства осуществляется сравнение выходной величины - и со входной и и запись результата сравнения по первому адресу и накопитель 1. При этом ключ 28 в течение этого так5 та работы находится в разомкнутом состоянии (фиг. 3 в), и устройство записи 4 формирует сигнал записи, пропорциональный + dJu, так как и, не поступает на вход устроио ства записи k (фиг. 3 в, с). В результате записи в элементе памяти накопителя 1 по первому адресу накапливается информация, пропорциональная u,/u -u +d;u+u -c u-c(;u u /U25 i.f ffl® 1. погрешность записи во втором такте записи по первому адресу. По заднему фронту импульса записи замыкаются разрядные ключи 16 и 17 интеграторов 8 и 9 с целью

д приведения их в исходное состояние для следующего такта работы (фиг. 3 с, 1).

В следующем такте работы устройства производится поочередное считывание информации из накопителя 1 по первому и второму адресам с выполнением операции умножения на величину числа находящегося по второму адресу. В результате на выходе устройства появляется выходное напряжение, пропорциональное U -rfjJ U. (фиг. 3). В следующем такте работы происходит сравнение входной величины а и выходной Uxj-(UU2.- По окончании процесса сравнения резуль тат +(fiUtJx фиксируется с помощью ключа 29 на запоминающем конденсаторе интегратора 6, При этом по заднему фронту импульса, управляющего ключом 29, замыкаются разрядные

ключи 16 и 17 интеграторов 8 и 9

с целью приведения их в исходное состояние для следующего такта работы (фиг. 3 1, гп) . Затем производится считывание инвертированного числа

- по второму адресу с выполнением операции деления в выходном устройстве, и на выходе появляется напряжение, пропорциональное - (фиг. 31). в следующем такте при выполнении сравнения входной U и выходной величины напряжения - di.U ключ 28 разомнут, и устройство записи Ч вырабатывает сигнал записи по первому адресу, пропорциональный di U. По заднему фронту импульса записи замыкаются разрядные ключи 16 и 17 интеграторов 8 и 9 с целью приведения их в исходное состояние для следующего такта работы (фиг, 3 с в элeмeнte памяти накопителя 1 по первому адресу в результате накапливается информация, пропорциональная )-( -K), где сГз U погрешность записи в третьем такте записи. В дальнейшем режим записи частного периодичен и продолжается до тех пор, пока d U в I-TOM такте записи не станет меньше наперед заданной величины погрешности. Из того следует, что при упрощении конструкции устройства сохраняется возможность выполнения опера ции деления одного записываемого числа на другое непосредственно в 10 накопителе с одновременной записью результата. Таким образом, достигнуто упроение конструкции устройства при замене фиксатора уровня ключом, причем сохранена возможность выполнения ножительно-делительных операций над записываемыми числами непосредтвенно в накопителе. Формула изобретения Аналоговое запоминающее устройство по авт. св. If 799013, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, в него введен восьмой ключ, первый вход которого соединен с вторым входом блока записи, второй вход восьмого ключа соединен с шестнадцатым выходом генератора тактовых импульсов, выход восьмого ключа соединен с входом четвертого интегратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР « 799013, кл, G 11 С 27/00, 2б.03о79 (прототип).

ri

n

J V.

n

yv V n П / I

П

n

n

n

n

TV П fui.2 П i.,

n

n

/

V

Д

П

m

Й/I.J

ГТ

Г1

/

1/

Д

n

Авторы

Даты

1982-08-15—Публикация

1979-05-25—Подача