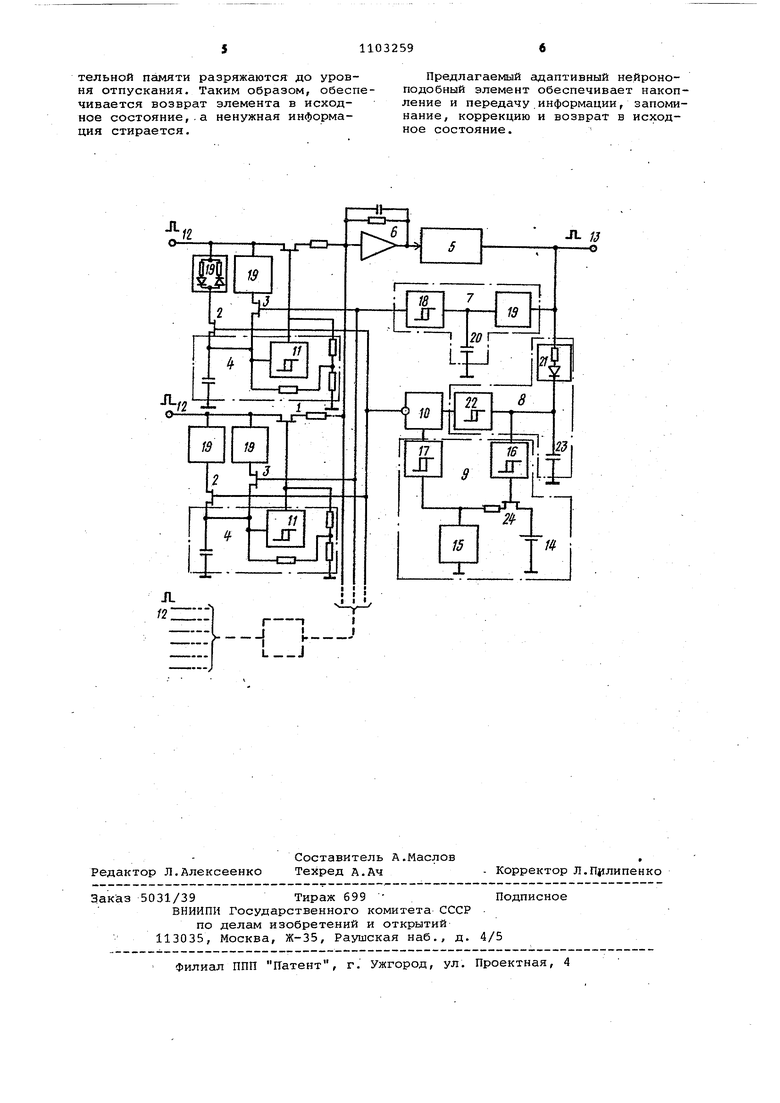

Изобретение относится к адаптив ным нейроноподобным элементам, может быть использовано в робототехнике и кибернетике в качестве базо вого элемента при создании адаптив ных и самообучающихся сетевых управляющих систем. Известно нейроноподобное устрой ство .содержащее блоки синаптическо проводимости, блоки пространственн временного суммирования и блок ада тации порога нейрона l . Такое устройство относительно сложно и не обеспечивает корректир ки синаптической проводимости посл обучения. Наиболее близким к изобретению является нейроноподобный элемент, содержащий входные интеграторы, вы ходы которых через управляемые входные ключи подключены к входам суммирующего интеграторами выходно преобразователь напряжения в часто ту 2 . Однако такой элемент не обеспечивает возможности корректировки состояния входных ключей и, как следствие, имеет недостаточно высо кую точность. Цель изобретения - повьяиение то ности работы элемента. Поставленная цель достигается тем, что нейроноподобный элемент, содержащий входные ключи, информац онные входы которых являются соответствующими входами элемента, а и формационные выходы подключены к входам суммирующего интегратора, входные интеграторы по числу входов элемента и преобразователь напряже ния в частоту, выход которого является выходом элемента, содержит ин тегратор коррекции, интегратор крат ковременной памяти, интегратор дли.тельной памяти, элемент ИЛИ, заряд;но-разрядные цепи, выполненные в ви де параллельно включенных .диоднореэйстивных цепочек, состоящих из последовательно соединенных резисто ров и встречно направленных диодов а также ключи входной памяти и ключи коррекции по числу входов элемента, подключенные информационными входами через соответствующие зарядно-разрядные цепи к соответств ющим входам элемента, а информационными выходами - к входам соответствующих входны х интеграторов, выходы которых подсоединены к управляющим входам входных ключей, входы интеграторов коррекции и кратковре менной памяти соединены с выходом преобразователя напряжения в частот информационный вход которого подклю чен к выходу суммирующего интеграто ра, выход интегратора коррекции под соединен к управляющим входам ключей коррекции, а первый выход интегратора кратковременной памяти и выход интегратора длительной памяти подключены к соответствующим входам элемента ИЛИ, выход которого соединен с управляющими входами ключей входной памяти, информационный вход интегратора длительной-памяти подключен к второму выходу интегратора кратковременной памяти. Интегратор коррекции содержит элемент аналоговой памяти, -зарядноразрядную цепь и триггер, выход которого является выходом интегратора, а вход соединен с входом элемента аналоговой памяти и через зарядноразрядную цепь подключен к входу ин-тегратора. Интегратор кратковременной памяти содержит элемент аналоговой памяти, зарядную цепь, выполненную в виде последовательно соединенных резистора и диода, и триггер, выход которого является первым выходом интегратора, а вход соединен с входом элемента аналоговой памяти, с вторым выходом интегратора и через зарядную цепь с его входом. Интегратор длительной памяти содержит элемент памяти, первый и второй триггеры, источник напряжения и ключ, вход которого подключен к источнику напряжения, управляющий, вход подключен к выходу первого триггера, а выход соединен с входом элемента памяти и входом второго триггера, выход которого является выходом интегратора, вход первого триггера является входом интегратора. На чертеже приведена схема адаптивного нейроноподобного элемента. Элемент содержит входные ключи 1, ключи 2 входной памяти, ключи 3.коррекции, входные интеграторы 4, пре-, образователь 5 напряжения в частоту, суммирующий интегратор 6, интегратор 7 коррекции, интегратор 8 кратковременной памяти, интегратор 9 длительной памяти, элемент ИЛИ 10, триггер 11 входных интеграторов 4, входы 12,, выход 13, источник 14 напряжения, элемент 15 памяти (длительной и триггеры 16 и 17 интегратора 9 длительной памяти, триггер 18, зарядно-разрядную цепь 19 и элемент 20 аналоговой памяти интегратора 7 коррекции, зарядную цепь 21, триггер 22 и элемент 23 аналоговой памяти (кpaткoвpeмeнJ oй) интегратора в кратковременной памяти, ключ 24 интегратора 9 длительной памяти. Адаптивный нейроноподобный элемент работает следующим образом. , В исходном состоянии элемента ключи 1, 3 и 24 находятся в непроводящем состоянии, ключи 2 - в проводящем состоянии. На выходах всех

триггеров 11, 16, 17, 18 и 22 низкий уровень, т.е. логический ноль.

Зарядно-разрядная цепь 19 интегратора 7 коррекции обеспечивает заряд до уровня срабатывания триггера 18 за 2-3 самых редких импульса и разряд до уровня отпускания - за 2-3 периода между ними.

Зарядная цепь 21 обеспечивает заряд элемента 23 памяти за 10-20 редких импульсов до уровня срабатывания триггера 22 и за -50-100 - до уровня срабатывания триггера 16. Время разряда элемента 23 памяти определяется токами утечки и на несколько порядков больше времени заряда.

Входные зарядно-разрядные цепи 19 обеспечивают заряд элементов памяти входных интеграторов 4 за 10-20 редких импульсов до уровня срабатывания триггеров 11 и разряд до уровня отпускания - за 10-20 периодов между ними.

Зарядно-разрядные цепи 19 обеспечивают заряд и разряд элементов памяти через ключи 3 за время в 1020 раз больше, чем через ключи 2.

Триггеры 11, 17 и 16 срабатывают, т.е. выдают сигнал логической единицы, при уровне входного, сигнала примерно 0,8 уровня единицы, а сбрасываются, т.е. выдают сигнал логического нуля, при уровне сигнала ниже логического нуля.

Триггер 22 срабатывает при достижении 0,5 уровня логической единицы. Отпускание происходит подобно отпусканию триггеров 11. Преобразователь 5 напряжения в частоту имеет зону нечувствительности, а в оставшейся части рабочего диапазона вырабатывает импульсы с частотой, пропорциональной сигналу управления.

Входы 12 элемента.обычно подключены к выходам таких же элементов, поэтому на них подаются импульсные сигналы в диапазоне частот (0,35+ +1,00)F-M постоянной длительности и амплитуды. Между собойвходные импульсы не синхронизированы.

В зависимости от назначения элемента резисторы на входах суммирующего интегратора 6 подбираются таким образом, чтобы сигналы проходили через элемент при наличии сигналов хотя бы на одном, двух или большинстве входов.

Импульсы, поступающие на выходы 12, вызывают рост напряжения на накопителях входных интеграторов 4 до тех пор, пока не сработают триггеры 11 и не. переведут ключи 1 в проводящее состояние.

Импульсы с входов 12 поступают через ключи 1 на входы суммирующего

интегратора 6, на его выходе вырабатывается напряжение, которое обуславливает появление импульсов некоторой частоты на выходе 13. Эта частота зависит от количества и частоты входных сигналов. После снятия сигналов на входах 12 сигналы на выходе 13 через время задержки также исчезают.

Появление сигналов на выходе 13 вызывают рост напряжения на элементах 20 и 23 памяти. В том случае, если время генерирования сигналов на выходе 13 было достаточно длительным, что является признаком прохождения через элемент потока рабочей информации, то срабатывает прежде всего триггер 22, который через элемент ИЛИ 10 переводит ключи 2 в непроводящее состояние, чем обеспечивает запоминание состояния входов элемента по крайней мере на время разряда элемента 23 памяти. ,

Те входы 12 элемента, на которых не было достаточно интенсивных сигналов, остаются отключенными от входов суммирующего интегратора 6, а элементы памяти соответствугадих входных интеграторов 4 остаются незаряженными.

Триггеры 11 после включения с помощью собственных цепочек резисторов, поддерживающих напряжение выше уровня отпускания, становятся на самоблокировку.

Однако в дальнейшем, при передаче через элемент, находящийся в состоянии памяти, некоторой информации возможна незначительная коррекция состояния входов.

Это происходит в том случае, если в режиме памяти почти через все включенные входы проходят сигналы.

При этом срабатывает триггер 18 и переводит ключи 3 в проводящее состояние. Если оказалось, что при перйичном запоминании один-два входа были включены или не включены неправильно, то через соответствующие зарядно-разрядные цепи 19 обеспечивается возможность откорректировать эту ошибку, но для этого нужно уже значительно больше времени.

В том случае, если через элемент передаются сигналы настолько долго, что срабатывает триггер 16 интегратора 9 длительной памяти, то с помощью ключа 24 к источнику 14 напряжения . подключается элемент 15 длительной памяти. В результате обеспечивается весьма длительное запоминание рабочего состояния элемента.

Однако при длительном неиспользовании элемента в рабочих каналах передачи информации, что свидетельствует о ненадобнодти созданной цепи и. элемент 23 кратковременной памяти и,|В конце концов, элемент 15 длительной памяти разряжаются до уровня отпускания. Таким образом, обеспечивается возврат элемента в исходное состояние,.а ненужная информация стирается.

Предлагаемый адаптивный нейроноподобный элемент обеспечивает накопление и передачу информации, запоминание, коррекцию и возврат в исходное состояние.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников | 1987 |

|

SU1571793A1 |

| Устройство для логарифмической обработки двух сигналов | 1983 |

|

SU1103250A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ СВЧ-ИЗЛУЧЕНИЙ | 1993 |

|

RU2040005C1 |

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

| Преобразователь временных интервалов | 1988 |

|

SU1525914A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Датчик разности фаз | 1980 |

|

SU962817A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1027818A1 |

| Устройство преобразования сигналаМОСТОВОгО дАТчиКА B чАСТОТу | 1979 |

|

SU839049A1 |

1. АДАПТИВНЫЙ НЕЙРОНОПОДОБНЫЙ ЭЛЕМЕНТ, содержащий входные ключи, информационные входы которых являются соответствующими входами элемента, а информационные выходы подключены к входам суммирующего интегратора, входные интеграторы по числу входов элемента и преобразователь напряжения в частоту, выход которого является выходом элемента, отличающийся тем, что, с целью повьшения точности работы элемента, он содержит интегратор коррекции, интегратор кратковременной памяти, интегратор длительной памяти, элемент ИЛИ, зарядно-разрядные цепи, выполненные в виде параллельно включенных диодно-резистивных цепочек, состоящих из последовательно соединенных, резисторов и встречнонаправленных диодов, а также ключи входной памяти и ключи коррекции по числу входов элемента, подключенные информационными входами через соответствующие зарядно-раэрядные цепи к соответствующим.входам элемента, а информационными выходами к входам соответствуквдих входных интеграторов, выходы которых подсоединены к управляющим входам входных ключей, входы интеграторов коррекции и кратковременной памяти соединены с выходом преобразователя напряжения в частоту, информационный вход которого подключен к выходу суммирующего интегратора, выход ийтегратора коррекции подсоединен к управляющим входам ключей коррекци, а первый выход интегратора кратковременной памяти и выход интегратора длительнойпамяти подключены к соответствующим входам элемента ИЛИ, выход которого соединен с управляющими входами ключей входной памяти, информационный вход интегратора длительной памяти подключен к второму выходу интегратора кратковременной . памяти. 2.Элемент по п.1, отличающий с я тем, что в нем интегра.тор коррекции содержит блемент аналоговой памяти, зарядно-разрядную цепь и триггер, выход которого является выходом интегратора, а вход соединен с входом элемента аналоговой памяти и через зарядно-разрядную С .цепь подклЕочен к входу интегратора. 3.Элемент по п. 1, о т л и ч а ю щ и и с я тем, что в нем интегратор кратковременной памяти содержит элемент аналоговой памяти, зарядную цепь, выполненную в виде последовательно соединенных резистора и диода, и триггер, выход которого является первым выходом интегратора, а вход соединен с входом элемента аналоговой памяти, с вторым выходом интегратора и через зарядную цепь с его входом. 4.Элемент поп.1, отличаю щ и и с я тем, что в нем интегратор длительной памяти содержит элемент памяти, первый и второй триггеры, источник напряжения и ключ, вход которого подключен к источнику напряжения, управляющий вход подключен к выходу первого триггера, а выход соединен с входом элемента памяти и входом второго триггера, выход которого является выходом интегратора, вход первого-триггера является входом интегра ора.

L

12

I

11 JT

23

16 JT

It

;.:

SI

12

{1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для моделирования нейтрона | 1976 |

|

SU647699A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| МОДЕЛЬ НЕЙРОНА | 0 |

|

SU283700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1982-04-05—Подача