Изобретение относится к автоматике и вычислительной технике и может быть использовано в формирователях управляющих токов (токов продвижения) в запоминающих устройствах на цилиндрических магнитных доменах (ЦМД ЗУ).

Известны многочисленные технические решения генерации и формирования периодических электрических сигналов различной формы, в том числе и синусоидальных, жестко привязанных по времени к импульсам задающих генераторов или сигналам внешней синхронизации.

Однако в этих устройствах не достигает: ся высокая точность формы и симметрия генерируемых сигналов.

Наиболее близким по технической сущности к предлагаемому является генератор

треугольных напряжений, содержащий источник тактовых импульсов, М-разрядный двоичный счетчик импульсов и функциональный преобразователь код - напряжение. В этом генераторе формирование выходного сигнала осуществляется путем преобразования цифрового кода состояний двоичного реверсивного N-разрядного счетчика в пропорциональное ему электрическое напряжение. Особенность генератора заключается в том, что в нем в первом цикле формирования выходных сигналов реверсивный счетчик работаете режиме суммирования последовательно проходя состояния от нулевого до максимального, равного (2N - 1), а во втором цикле - в режиме вычитания, последовательно проходя все состояния первого цикла, но в обратvi ю ел ю ел ел

ном направлении, в результате чего выходное напряжение второго цикла является зеркальным отображением выходного напряжения первого цикла, а следовательно, напряжение первого и второго циклов сим- метричны относительно осей, проходящих через середины участков их максимальных и минимальных значений.

Однако этот генератор не обеспечивает строгой симметрии положительных и отри- цательных полуволн выходных сигналов вследствие того, что центрально-симметричные (относительно точек их пересечения с осью времени ) участки-ступеньки этих сигналов формируются по взаимно инвер- тируемым уровням двоичных сигналов всех разрядов реверсивного счетчика, разброс значений которых, особенно их верхних уровней, в типовых логических элементах, составляет значительную величину. Так, на- пример, участки выходного напряжения с минимальным значением формируются по низким (нулевым) уровням сигналов всех разрядов реверсивного счетчика, в то время как симметричные им участки с максималь- ным значением формируются по высоким (единичным)уровням, и поэтому отклонение как верхних, так и нижних уровней сигналов любого из разрядов счетчика от их номиналов неизбежно приводит к искажению сим- метрии положительных и отрицательных полуволн выходных сигналов генератора.

Кроме того, известный генератор имеет ряд недостатков, ограничивающих его широкое применение, таких как формирование напряжения только ступенчато-треугольной формы; невозможность формирования от одного реверсивного счетчика двух, взаимно ортогональных (с фазовым, сдвигом на 90°) выходных сигналов.

Цель изобретения - повышение точности формы генерируемых сигналов путем повышения симметрии их положительных и отрицательных полуволн и повышения сте- пени ортогональности двух фаз генерируемых сигналов для использования их в запоминающих устройствах доменной памяти.

Указанная цель достигается тем, что в устройство, содержащее задающий генератор импульсов, двоичный счетчик импульсов и преобразователь код-напряжение, дополнительно введены соединенные соответствующим образом реверсивный сдвиго- вый регистр, второй преобразователь код-напряжение, два коммутатора, два разностных интегратора, инвертор, блок инверторов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре элемента И.

В предлагаемом генераторе за один пе- чриод выходного сигнала формируются два периодических сигнала, один из которых используется как положительная полуволна первичного напряжения, а зеркально-инвертированный сигнал - как отрицательная полуволна напряжения.

В разностном интеграторе произведено преобразование ступенчатого напряжения в кусочно-ломаное выходное напряжение генератора.

Введение в устройство реверсивного сдвигового регистра позволяет генерировать сигналы квазисинусоидальной формы.

Введение в устройство инверторов, преобразователя код-напряжение, коммутаторов и разностных интеграторов обеспе- чивает формирование второй фазы выходного сигнала, ортогональной сигналам первой фазы.

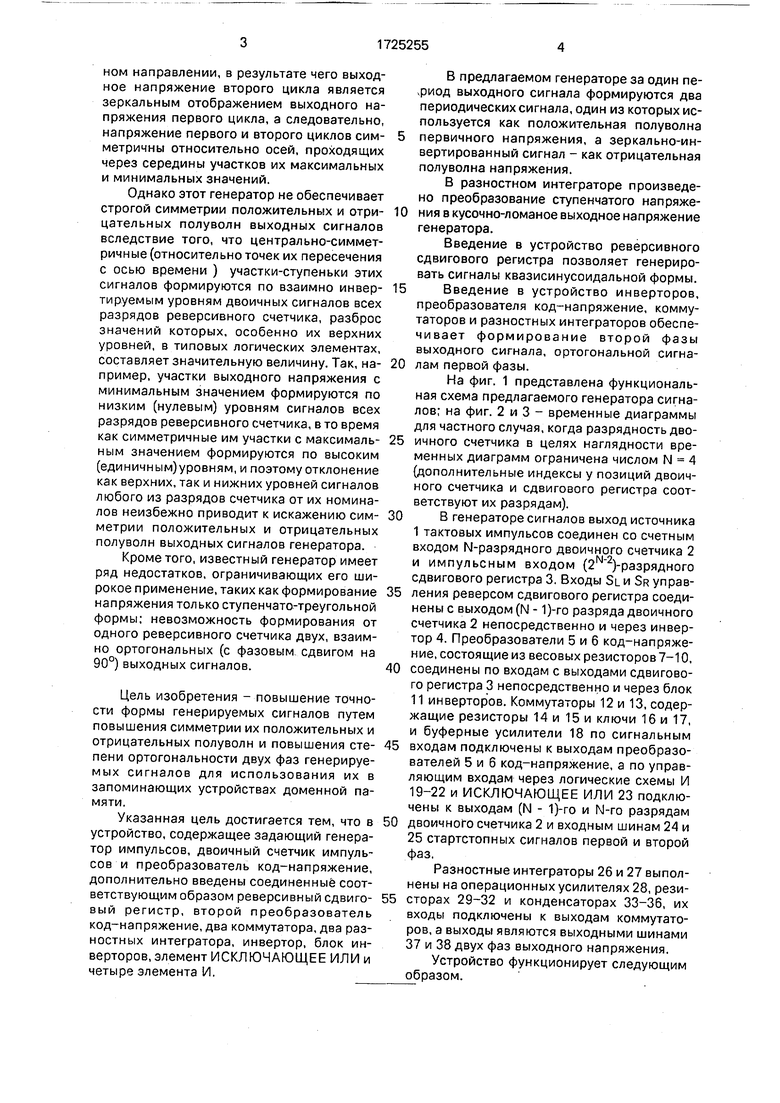

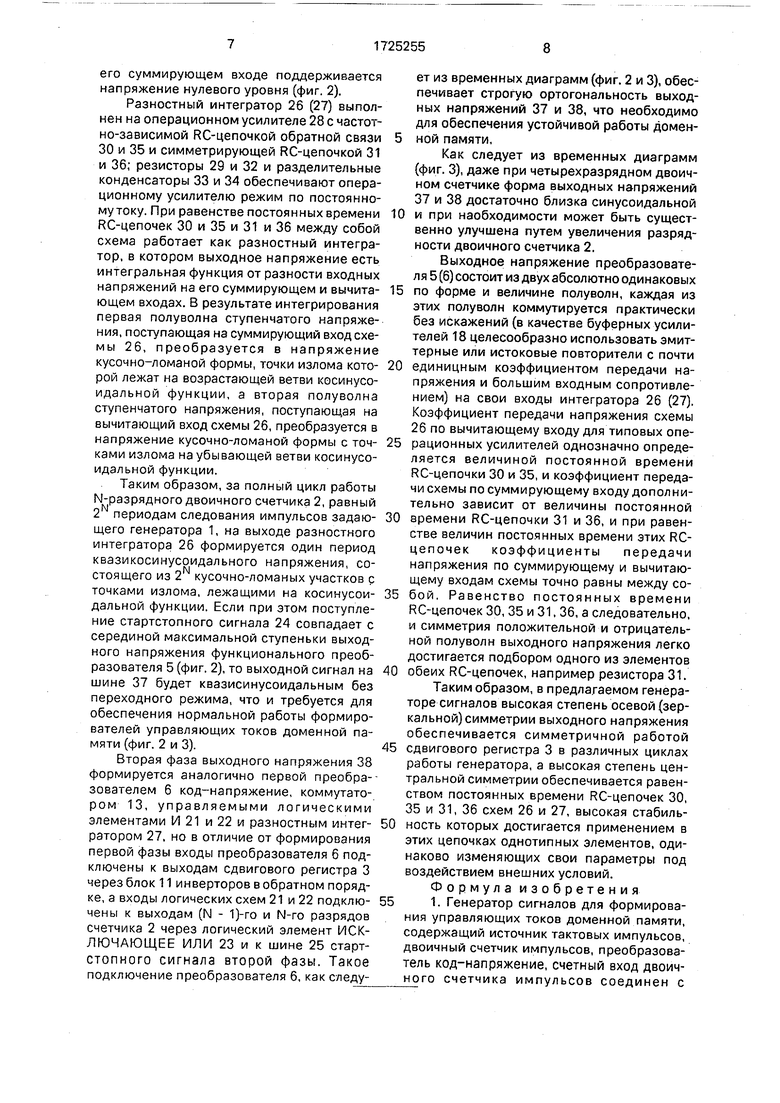

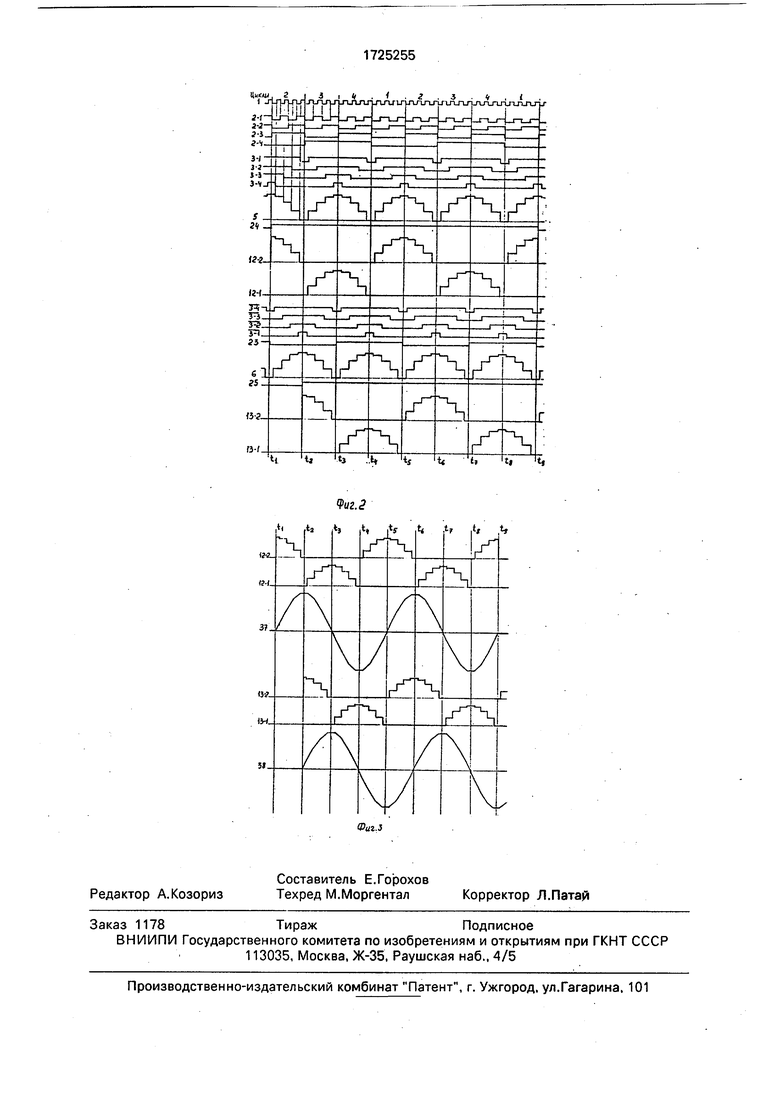

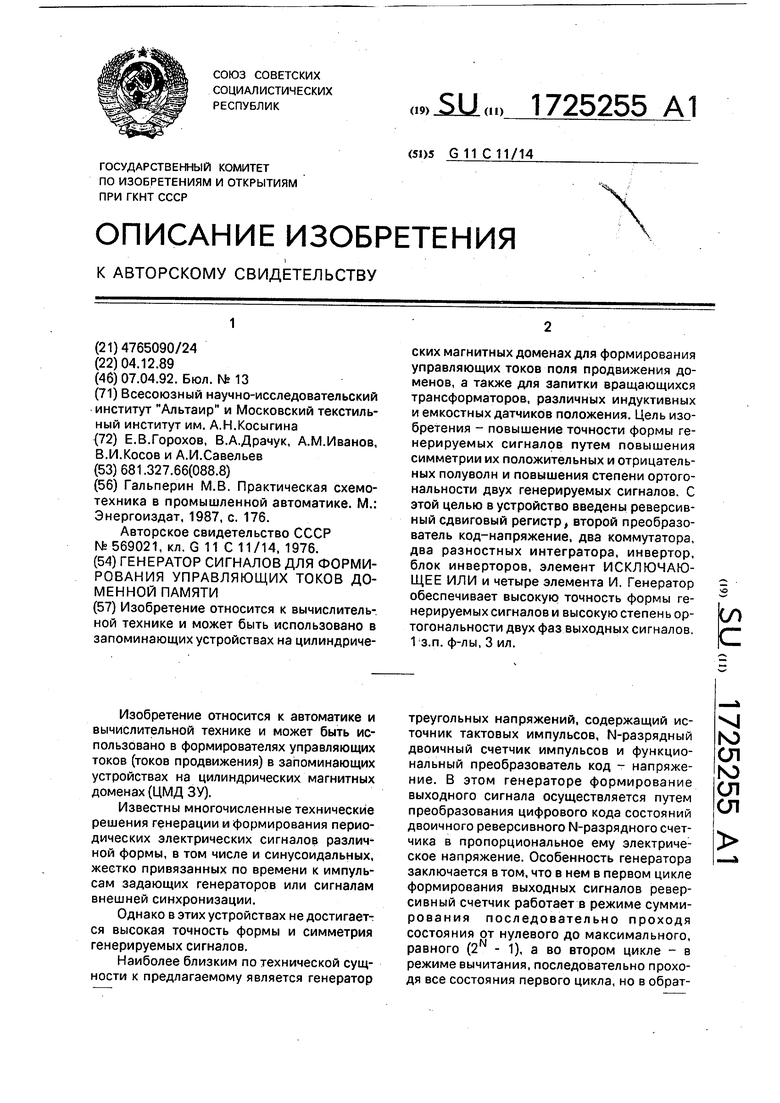

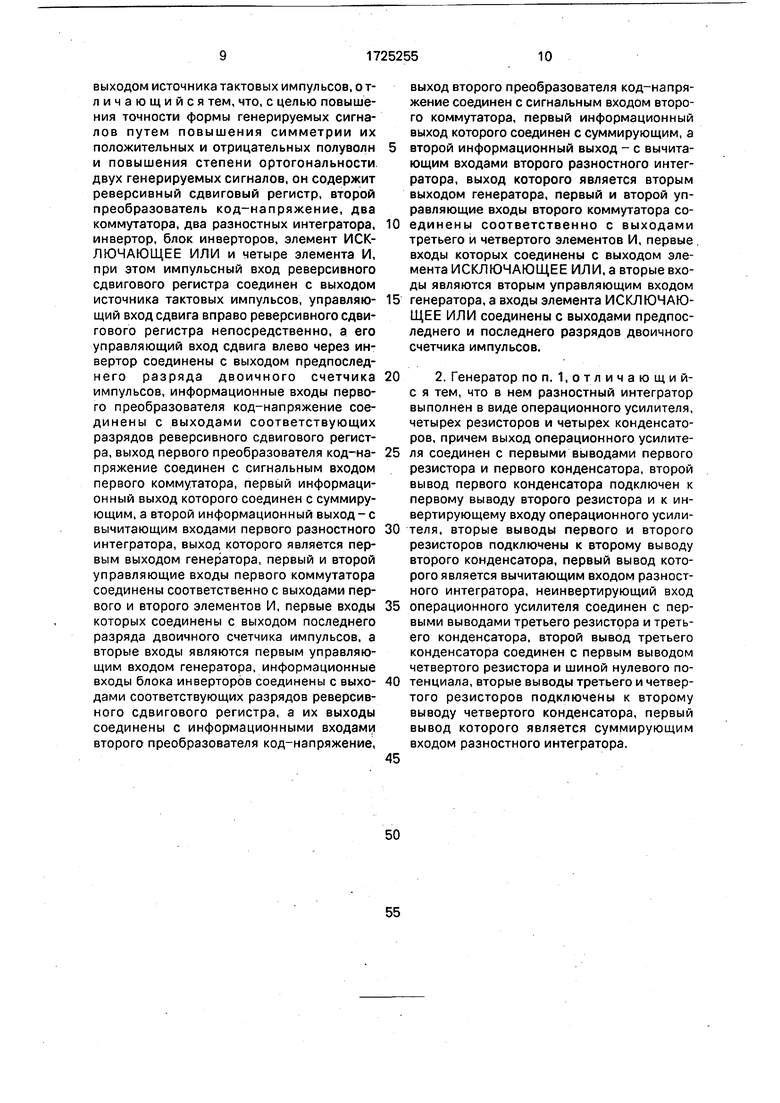

На фиг. 1 представлена функциональная схема предлагаемого генератора сигналов; на фиг. 2 и 3 - временные диаграммы для частного случая, когда разрядность двоичного счетчика в целях наглядности временных диаграмм ограничена числом N 4 (дополнительные индексы у позиций двоичного счетчика и сдвигового регистра соответствуют их разрядам).

В генераторе сигналов выход источника

Iтактовых импульсов соединен со счетным входом N-разрядного двоичного счетчика 2 и импульсным входом ()-разрядного сдвигового регистра 3. Входы SL и SR управления реверсом сдвигового регистра соединены с выходом (N - 1)-го разряда двоичного счетчика 2 непосредственно и через инвертор 4. Преобразователи 5 и 6 код-напряжение, состоящие из весовых резисторов 7-10, соединены по входам с выходами сдвигового регистра 3 непосредственно и через блок

IIинверторов. Коммутаторы 12 и 13, содержащие резисторы 14 и 15 и ключи 16 и 17, и буферные усилители 18 по сигнальным входам подключены к выходам преобразователей 5 и б код-напряжение, а по управляющим входам через логические схемы И 19-22 и ИСКЛЮЧАЮЩЕЕ ИЛИ 23 подключены к выходам (N - 1)-го и N-го разрядам двоичного счетчика 2 и входным шинам 24 и 25 стартстопных сигналов первой и второй фаз.

Разностные интеграторы 26 и 27 выполнены на операционных усилителях 28, резисторах 29-32 и конденсаторах 33-36, их входы подключены к выходам коммутаторов, а выходы являются выходными шинами 37 и 38 двух фаз выходного напряжения.

Устройство функционирует следующим образом.

Источник 1 тактовых импульсов вырабатывает непрерывную серию масштабных сигналов в форме меандра. Двоичный счетчик 2 путем пересчета масштабных импуль- сов по их отрицательным фронтам формирует на выходах (N - 1)-го и N-rb разрядов две серии управляющих импульсов (2-3 и 2-4 на временных диаграммах фиг. 2). Одновременно по положительному фронту каждого из масштабных импульсов осуществляется сдвиг информации сдвигового регистра 3. Направление сдвига определяется взаимно исключающими сигналами SL и SR управления реверсом. В первом цикле работы генератора сигналы на (N - 1)-м и N-м разрядах двоичного счетчика имеют низкий

-нулевой - уровень, и на выходе инвертора 4 появляется сигнал высокого - единичного

-уровня, который по входу SL сдвигового регистра управляет сдвигом его информации влево - в сторону старших разрядов. На информационном входе DI первого разряда сдвигового регистра постоянно присутствует сигнал высокого уровня - 1, и поэтому под воздействием масштабных импульсов, все разряды сдвигового регистра, начиная с первого, заполняются единицами (фиг. 2).

Во втором цикле работы генератора сигнал на выходе (N - 1)-го разряда двоичного счетчика имеет высокий уровень, который по входу SR сдвигового регистра управляет сдвигом его информации вправо - в сторону младших разрядов. На информационном входе DN N-ro разряда сдвигового регистра постоянно присутствует сигнал низкого уровня - О, и поэтому под воздействием масштабных импульсов все разряды, начиная со старшего, заполняются нулями. Во втором цикле работы сдвиговый регистр проходит все состояния первого цикла, но в обратном порядке, т.е. состояния сдвигового регистра в первом и втором циклах являются взаимно зеркальными. Работа сдвигового регистра в третьем и четвертом циклах работы генератора полностью тождественна его работе в первом и втором циклах, но сопровождается высоким уровнем выходного сигнала на N-м выходе двоичного счетчика 2.

Преобразователи 5 и 6 код-напряжение идентичны между собой и являются аналоговыми сумматорами напряжения с весовыми коэффициентами по каждому из (2N 2) входов, определяемыми величинами резисторов 7-10. На входы функционального преобразователя 5 первого канала поступают сигналы непосредственно с выходов всех разрядов сдвигового регистра 3. Резисторы функциональных преобразователей подобраны так, что на выходе преобразователя 5 в первом цикле работы формируется ступенчатое напряжение, середины ступенек которого соответствуют первой четверти периода синусоидальной функции.

Во втором цикле работы напряжение на

выходе функционального преобразователя 5 зеркально его напряжению в первом цикле в силу зеркальности состояний сдвигового регистра в этих циклах. Поэтому в течение

0 первого и второго циклов работы на выходе преобразователя 5 формируется ступенчатое напряжение, середины ступенек которого соответствуют положительной полуволне синусоидального напряжения - напряже5 нию первой полуволны. Аналогичным образом в третьем и четвертом циклах работы на выходе преобразователя 5 формируется напряжение второй полуволны, в точности повторяющее напряжение первой полуволны.

0 С выхода преобразователя 5 напряжение двух полуволн поступает на сигнальный вход коммутатора 12, управляемого логическими элементами И 19 и 20. В отсутствии (низком уровне) стартстопного сигнала на

5 входной шине 24 первой фазы выходные сигналы высокого уровня элементов И 19 и 20 открывают ключи 16 и 17 коммутатора 12, которые шунтируют напряжение на его выходах до величины нулевого уровня. С по0 ступлением стартстопного сигнала на входной шине 24 устанавливается напряжение высокого уровня, снимающее блокировку логических элементов 19 и 20, и их дальнейшая работа определяется исключи5 тельно логическим состоянием N-ro разряда двоичного счетчика 2. В первом и втором циклах N-й разряд двоичного счетчика 2 находится в нулевом состоянии (низкий уровень), которое устанавливает на выходе

0 логического элемента И 19 сигнал единичного (высокого) уровня, а на выходе элемента И 20 - сигнал нулевого уровня. Сигнал низкого уровня на входе ключа 17 удерживает его в разомкнутом состоянии и

5 первая полуволна выходного напряжения преобразователя 5 проходит через резистор 15 и буфер 18 на суммирующий вход разностного интегратора 26. Одновременно сигнал высокого уровня на входе ключа 16

0 удерживает его в замкнутом состоянии и на вычитающем входе разностного интегратора 26 поддерживается напряжение нулевого уровня. В третьем и четвертом циклах N-й разряд счетчика переходит в единичное

5 состояние, в результате чего состояния ключей 16 и 17 изменяются на противоположные и вторая полуволна выходного напряжения преобразователя 5 проходит через резистор 14 и буфер 18 на вычитающий вход разностного интегратора 26, а на

его суммирующем входе поддерживается напряжение нулевого уровня (фиг. 2).

Разностный интегратор 26 (27) выполнен на операционном усилителе 28 с частотно-зависимой RC-цепочкой обратной связи 30 и 35 и симметрирующей RC-цепочкой 31 и 36; резисторы 29 и 32 и разделительные конденсаторы 33 и 34 обеспечивают операционному усилителю режим по постоянному току. При равенстве постоянных времени RC-цепочек 30 и 35 и 31 и 36 между собой схема работает как разностный интегратор, в котором выходное напряжение есть интегральная функция от разности входных напряжений на его суммирующем и вычита- ющем входах. В результате интегрирования первая полуволна ступенчатого напряжения, поступающая на суммирующий вход схемы 26, преобразуется в напряжение кусочно-ломаной формы, точки излома кото- рой лежат на возрастающей ветви косинусо- идальной функции, а вторая полуволна ступенчатого напряжения, поступающая на вычитающий вход схемы 26, преобразуется в напряжение кусочно-ломаной формы с точ- ками излома на убывающей ветви косинусо- идальной функции.

Таким образом, за полный цикл работы N-разрядного двоичного счетчика 2, равный 2 периодам следования импульсов задаю- щего генератора 1, на выходе разностного интегратора 26 формируется один период квазикосинусоидального напряжения, состоящего из 2 кусочно-ломаных участков с точками излома, лежащими на косинусои- дальней функции. Если при этом поступление стартстопного сигнала 24 совпадает с серединой максимальной ступеньки выходного напряжения функционального преобразователя 5 (фиг. 2), то выходной сигнал на шине 37 будет квазисинусоидальным без переходного режима, что и требуется для обеспечения нормальной работы формирователей управляющих токов доменной памяти (фиг. 2 и 3).

Вторая фаза выходного напряжения 38 формируется аналогично первой преобразователем 6 код-напряжение, коммутатором 13, управляемыми логическими элементами И 21 и 22 и разностным интег- ратором 27, но в отличие от формирования первой фазы входы преобразователя 6 подключены к выходам сдвигового регистра 3 через блок 11 инверторов в обратном порядке, а входы логических схем 21 и 22 подклю- чены к выходам (N - 1)-го и N-ro разрядов счетчика 2 через логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и к шине 25 старт- стопного сигнала второй фазы. Такое подключение преобразователя 6, как следует из временных диаграмм (фиг. 2 и 3), обеспечивает строгую ортогональность выходных напряжений 37 и 38, что необходимо для обеспечения устойчивой работы доменной памяти,

Как следует из временных диаграмм (фиг. 3), даже при четырехразрядном двоичном счетчике форма выходных напряжений 37 и 38 достаточно близка синусоидальной и при наобходимости может быть существенно улучшена путем увеличения разрядности двоичного счетчика 2.

Выходное напряжение преобразователя 5 (6) состоит из двух абсолютно одинаковых по форме и величине полуволн, каждая из этих полуволн коммутируется практически без искажений (в качестве буферных усилителей 18 целесообразно использовать эмит- терные или истоковые повторители с почти единицным коэффициентом передачи напряжения и большим входным сопротивлением) на свои входы интегратора 26 (27). Коэффициент передачи напряжения схемы 26 по вычитающему входу для типовых операционных усилителей однозначно определяется величиной постоянной времени RC-цепочки 30 и 35, и коэффициент передачи схемы по суммирующему входу дополнительно зависит от величины постоянной времени RC-цепочки 31 и 36, и при равенстве величин постоянных времени этих RC- цепочек коэффициенты передачи напряжения по суммирующему и вычитающему входам схемы точно равны между собой, Равенство постоянных времени RC-цепочек 30, 35 и 31, 36, а следовательно, и симметрия положительной и отрицательной полуволн выходного напряжения легко достигается подбором одного из элементов обеих RC-цепочек, например резистора 31.

Таким образом, в предлагаемом генераторе сигналов высокая степень осевой (зеркальной) симметрии выходного напряжения обеспечивается симметричной работой сдвигового регистра 3 в различных циклах работы генератора, а высокая степень центральной симметрии обеспечивается равенством постоянных времени RC-цепочек 30, 35 и 31, 36 схем 26 и 27, высокая стабильность которых достигается применением в этих цепочках однотипных элементов, одинаково изменяющих свои параметры под воздействием внешних условий.

Формула изобретения

1. Генератор сигналов для формирования управляющих токов доменной памяти, содержащий источник тактовых импульсов, двоичный счетчик импульсов, преобразователь код-напряжение, счетный вход двоичного счетчика импульсов соединен с

выходом источника тактовых импульсов, о т- пинающийся тем, что, с целью повышения точности формы генерируемых сигналов путем повышения симметрии их положительных и отрицательных полуволн и повышения степени ортогональности, двух генерируемых сигналов, он содержит реверсивный сдвиговый регистр, второй преобразователь код-напряжение, два коммутатора, два разностных интегратора, инвертор, блок инверторов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре элемента И, при этом импульсный вход реверсивного сдвигового регистра соединен с выходом источника тактовых импульсов, управляющий вход сдвига вправо реверсивного сдвигового регистра непосредственно, а его управляющий вход сдвига влево через инвертор соединены с выходом предпоследнего разряда двоичного счетчика импульсов, информационные входы первого преобразователя код-напряжение соединены с выходами соответствующих разрядов реверсивного сдвигового регистра, выход первого преобразователя код-напряжение соединен с сигнальным входом первого коммутатора, первый информационный выход которого соединен с суммирующим, а второй информационный выход-с вычитающим входами первого разностного интегратора, выход которого является первым выходом генератора, первый и второй управляющие входы первого коммутатора соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены с выходом последнего разряда двоичного счетчика импульсов, а вторые входы являются первым управляющим входом генератора, информационные входы блока инверторов соединены с выходами соответствующих разрядов реверсивного сдвигового регистра, а их выходы соединены с информационными входами второго преобразователя код-напряжение,

выход второго преобразователя код-напряжение соединен с сигнальным входом второго коммутатора, первый информационный выход которого соединен с суммирующим, а

второй информационный выход - с вычитающим входами второго разностного интегратора, выход которого является вторым выходом генератора, первый и второй управляющие входы второго коммутатора соединены соответственно с выходами третьего и четвертого элементов И, первые . входы которых соединены с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а вторые входы являются вторым управляющим входом

генератора, а входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами предпоследнего и последнего разрядов двоичного счетчика импульсов.

2. Генератор поп. 1, о т л и ч а ю щ и й- с я тем, что в нем разностный интегратор выполнен в виде операционного усилителя, четырех резисторов и четырех конденсаторов, причем выход операционного усилителя соединен с первыми выводами первого резистора и первого конденсатора, второй вывод первого конденсатора подключен к первому выводу второго резистора и к инвертирующему входу операционного усилителя, вторые выводы первого и второго резисторов подключены к второму выводу второго конденсатора, первый вывод которого является вычитающим входом разностного интегратора, неинвертирующий вход

операционного усилителя соединен с первыми выводами третьего резистора и третьего конденсатора, второй вывод третьего конденсатора соединен с первым выводом четвертого резистора и шиной нулевого потенциала, вторые выводы третьего и четвертого резисторов подключены к второму выводу четвертого конденсатора, первый вывод которого является суммирующим входом разностного интегратора.

Риг./

2j3i..Ј,3-.. jTj-u rpxjtJUT-nj4xir}rulnxuxn

I I ) IrbIrtlITtl1Ttl.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2282937C1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на цилиндрических магнитных доменах для формирования управляющих токов поля продвижения доменов, а также для запитки вращающихся трансформаторов, различных индуктивных и емкостных датчиков положения. Цель изобретения - повышение точности формы генерируемых сигналов путем повышения симметрии их положительных и отрицательных полуволн и повышения степени ортогональности двух генерируемых сигналов. С этой целью в устройство введены реверсивный сдвиговый регистр, второй преобразователь код-напряжение, два коммутатора, два разностных интегратора, инвертор, блок инверторов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре элемента И. Генератор обеспечивает высокую точность формы генерируемых сигналов и высокую степень ортогональности двух фаз выходных сигналов. 1 з.п. ф-лы, 3 ил. СО С

г ч

г-г

(г-tr

ЗЧ-iir 5. 55.

гз(г-г

Фиг. « ia ц ц ,ty t t, ,t, t,

h

о-л

)H.

ST

Ј

Ј

ЈT

Ј±h

| Гальперин М.В | |||

| Практическая схемотехника в промышленной автоматике | |||

| М.: Энергоиздат, 1987, с | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

| Генератор треугольного напряжения | 1975 |

|

SU569021A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-04-07—Публикация

1989-12-04—Подача