мяти, первый и второй входы которого соединены г. пятым и шестым выходами блока управления, седьмой и восьмой .выходы которого соединены с первым и вторым входами коммутатора магистралей, выходы которого соединены двунаправленной связью с в ходами группы блока буферной памяти и с входами второй группы коммутаторов данных, входы третьей группы которых соединены двунаправленной связью с. входами блоков приема сообщений первой группы, вькоды блоков приема сообщений второй группы соединены двунаправленной связью с входами четвертой группы коммутаторов данных первые входы которых соединены с выходами дешифратора выбора канала, выход блока управления соединен с входом блока памяти команд, выходы второй группы блока счетчиков соединены с входами группы дешифратора записи, выходы которого соединены с входами группы коммутатора записи, выходы пятой группы блока счетчиков соединены с входами первой группы первого коммутатора адреса, вход которого соединен с выходом блока счетчиков и вторым входбм коммутатора управляющих сигналов, выходы первой группы первого коммутатора адреса соединены с входами группы блоков приема сообщений первой групры, выходы второй группы первого комыутатора адреса соединены с входами группы блоков приема сообщений втоуой группы, третий вход коммутатора управляющих сигналов является четвер1 ым входом устройства, входы-выходы коммутаторов данных являются входамивыходами первой группы устройства, входы-выходы второй группы коммута1ора магистралей являются входамивыходами второй группы устройства, «ходы второй группы первого коммутатора адреса являются группой управ ляющих входов устройства.

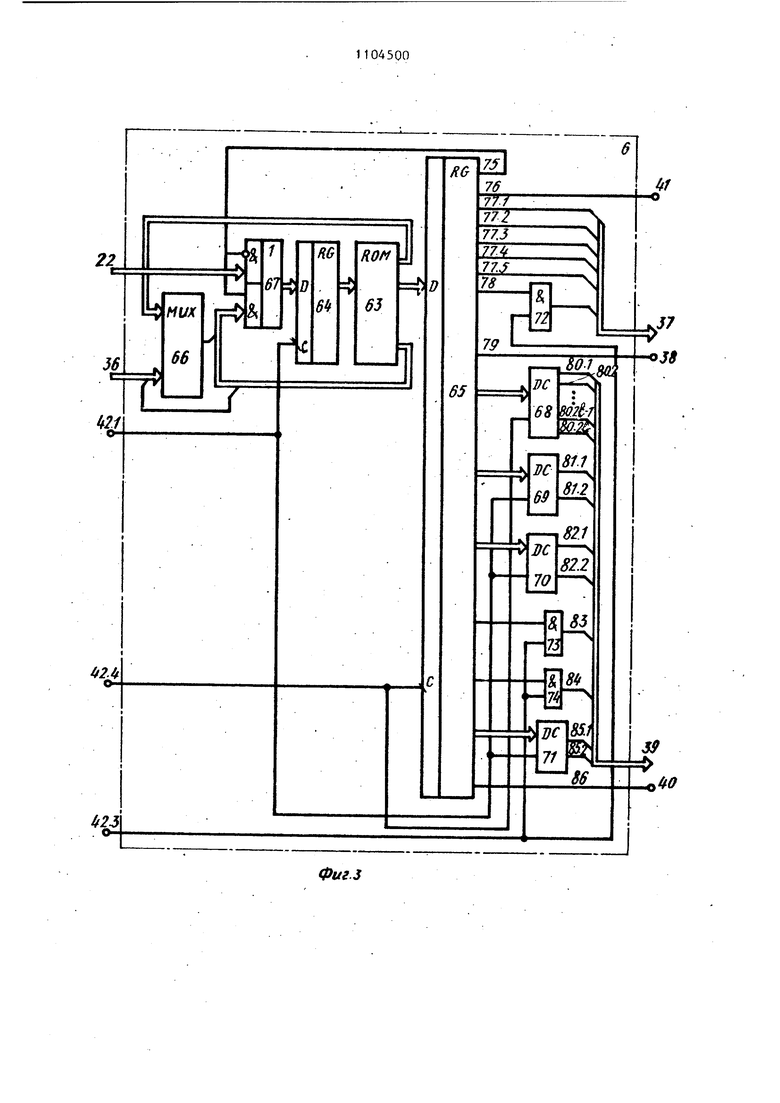

2. Устройство по П.1, отличающееся тем, что блок управления содержит мультиплексор, второй коммутатор адреса, регистр адреса, узел памяти микрокоманд, регистр микрокоманд, первый, второй и третий элементы И, первый, второй, третий и четвертый дешифраторы, входы

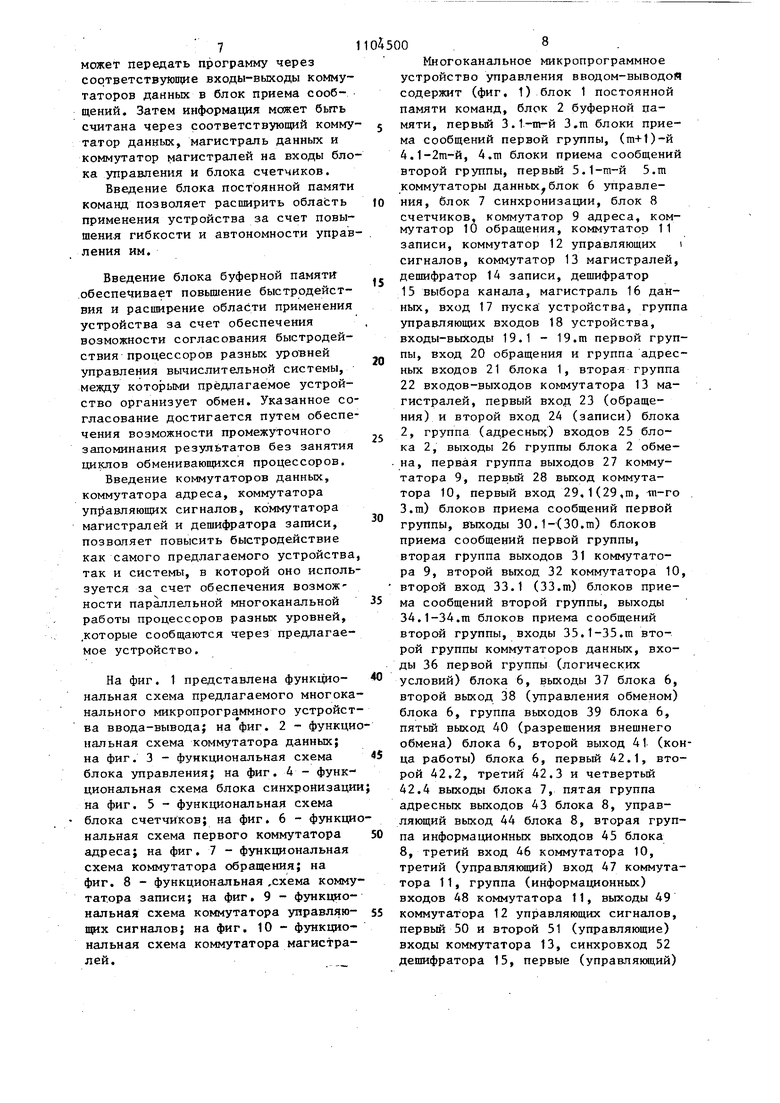

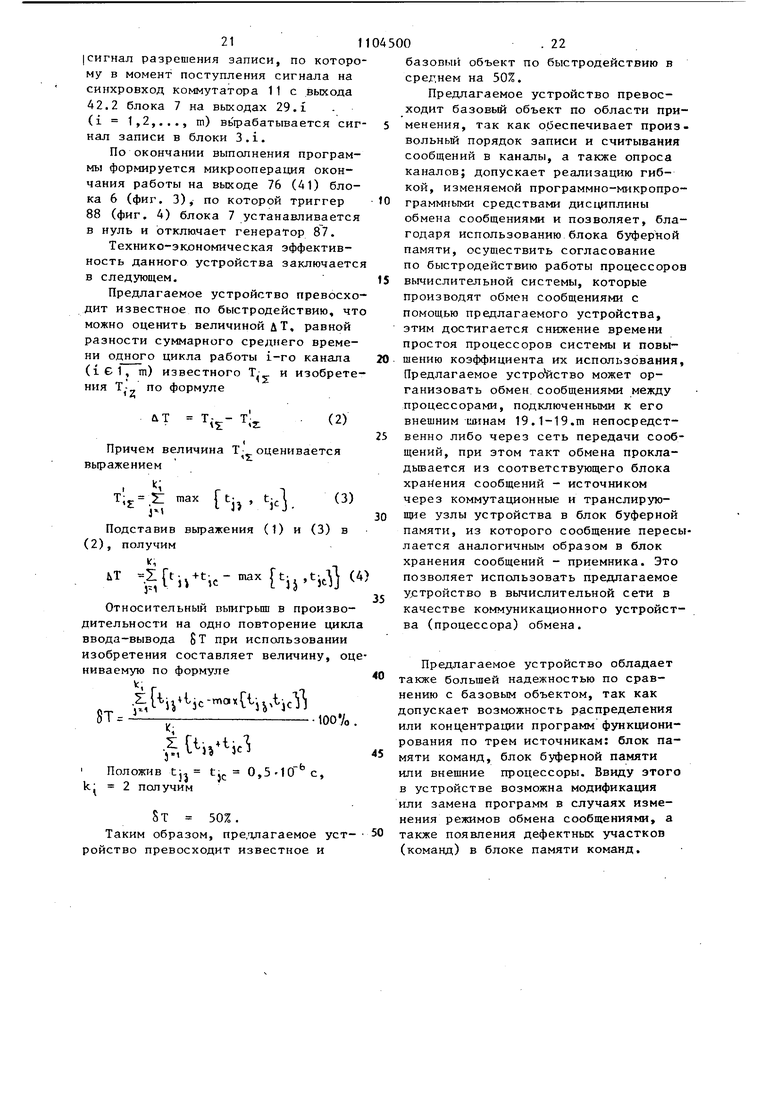

группы которых соединены с выходами группы регистра микрокоманд, входы группы которого соединены с выходами первой группы узла памяти микрокоманд выходы второй группы которого соединены с входами первой группы мультиплексора, выходы которого соединены с выходами третьей группы узла памяти микрокоманд и с входами первой группы второго коммутатора адреса, выходы которого соединены с входами группы регистра адреса, выходы которого соединены с входами узла памяти микрокоманд, первый выход регистра микрокоманд соединен с входом второго коммутатора адреса,второй выход регистра микрокоманд соединен с первым входом первого элемента И,второй вход которого соединен с первыми входами второго и третьего элементов И, тактовый вход регистра микрокоманд соединен с входом первого дешифратора, тактовый вход регистра адреса соединен с входами второго, третьего и четвертого дешифраторов, третий и четвертый выходы регистра микрокоманд соединены соответственно с вторыми входами второго и третьего элементов И, выход узла памяти микрокоманд соединен с входом мультиплексора, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый выходы регистра микрокоманд являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым выходами блока управления, выход первого элемента И является девятым выходом блока управления, выходы первого, второго, третьего, четвертого дешифраторов, второго и третьего элементов И являются выходами группы блока управления, тактовый вход регистра адреса является первым входом блока управления, второй вход первого элемента И является вторым входом блока управления, тактовый вход регистра микрокоманд является третьим входом блока управления, входы второй группы мультиплексора являются входами первой группы блока управления, входы второй группы второго коммутатора адреса являются входами второй группы блока управления. Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных для организации обмена информацией между подсистемами разных уровней. Известно многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной маши ной, содержащее блок синхронизации, блоки хранения сообщений, блоки депифрации, коммутаторы записи и считывания lj . Недостатком этого устройства является низкое быстродействие, обусловленное жестким порядком определенйя последовательности записи сообщений. Кроме этого, устройству присуща узкая область применения в связи с установкой приоритета выбора сообщений в зависимости от их количестна, а не важности для процессора высшего уровня управления. Наиболее близким к предлагаемому устройству по технической сущности и достигаемому результату является многоканальное устройство для ввода информации, содержащее генератор импульсов (блок синхронизации), блок дешифрации, блок хранения сообщений счетчик, коммутатор записи, коммутатор считывания, коммутатор входов, коммутатор выходов, блок дешифрации числа заявок в каналах, элементы И, блок сравнения, причем генератор импульсов соединен с входом блока дешифрации, каждый вход устройства соединен с входом элемента И и кодовым входом коммутатора записи соответствующего канала, выход элемента ИЛИ подключен к управляющему входу коммутатора .записи канала и суммирующему входу реверсивного счетчика канала, выходы коммутатора записи канала соединены с кодовыми входами блоков хранения сообщений канала, выходы которых соединены с выходом устройства, а управляющие входы - с выходами коммутатора считывания кана ла, выходы реверсивных счетчиков каналов соединены с группой входов блока дешифрации, каждый выход которого соединен с входом коммутатора считьгоания и вычитающим входом ревер сивного счетчика соответствующего канала, группа информационных входов коммутатора входов соединена с группой входов устройства, группа выходов - с кодовыми входами коммутат/ров записи каналов, группа адресных входов - с первой группой выходов блока сравнения, а второй вход - с первым вькодом коммутатора выходов, группа информационных входов которого подключена к выходам блоков хранения сообщений каналов, вход - к второй группе выходов блока сравнения и других дополнительных входов блока дешифрации, а второй выход является выходом устройства, группа входов блока сравнения соединен ; с группой выходов блока дешифрации числа заявок в каналах, группа входов которого подключена к выходам реверсивных счетчиков каналов 2j . Недостатками известного устройства являются низкое быстродействие и узкая область использования. В устройстве используется iri параллельно работающих каналов, каждый из которых содержит блоки приема сообщений. Причем в устройстве схемотехнически не предусмотрена возможность одновременной записи и считьшания информации из блоков приема сообщений одного и того же канала. Поэтому суммарное среднее время одного цикла работы i-ro канала (161, т)Т;J может быть вычислено по формуле I к; ; .Mc, где t:,,t: - среднее время записи и считьтания из j-ro блока приема сообщений соответственно;k - число блоков приема сообщений i-ro канала устройства. Из выражения (1) следует, что среднее время одного цикла работы i-ro (ie 1, m) канала в известном устройстве велико именно из-за отсутствия возможности одновременной записи и считывания информации из блоков приема сообщений одного и того же канала. Это обусловлено тем, что в устройстве задается жесткий порядок записи сообщений, а затем их считывания из блоков приема сообщений. Узкая область применения известного устройства обусловлена тем, что в устройстве структурно предопределен последовательный порядок записи и считьюания сообщений в каналы и, кроме того,, последовательность опроса каналов для считьшания сообщений установлена в соответствии с заране заданными приоритетами. Поэтому в устройстве невозможно реализовать произвольную дисциплину обмена сообщениями. Цель изобретения - повыр-ение быст родействия устройства. Поставленная цель достигается тем, что в многоканальное микропрограммное устройство ввода-вывода, содержащее, блок синхронизации, комму татор обращений, коммутатор записи, первую и вторую группы блоков приема сообщений, блок счетчиков, дешифратор выбора канала и блок управления первый выход которого соединен с синхровходом дешифратора выбора канала, второй выход блока управления соединен с первым входом коммутатора обращений, второй вход которого соед нен с выходом блока счетчиков, выходы первой группы которого соединен с входами первой группы блока управления, первый вход которого соединен с первым выходом блока синхронизации второй вьгход которого соединен с пер вым входом коммутатора записи,, выход первой группы которого соединены с первыми входами блоков приема сообщений- первой группы, вторые вход которых соединены с первым выходом коммутатора обращении, второй выход которого соединен с первьми входами блоков приема сообщений второй группы, вторые входы которых соединены с выходами второй группы коммутатора записи, третий и четвертый выходы блока синхронизации соединены соответственно с вторым и третьим входами блока управления, третий выход которого соединен с первым входом блока синхронизации,- выходы второй группы бл.ока счетчиков соединены с информационными входами дешифратора выбора канала, второй вход коммутатора записи соединен с вторым входом коммутатора обращений, выходы группы блока управления соединены с входами первой группы блока счетчиков, второ вход блока синхронизации является первым входом устройства, третий вход коммутатора обращений является вторым входом устройства, третий вход коммутатора записи является третьим входом устройства, введены коммутатор управляющих сигналов, блока памяти команд, блок буферной -памяти, коммутатор магистралей, дешифратор записи, первый коммутатор адреса и коммутаторы данных, входы первой группы которых соединены с выходами коммутатора управляющих сигналов, первый вход которого соединен с четвертым выходом блока управления и с первым входом дешифратора записи, второй вход которого соединен с вторым входом блока управления, входы второй группы которого соединены с входами второй группы блока счетчиков, с входами-выходами первой группы коммутатора магистралей и с выходами блока памяти команд, входы группы которого соединены с выходами третьей группы блока счетчиков, выходы четвертой группы которого соединены с адресными входами блока буферной памяти, первый и второй входы которого соединены с пятым и mecTbiM выходами блока управления, седьмой и восьмой выходы которого соединены с первым и вторым входами коммутатора магистралей, выходы которого соединены двунаправленной связью с выходами группы блока буферной памяти и с входами второй группы коммутаторов данных, входы третьей группы которых соединены двунаправленной связью с выходами блоков приема сообщений первой группы,вьгходы блоков приема сообщений второй группы соединены двунаправленной связью с входами четвертой группы коммутаторов данных-, первые входы которых соединены с выходами дешифратора выбора канала, выход блока управления соединен с выходом блока памяти команд, выходы второй группы блока счетчиков соединены с входами группы дешифратора записи, выходы которого соединены с входами группы коммутаторэ записи, выходы пятой группы блока счетчиков соединены с входами первой группы первого коммутатора адреса, вход которого соединен с выходом блока счетчиков и вторым входом коммутатора управляющих сигналов, выходы первой группы первого коммутатора адреса соединены с входами группы блоков приема сообщений первой группы, выходы второй группы первого коммутатора адреса соединены с входами группы блоков приема сообщений второй группы, третий вход коммутатора управляющих сигналов является четвертым входом устройства, входы-выходы коммутаторов данных являются входамивыходами первой группы устройства, входы-выходы второй группы коммутатора магистралей являются входамивыходами второй группы устройства, входы второй группы первого коммутатора адреса явл.яются группой управляющих входов устройства. Причем блок управления содержит мультиплексор, второй коммутатор адр са, регистр адреса, узел памяти микрокоманд, регистр микрокоманд, первый, второй и третий элементы И, пер вый, второй, третий и четвертый дешифраторы, входы группы которых соединены с выходами группы регистра микрокоманд, входы группы которого соединены с выходами первой группы узла памяти микрокоманд, выходы второй группы которого соединены с входами первой группы мультиплексора выходы которого соединены с выходами третьей группы узла памяти микрокоманд и с входами первой группы второ го коммутатора адреса, выходы которого соединены с входами группы реги стра адреса, выходы которого соединены с входами узла памяти микрокоманд, первый выход регистра микрокоманд соединен с входом второго коммутатора адреса, второй выход регистра микрокоманд соединен с первым входом первого элемента И, второй вход которого соединен с первьми входами второго и третьего элементов И, тактовый вход регистра микрокоманд соединен с входом первого дешифратора, тактовый вход регистра адреса соединен с входами второго, третьего и четвертого дешифраторов, третий и четвертый выходы регистра микрокоманд соединены соответственно с вторьми входами второго и третьего элементов И, выход узла памяти микр команд соединен с входом мультиггпексора, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый выходы регистра микрокоманд являются соответственно первым, вторым, третьим, четвертым, пя- тым, шестьм, седьмым и восьмым выходами блока управления, вь1ход первого элемента И является девятым выходом блока управления, выходы первого, вт рого, третьего и четвертого дешифраторов, второго и третьего элементов И являются выходами группы блока управления, тактовый вход регистра адреса является первым входом блока управления, второй вход первого эле-i. мента И является вторым входом блока управления, тактовый вход регистра микрокоманд является третьим входом блока управления, входы второй группы мультиплексора являются входами первой группы блока управления, входы аторой группы второго коммутатора адреса являются входами второй группы блока управления. Сущность предлагаемого изобретения состоит в следующем. Повышение быстродействия достигается за счет уменьшения суммарного времени одного цикла работы i-ro (i 1, га) канала путем введения новых элементов и связей, которые позволяют осуществлять запись и считывание информации в (из) блока приема сообщений одного и того же канала. Расширение области применения уст ройства достигается введением произ- вольного порядка, устанавливаемого микропрограммно, записи и считывания сообщений в каналы, а также опроса каналов. Это позволяет реализовать в устройстве гибкую произвольную дисциплину обмена сообщениями, что расширяет область его применения. . Кроме того, предлагаемое устройство допускает организацию обмена сообщениями между процессорами вычислительной системы, подключенными к внешним шинам сообщений устройства непосредственно или через сеть передачи сообщений. Дополнительно предлагаемое устройство обладает повышенной надежностью, обусловленной тем, что программы его функционирования могут храниться не только в блоке памяти команд, но и в блоке буферной памяти, блоках приема сообщений, а также поступать от внешних источников (процессоров). В случае хранения программы в блоке буферной памяти программы (константы и др) из блока буферной памяти через магистраль данных, коммутатор магистралей поступает на входывыходы первой группы коммутатора магистралей, откуда могут передаваться, в блок счетчиков и блок управления . При поступлении программ от внеш них источников внешний процессор может передать программу через соответствуюп ие входы-выходы коммутаторов данных в блок приема сообщений. Затем информация мажет быть считана через соответствующий комму татор данных, магистраль данных и коммутатор магистралей на входы бло ка управления и блока счетчиков. Введение блока постоянной памяти команд позволяет расширить область применения устройства за счет повышения гибкости и автономности управ ления им, Введение блока буферной памяти .обеспечивает повышение быстродействия и расширение области применения устройства за счет обеспечения возможности согласования быстродействия процессоров разных уровней управления вычислительной системы, между которыми предлагаемое устройство организует обмен. Указанное со гласование достигается путем обеспе чения возможности промежуточного запоминания результатов без занятия циклов обменивающихся процессоров. Введение коммутаторов данных, коммутатора адреса, коммутатора управляющих сигналов, коммутатора магистралей и дешифратора записи, позволяет повысить быстродействие как самого предлагаемого устройства так и системы, в которой оно исполь зуется за счет обеспечения возмож ности параллельной многоканальной работы процессоров разных уровней, .которые сообщаются через предлагаемое устройство. На фиг. 1 представлена функциональная схема предлагаемого многока нального микропрограммного устройст ва ввода-вывода; на фиг. 2 - функци нальная схема коммутатора данных; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема блока синхронизаци на фиг. 5 - функциональная схема блока счетчиков; на фиг. 6 - функци нальная схема первого коммутатора адреса; на фиг. 7 - функциональная схема коммутатора обращения; на фиг. 8 - функциональная ,схема комму татора записи; на фиг, 9 - функциональная схема коммутатора управляющих сигналов; на фиг, 10 - функциональная схема коммутатора магистралей. Многоканальное микропрограммное устройство управления вводом-выводой содержит (фиг, 1) блок 1 постоянной памяти команд, блок 2 буферной памяти, первый 3.1-т-й 3,т блоки приема сообщений первой группы, (т+1)-й 4.1-2т-й, 4.т блоки приема сообщений второй группы, первый 5.1-га-й 5.т коммутаторы данных блок 6 управления, блок 7 синхронизации, блок 8 счетчиков, коммутатор 9 адреса, коммутатор 10 обращения, коммутатор 11 записи, коммутатор 12 управляющих сигналов, коммутатор 13 магистралей, дешифратор 14 записи, дешифратор 15 выбора канала, магистраль 16 данных, вход 17 пуска устройства, группа управляющих входов 18 устройства, входы-выходы 19.1 - 19.m первой группы, вход 20 обращения и группа адресных входов 21 блока 1, вторая группа 22 входов-выходов коммутатора 13 магистралей, первый вход 23 (обращения) и второй вход 24 (записи) блока 2, группа (адресных) входов 25 блока 2, выходы 26 группы блока 2 обмена, первая группа выходов 27 коммутатора 9, первый 28 выход коммутатора 10, первый вход 29, 1(29,т, iti-ro . З.т) блоков приема сообщений первой группы, выходы 30.1-(30.т) блоков приема сообщений первой группы, вторая группа выходов 31 коммутатора 9, второй выход 32 коммутатора 10, второй вход 33.1 (33.т) блоков приема сообщений второй группы, выходы 34.1-34.т блоков приема сообщений второй группы, входы 35,1-35.m второй группы коммутаторов данных, входы 36 первой группы (логических условий) блока 6, выходы 37 блока 6, второй выход 38 (управления обменом) блока 6, группа выходов 39 блока 6, пятьй выход 40 (разрешения внешнего обмена) блока 6, второй выход 41 (конца работы) блока 6, первый 42.1, второй 42.2, третий 42.3 и четвертый 42.4 выходы блока 7, пятая группа адресных выходов 43 блока 8, управляющий выход 44 блока 8, вторая группа информационных выходов 45 блока 8, третий вход 46 коммутатора 10, третий (управляющий) вход 47 коммутатора 11, группа (информационных) входов 48 коммутатора 11, выходы 49 коммутатора 12 управляющих сигналов, первый 50 и второй 51 (управляющие) входы коммутатора 13, синхровход 52 ешифратора 15, первые (управляющий)

входы 53.1 (53.m) коммутаторов дан- . ных 5.1 (5,т).

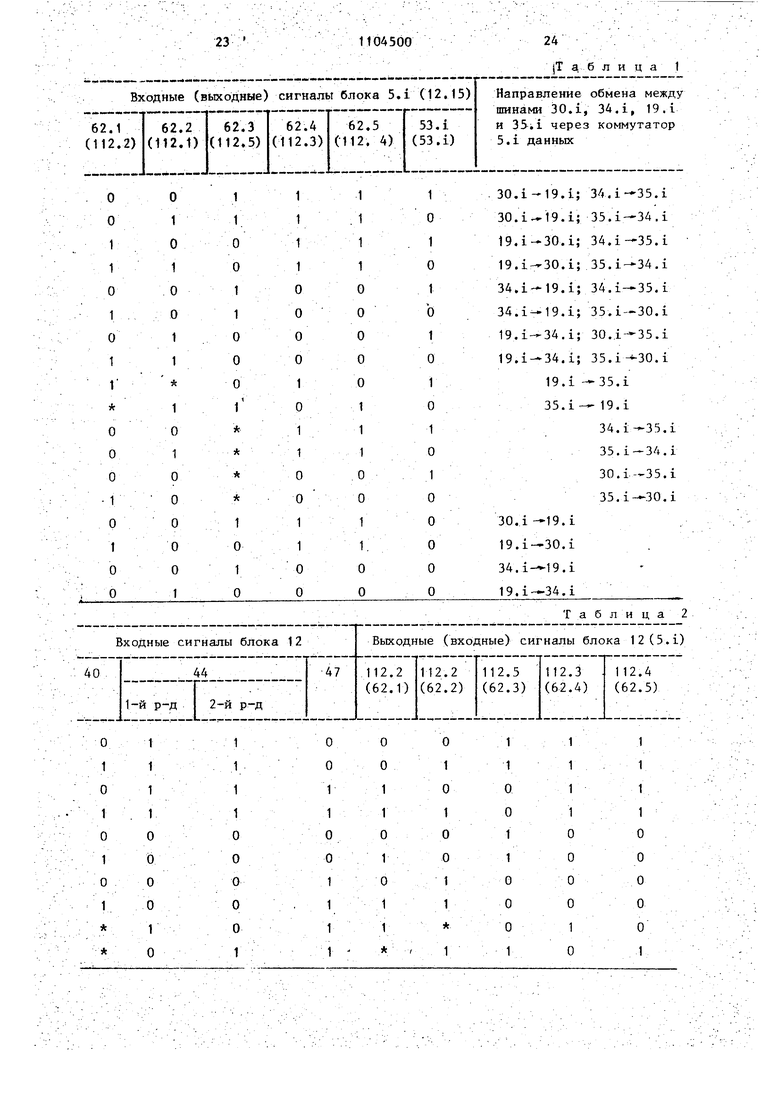

Коммутатор 5,1 (i .1,2,...., m) данных содержит первьпЧ 54, второй 55, третий 56 и -четвертый 57 узлы коммутации, первый 58,. второй 59, третий 60 и четвертьпг 61 узлы магистральных элементов, первый 62.1, второй 62.2, третий 62.3, четвертый 62.4 и пятый 62.5 входы первой группы входов коммутатора 5.1.

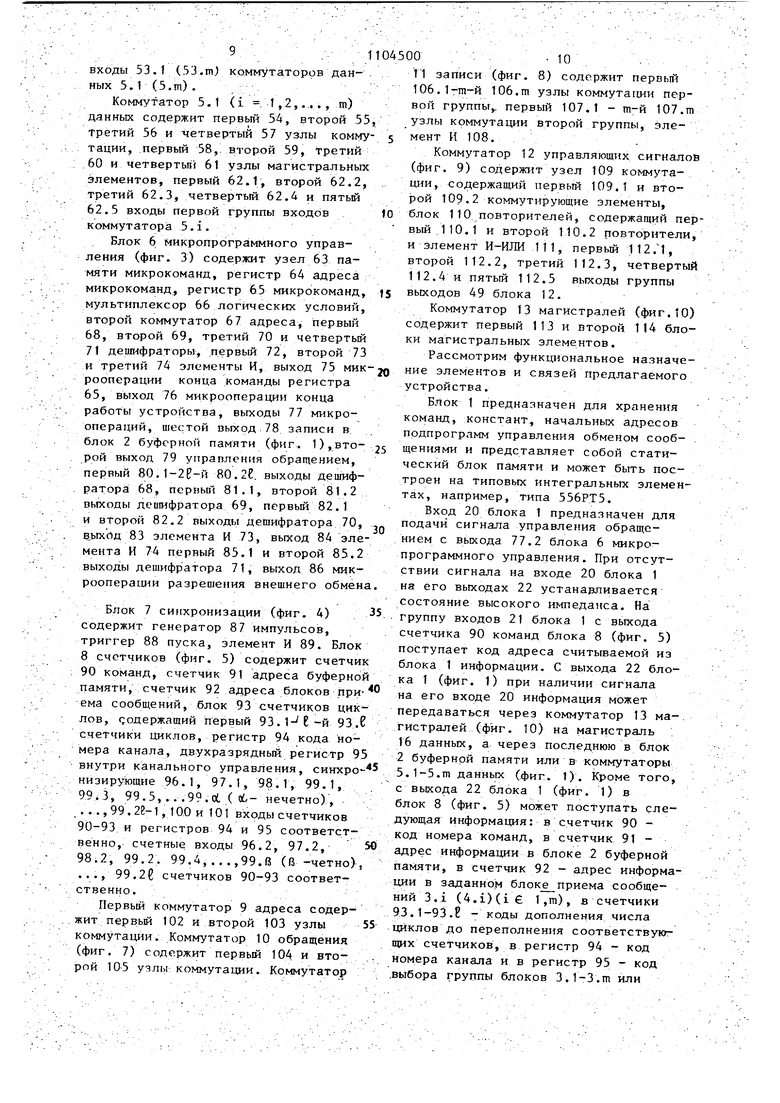

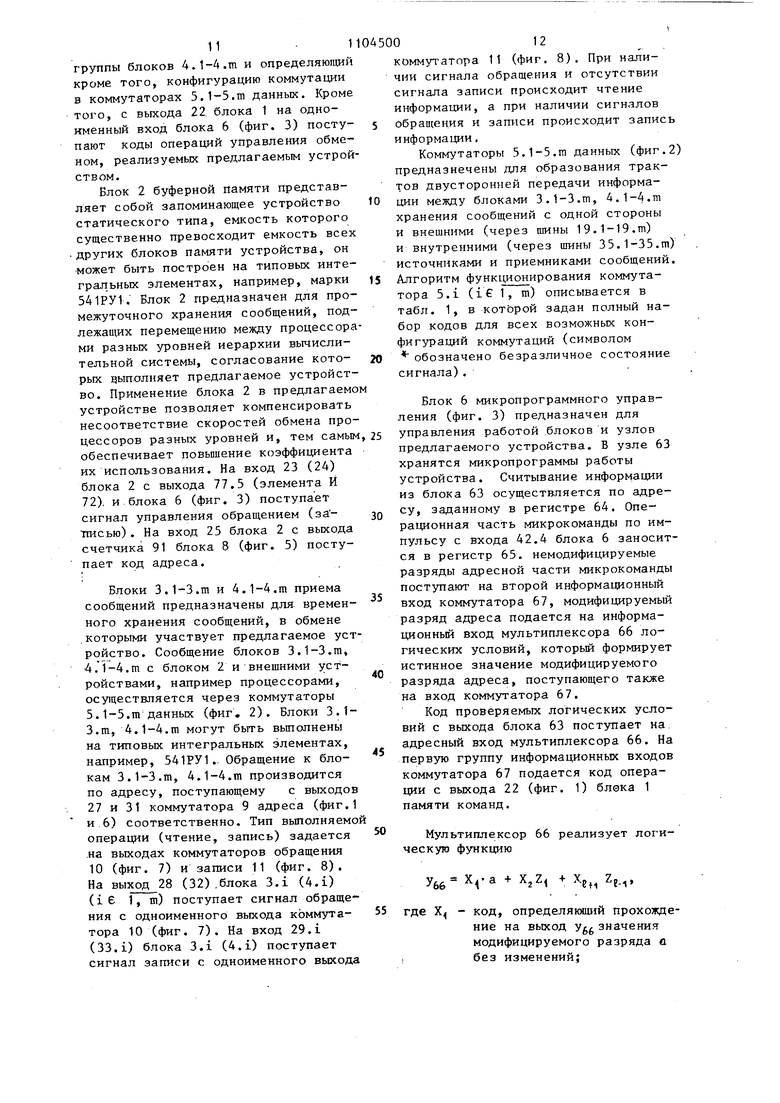

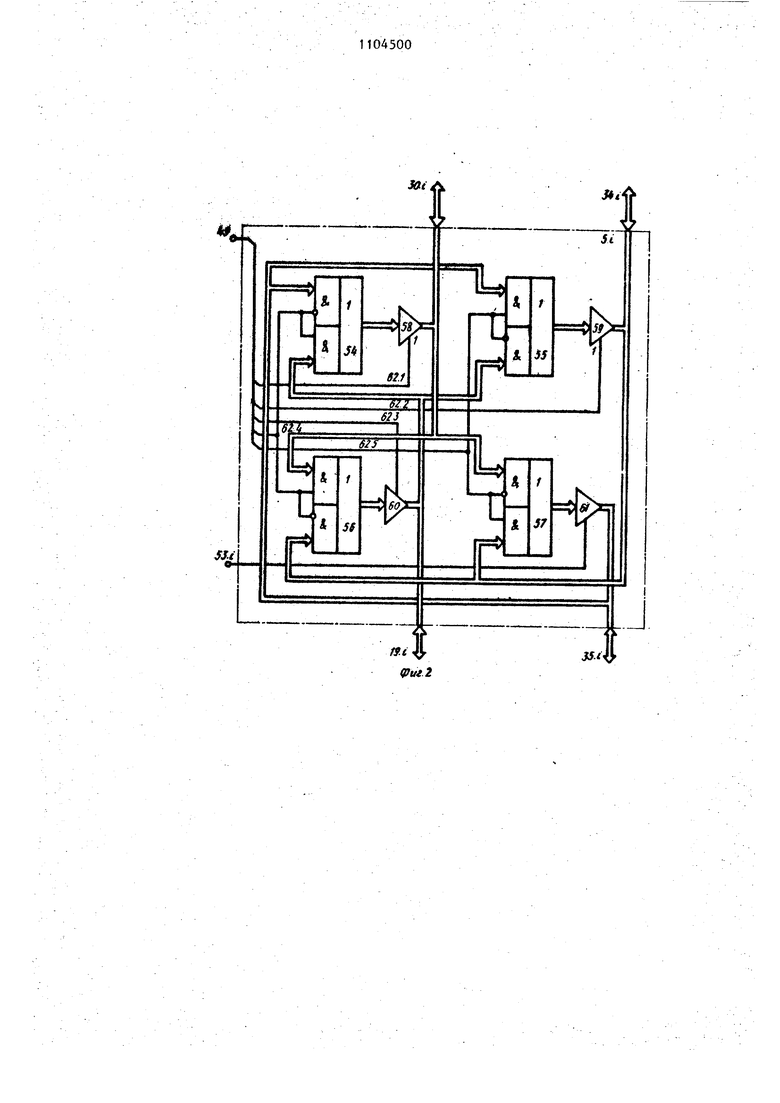

Блок ( микропрограммного управления (фиг. 3) содержит узел 63 памяти микрокоманд, регистр 64 адреса микрокоманд, регистр 65 микрокоманд, мультиплексор 66 логических условий, второй коммутатор 67 адреса, первый 68, второй 69, третий 70 и четвертьй 71 дешифраторы, .первый 72, второй 73 и третий 74 элементы И, выход 75 микрооперации конца команды регистра 65, выход 76 микрооперации конца работы устройства, выходы 77 микроопераций шестой выход 78 записи в блок 2 буферной памяти (фиг. 1),второй выход 79 угтрапления обращением, первый 80.1-2р-й 80.2. выходы дешифратора 68, псрвьш 81.1, второй 81.2 выходы дешифратора 69, первый 82.1 И второй 82.2 выходы дешифратора 70, выхЬд 83 элемента И 73, выход 84 элемента И 74 первый 85.1 и второй 85.2 выходы дешифратора 71, выход 86 микрооперации разрешения внешнего обмена

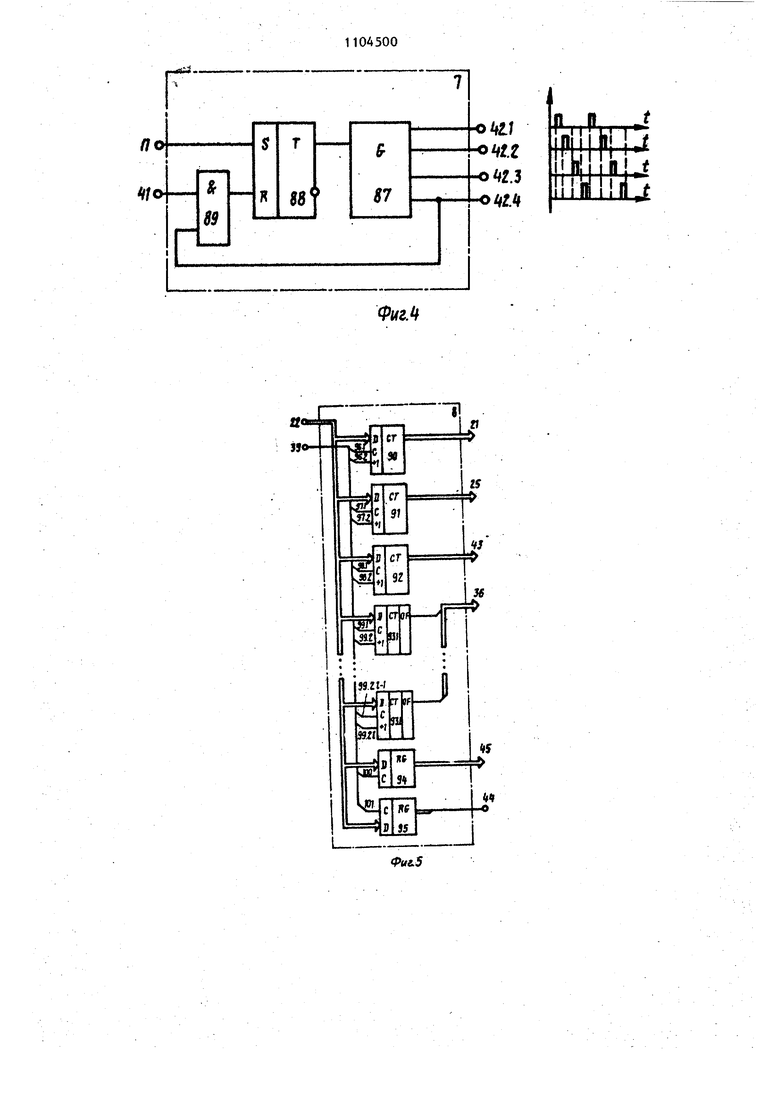

Блок 7 синхронизации (фиг. 4) содержит генератор 87 импульсов, триггер 88 пуска, элемент И 89. Блок 8 счетчиков (фиг. 5) содержит счетчик 90 команд, счетчик 91 адреса буферной памяти, счетчИк 92 адреса блоков приема сообщений, блок 93 счетчиков циклов, содержащий первый 93. 1- 6 -и 93.6 счетчики циклов, регистр 94 кода номера канала, двухразрядный регистр 95 внутри канального управления, синхронизирующие 96.1, 97.1, 98.1, 99. Г, 99.3, 99.5,...99.о(. ( об- нечетно), ... ,99.28-1,100 и 101 входы счетчиков 90-93 и регистров 94 и 95 соответственно, счетные входы 96.2, 97.2, 98.2, 99.2. 99.4,...,99.В (В -четно), ...,99.2 счетчиков 90-93 соответственно.

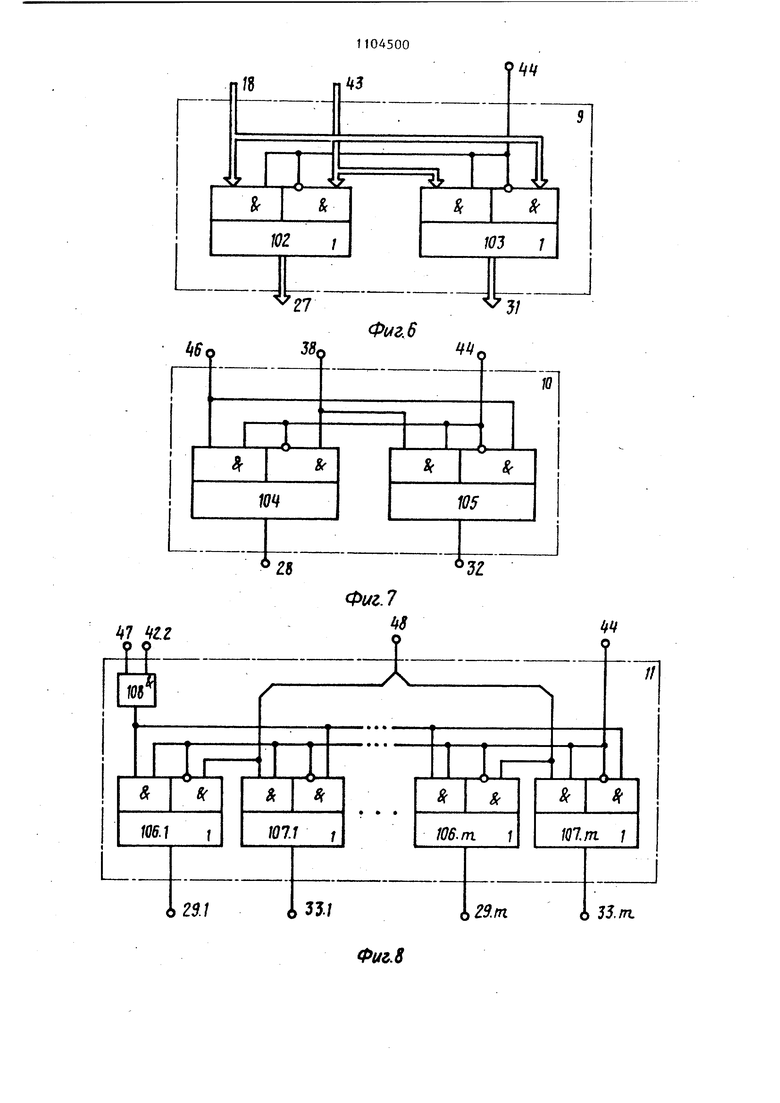

Первый коммутатор 9 адреса содержит первый 102 и второй 103 узлы коммутации. Коммутатор 10 обращения (фиг. 7) содержит первый 104 и второй 105 узлы коммутации. Коммутатор

11 записи (фиг. 8) содержит первый 106.1-т-й 106.m узлы коммутации первой группы,, первый 107.1 - тп-й 107.тп узлы коммутации второй группы, элемент И 108.

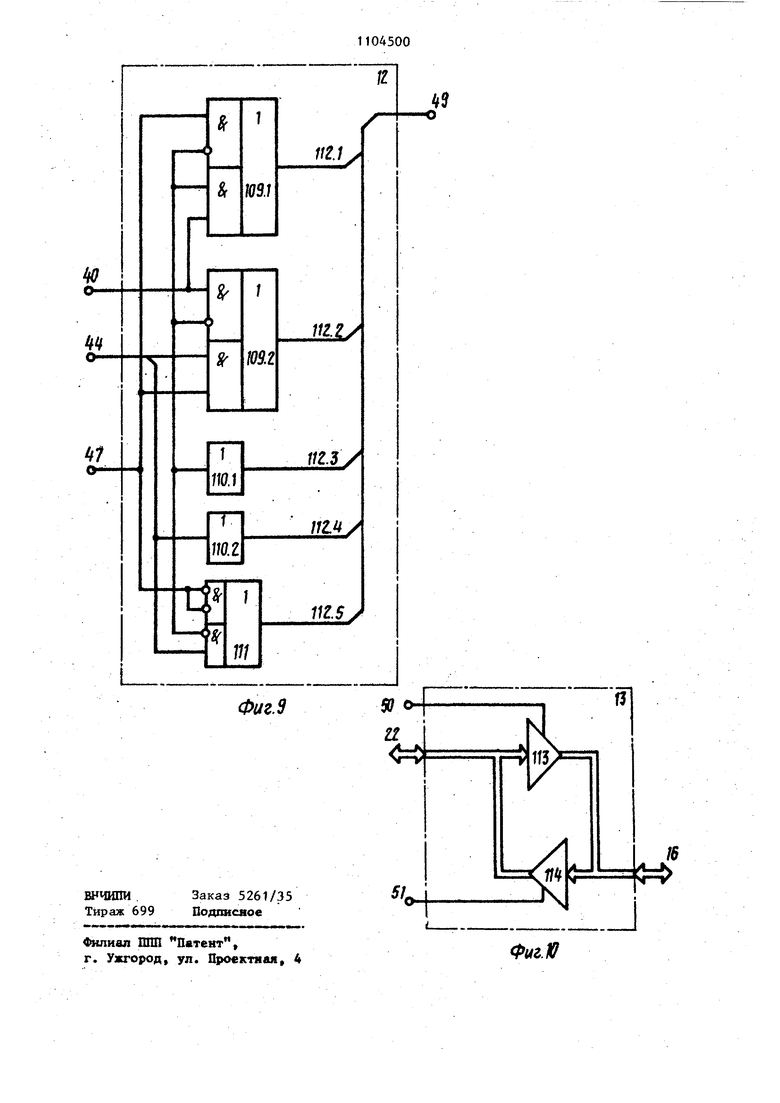

Коммутатор 12 управляющих сигнало (фиг. 9) содержит узел 109 коммутации, с одержаший первый 109.1 и второй 109.2 коммутирующие элементы, блок 110 повторителей, содержащий певый 110.1 и второй 110.2 повторители и элемент И-ИЛИ 111, первый 112.1, второй 112.2, третий 112.3, четверты 112.4 и пятый 112.5 выходы группы вькодов 49 блока 12.

Коммутатор 13 магистралей (фиг.10 содержит первый 113 и второй 114 блоки магистральных элементов.

Рассмотрим функциональное назначение элементов и связей предлагаемого устройства.

Блок 1 предназначен для хранения команд, констант, начальных адресов подпрограмм управления обменом сообщениями и представляет собой статический блок памяти и может быть построен на типовых интегральных элементах, например, типа 556РТ5.

Вход 20 блока 1 предназначен для подачи сигнала управления обращением с выхода 77.2 блока 6 микропрограммного управления. При отсутствии сигнала на входе 20 блока 1 на его выходах 22 устанавливается состояние высокого импеданса. На группу входов 21 блока 1 с выхода счетчика 90 команд блока 8 (фиг. 5) поступает код адреса считываемой из блока 1 информации. С выхода 22 блока 1 (фиг. 1) при наличии сигнала на его входе 20 информация может передаваться через коммутатор 13 магистралей (фиг. 10) на магистраль 16 данных, а через последнюю в блок 2 буферной памяти или в коммутаторы 5.1-5.т данных (фиг. 1). Кроме того, с выхода 22 блока 1 (фиг. 1) в блок 8 (фиг. 5) может поступать следующая информация: в счетчик 90 код номера команд, в счетчик 91 адрес информации в блоке 2 буферной памяти, в счетчик 92 - адрес информации в заданном блок приема сообщений 3.1 (4.i)(ie 1,m), в счетчики 93.1-93.8 - коды дополнения числа циклов до переполнения соответствующих счетчиков, в регистр 94 - код номера канала и в регистр 95 - код .выбора группы блоков 3.1-З.т или группы блоков 4.1-4.m и определяющий кроме того, конфигурацию коммутации в коммутаторах 5.1-5.т данных. Кроме того, с выхода 22 блока 1 на одноименный вход блока 6 (фиг. 3) поступают коды операций управления обменом, реализуемых предлагаемым устрой ством. Блок 2 буферной памяти представляет собой запоминающее устройство статического типа, емкость которого существенно превосходит емкость всех других блоков памяти устройства, он может быть построен на типовых интегральных элементах, например, марки 541РУ1, Блок 2 предназначен для промежуточного хранения сообщений, подлежащих перемещению между процессора ми разных уровней иерархии вычислительной системы, согласование которых вып-олняет предлагаемое устройство. Применение блока 2 в предлагаемо устройстве позволяет компенсировать несоответствие скоростей обмена процессоров разных уровней и, тем самым обеспечивает повьпнение коэффициента их использования. На вход 23 (24) блока 2 с выхода 77.5 (элемента И 72). и блока 6 (фиг. 3) поступает сигнал управления обращением (затшсью). На вход 25 блока 2 с выхода счетчика 91 блока 8 (фиг. 5) поступает код адреса. Блоки 3.1-З.т и 4.1-4.т приема сообщений предназначены для временного хранения сообщений, в обмене .которыми участвует предлагаемое уст ройство. Сообщение блоков 3.1-З.т, 4.1-4.т с блоком 2 и внешними устройствами, например процессорами, осуществляется через коммутаторы 5.1-5.т данных (фиг. 2). Блоки 3.1З.т, 4.1-4.т могут быть вьшолнены на типовых интегральных элементах, например, 541РУ1.. О&ращение к блокам 3.1-З.т, 4.1-4.т производится по адресу, поступающему с выходов 27 и 31 коммутатора 9 адреса (фиг.1 и 6) соответственно. Тип вьтолняемой операции (чтение, запись) задается .на выходах коммутаторов обращения 10 (фиг. 7) и записи 11 (фиг. 8). На выход 28 (32) .блока 3.1 (4.1) (1е 1, ш) поступает сигнал обраще ния с одноименного выхода коммутатора 10 (фиг. 7). На вход 29.1 (33.1) блока 3.1 (4.1) поступает сигнал записи с одноименного выхода коммутатора 11 (фиг. 8). При наличии сигнала обращения и отсутствии сигнала записи происходит чтение информации, а при наличии сигналов обращения и записи происходит запись информации. Коммутаторы 5.1-5.т данных (фиг.2) предназначены для образования трактов двусторонней передачи информации между блоками 3.1-З.т, 4.1-4.т хранения сообщений с одной стороны и внешними (через тины 19.1-19.т) и внутренними (через шины 35.1-35.т) источниками и приемниками сообщений. Алгоритм функционирования коммутатора 5.1 (i 1, m) описывается в табл. 1, в которой задан полный набор кодов для всех возможных конфигураций коммутаций (символом обозначено безразличное состояние сигнала). Блок 6 микропрограммного управления (фиг. 3) предназначен для управления работой блоков и узлов предлагаемого устройства. В узле 63 хранятся микропрограммы работы устройства. Считывание информации из блока 63 осуществляется по адресу, заданному в регистре 64. Операционная часть микрокоманды по импульсу с входа 42.4 блока 6 заносится в регистр 65. немодифицируемые разряды адресной части микрокоманды поступают на второй информационный вход коммутатора 67, модифицируемый разряд адреса подается на информационный вход мультиплексора 66 логических условий, которьй формирует истинное значение модифицируемого разряда адреса, поступающего также на вход коммутатора 67. Код проверяемых логических условий с выхода блока 63 поступает на адресный вход мультиплексора 66. На первую группу информационных входов коммутатора 67 подается код операции с выхода 22 (фиг. 1) блека 1 памяти команд. Мультиплексор 66 реализует логическуго функцию + X -Вн е-1 Убб где Х. - код, определяющий прохождение на выход у значения модифицируемого разряда а без изменений; Xjj.. X - коды, предопределяющие npo хождение на вьйсод мультиплексора 66 соответствующе сигнала Zj,..., Zj. логиче кого УСЛОВИЯ (переполнения с выходов 36 счетчиков 93. 93.В блока 8 (см. фиг. 5) Коммутатор 67 управляет поступле нием адресной информации в регистр 64 (фиг. 3) При наличии сигнала на выходе 75 регистра 65 адрес микр команды определяется кодом реализуе мой операции, поступающим с входа 22блока 6 (выхода 22 блока 1). При вьшолнении микрокоманд микропрограм мы операции сигнала на выходе 75 равен нулю и адрес очередной микрокоманды определяется по адресу, счи тываемому из блока 63. Регистр 65 предназначен для хранения операционных частей i-шкрокоманд. С выхода 76 на вход 41 блока синхронизации (фиг. 4) поступает сигнал окончания работы. С выхода 77.1на вход 52 дешифратора 15 выбора канала (фиг. 1) поступает сигнал синхронизации для разрешения вьщачи информации из блока 5.1 на магистраль 16 данных. С выхода 77.2 поступает сигнал разрешения обращения на вход 20 блока 1 (фиг. 1). С выходов 77.3 и 77.4 вьщаются управляющие сигналы на входы 50 и 51 ком мутатора 13 магистралей (фиг. 10). С выхода 77.5 вьщается сигнал микро операции разрешения обращения на вх 23блока 2 (фиг. 1), ас выхода 78 через элемент И 72 на вход 24 блока 2 вьщается сигнал микрооперации записи. С выхода 79 регистра 65 на вход 38 коммутатора 10 обращения (фиг. 7) поступает сигнал разрешения о.бращения. По выходам 80.1 и 80.2дешифратора 68 в счетчиках 93.1-93.2 (фиг. 5) осуществляется запись или увеличение их значения через соответствующие входы 99.1 и 99.2 (фиг. 5). С выхода 81.1 (81.2) на вход 98.1 (98.2) поступает сигнал синхро низации записи (увеличения значения счетчика 32. С выхода 82.1 (82.2) на вход 97,1 (97.2) счетчика 91 поступает сигнал синхронизации записи (увеличения значения). С выход 83 (84) элемента И 73 (74) на вход 100 (101) регистра 94 (95) поступае сигнал разрешения записи. С выхода 85.1 (85.2) на вход 96.1 (96.2) счетчика 90 поступает сигнал разрешения записи (увеличения значения). С выхода 86 регистра 65 (фиг. 3) на первый вход коммутатора 12 управляющих сигналов (фиг. 9), а также на вход V 1 дешифратора 14 записи подается сигнгш разрешения внешнего доступа, который определяет режим записи в блок 3.1 (4.1) . На входы 42.1, 42.3 и 42.4 блока 6 (фиг. 3) поступают первый, третий и четвертый синхроимпульсы с выхода блока 7 синхронизации (фиг. 1 и 4). Блок 7 синхронизации (фиг. 4) предназначен для синхронизации работы всех узлов и блоков устройства. I Триггер 88 служит для управления работой блока 7 синхронизации. В исходном состоянии триггер 88 на ходится в нулевом состоянии. Нулевой сигнал на его единичном выходе поступает на вход управления генератора 87. Генератор 87 формирует на своих выходах 42.1-42.4 четыре последовательности сдвинутых друг относительно друга импульсов только при наличии единичного сигнала на его упрарляющем входе. Элемент И 89 служит для формирования сигнала на R-вход триггера 88 после поступления управляющего сигнала Конец работы с выхода 41 блока 6 микропрограммного управления. После поступления сигнала Пуск на вход 17 устройства последний подается на S-вход триггера 88 и устанавливает его в единичное состояние. Единичным сигналом на своем выходе триггер 88 запускает генератор 87, который начинает формирование последовательностей управляющих сигналов. Формирование синхросигналов продолжается до тех пор, пока на первый вход элемента И 89 не поступает управляющий сигнал Конец работы. После этого при поступлении на второй вход элемента И 89 очередного тактового импульса с выхода 42.4 генератора 87 формируется управляющий сигнал на R-вход триггера 88, который возвращается в исходное состояние и снимает управляющий сигнал с входа генератора 87, В результате этого генератор 87 прекращает вьвдачу сикхропоследовательностей. Коммутатор 9 адреса (фиг. 6) предназначен для коммутации адреса 15 блоков 3.1-3.m, 4.1-4.га приема сооб щений, который может поступать извн на вход 18 или на вход 43 с одноиме ного выхода счетчика 92 блока 8 (фиг. 5). Выбор группы блоков 3.1З.т или 4.1-4.т для вьщачи соответствующих адресов на их адресные входы осуществляется управляюпц м сигналом, который поступает с выход первого разряда регистра 95 (фиг.5) на управляющий вход 44 коммутатора. 9 (фиг. 6). Коммутатор 10 обращения (фиг.7) предназначен для коммутации сигнала обращения, поступающего с выхода 38 блока 6 (фиг. 3) или с разряда обращения группы входов 18 устройства. Выбор групп блоков 3.1-З.т или 4.1-4.m для вьщачи соответствующих обращений на их первые управляющие входы осуществляется аналогично опи санном для блока 9. Коммутатор 11 записи (фиг. 8) предназначен для формирования сигна ла записи в блоки 3.1-З.т, 4.1-4.т. Выбор блоков 3.J (4.j)(j 1, m) осуществляется по коду с выхода 45 блока 8 дешифрированному дешифратором 14 записи и выдающим сигнал при наличии сигналов на его входах V 1 и V 2 в j-й разряд выхода 48 дешифратора 14 записи, идентификация одного из блоков 3.J или 4.J производится сигналом с первого раз ряда выхода 44 регистра 95 блока 8 (фиг. 5). Элемент И 108 предназначен для формирования управляющего сигнала записи, поступающего с группы входов 18 по входу 47, стробируемого синхроимпульсом с выхода 42.2 блока 7 синхронизации (фиг.4). Коммутатор 12 управляющих сигналов (фиг. 9) предназначен для управ ления работой коммутаторов данных 5.1 (i 1, m). На вход 40 (47) коммутатора 12 поступает-сигнал раз рещения внешнего доступа, разрешающего запись, с выхода блока 6 (разрешения записи извне). Функционирование коммутатора 12 управляющих сигналов (фиг. 9) описывается в табл. 2 ( обозначено безразличное состояние). Десять состояний коммутатора 12 управляющих сигналов приведенные в табл. 2 обеспечивают (совместно с сигналами на выходах 53.1 дешифра016тора 15 выбора канала) полный объем функционирования ком 1утатора 5.1 данных в соответствии с табл. 1. Коммутатор 13 магистралей (фиг.10) предназначен для коммутации передачи информации между магистралью 16 (фиг. 1) и входами-выходами 22. При наличии сигнала на входе 50 осуществляется передача информации с входов-выходов 22 в магистраль 16, при отсутствии сигнала на входах 50 и 51 первая и вторая группы входов-выходов коммутатора 13 магистралей находятся в высокоимпедансном состоянии. При наличии сигнала на входе 51 коммутатора 13 магистралей осуществляете передача информации из магистрали 16 данных на вход-выход 22 коммутатора 13. Рассмотрим функционирования предлагаемого устройства. Устройство осуществляет обмен сообщениями между процессорами разных уровней вычислительной системы, а также накопление и хранение сообщений в блоке 2 памяти и в блоках 3.1-З.т и 4.1-4.т. Использование блоков 3.1 и 4.1 в каждом канале устройства позволяет совместить процессы ввода, вывода и обработки информации в многоуровневой вычислительной системе, где может быть применено устройство. Для этого один из блоков обмена сообщениями 3.1 (4.1) может осуществлять обмен сообщениями, например ввод их через щину 19.1 с внешнего процессора. В то же время устройство может осуществлять обмен информацией, например вывод или ввод сообщений, введенных рассматриваемым внешним процессором в блок 4.1 (3.1), на предыдущем этапе работы через коммутатор 5.1 данных, щину 35.1, магистраль 16 и щину 26 в блок 2 буферной памяти. Причем, поскольку обмен с внешним процессором осуществляется в процессе обработки им информации, а обмен с блоком 2 в процессе сканирования, то время обмена с процессором намного превосходит время обмена с блоком 2 для одного и того же канала. Если для числа внешних процессоров (абонентов) m и времен обмена одного канала с соответствукицим процессором ОЬм блоком 2 t справедливо соотношение ТО предлагаемое устройство обес.пе.чнвает работу m процессоров без потерь времени на ввод-вывод сообщений. Направления обмена информацией прокладываются коммутаторами 5.15,га в соответствии с табл. 1 и 2. Состояниям, указанным в табл. 1, соответствуют режимы работы устройства по управлению обменом сообщениями. Кроме того, устройство может управлять обменом сообщениями между процессорами, подключенными к шинам 19.1-19.m непосредственно либо через сеть передачи сообщений . При этом процессор i посыпает сообщения через коммутатор 5.1, шину 35.1, магистраль 16 и имну 26 в блок 2 буферной памяти, откуда может осуще ствляться пересыпка сообщения в блок 3.J (4.J) процессора - получателя сообщения, который, обратившис к данному блоку, может принять сооб щение. Это позволяет использовать предлагаемое устройство в вычислительной сети в качестве коммутацион ного устройства. Важной особенностью предлагаемог устройства является то, что програм ма его работы может считываться не только из блока 1 памяти команд, но также из блока 2 буферной памяти ил поступать от внешних процессоров. первом случае программа считывается с выходов 22 блока 1 (фиг. 1). Во втором случае программа с выходов блока 2 через шину 26, магистраль 1 группу магистральных элементов 114 (фиг. 10) блока 13 поступает на выходы 22 коммутатора 13. В третьем случае, вне-шний процессор может передать программу через шину 19.1 в блок 3.1 (4.1) через коммутатор 3.1, откуда она считывается под упр лением блока 6 по цепи: блок 3.1 (4.1), шина 30.1 (34.1), коммутатор 5.1, шина 35.1, магистраль 16, элементы 114 (фиг. 10) коммутатора 13, выходы 22 коммутатора 13 (фиг. 1). Использование второго и третьего ис точников программы работы устройства позволяет вьшолнять модификацию программ в случае необходимости изменения режимов обмена сообщения ил замены ошибочных (дефектных) участ- ков программ в блоке 1 памяти коман 00. 18 Пример. Рассмотрим функшюнирование устройства при обмене сообщениями между процессорами, подключенными к шинам 19.1 - 19,т и блоком 2 через блоки 3.1-3.га (4.14.т), в которых информация накапливается в процессе работы процессоров, подключенных через шины 19.1-19.т. В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии. Предположим, что устройству необходимо обеспечить обмен сообщениями между процессорами вычислительной системы, подключенными к шинам 19.1-19.т (фиг. 1), и блоком 2 буферной памяти. Для обеспечения начального функционирования этих процессоров осуществляется начальный ввод сообщений (данных) в блоки 3.1З.т (4.1-4.т) приема сообщений с . выхода блока 2 через шину 26, магистраль 16, иины 35.1-35.m , коммута-. торы 5.1-5.т и шины 30.1-ЗО.т (34.134.т). Выполнение указанного обмена происходит под управлением управляющих и коммутационных блоков устройства. При поступлении сигнала пуска на вход 17 устройства (фиг. 1) триггер 88 (фиг. 4) устанавливается в единичное состояние и включает генератор 87, который начинает формировать тактовую сетку импульсов, синхронизирующих работу устройства. В счетчике 90 команд (фиг. 5) задан адрес первой (нулевой) комавды программы управления обменом, хранящийся в блоке 1 памяти команд (фиг. 1). В исходном состоянии на выходе 77.2 присутствует единичньй потенциал, которьй через выходы 37 блока 6 (Фиг.З) поступает на вход 20 упраапения обращением блока 1 и разрешает тем самым считывание из блока 1 комаьады по адресу, поступающему на входы 21блока 1 (фиг. 1). С выхода 22 блока 1 считывается первая команда программы работы устройства, код операции которой поступает на входы 22блока 6 (фиг. 3) и записывается через коммутатор 67 по тактовому импульсу с входа 42.1 в регистр 64, содержимое которого задает адрес первой микрокоманды выполнения операции обмена в узле 63 памяти микропрограммы. В зависимости от типа выполняемой операции обмена (режима обмена) в последующих микрокомандах может задаваться считывание из блок 1 и, запись соответствующих констант в счетчики и регистры блока 8 (фиг При этом адрес считываемой информации задается счетчиком 90 блока 8 (фиг. 5), считывание разрешается сигналом микрооперации с выхода 77 блока 6 (фиг. 3), поступающей на вход 20 блока 1 (фиг. 1). Адресат определяется сигналом микрооперации с выходов 80.1, 80.3,...B0.2t-1, 81.1,82.1, 83,84 или 85.1 блока 6 (фиг. 3), поступаюпщм на один из соответствующих входов 99.1, 99.3, ...,99.2е-1. 96.1, 97.1, 100, 101 и 96.1. Выполнение указанных действий позволяет записать адрес команды в счетчик 90 (фиг. 5); адрес сообщения (данных) в блоке 2 счетчика 91; адрес сообщения в одном из блоков ,3.1-3.т (.4.1-4.т); код дополнения в счетчик 1д;икпов 93.j (j 6 1,К ); код номера канала в регистр 94; код выбора блока 3.1 или 4.1 в канале в регистр 95. Приращение значений счетчиков 90-93 блока 8 (фиг. 5) осуществляет ся по сигналам микроопераций, посту пающим с выходов 85.2, 82.2, 81.2, 80.2,80.4,..., 80.26 блока 6 (фиг. 3) на соответствующие входы 96.2, 97.2, 98.2, 99.2, 99.4,..., 99.2 6 блока 8 (фиг. 5). Рассмотрим порядок записи информации с шины 19.1 в блок 3.1 приема сообщений и одновременного считывания из блока 4.1 в блок 2 буферной памяти. В этом случае адрес записи (считьюания) сообщений в (из) блок 3.1 (блока 4.1) может задаваться с входа 18 устройства (фиг. 1) (сче чиком 92 блока 8). Задание адреса с входа 18 устройства осуществляет процессор высшего уровня по отношению к процессору, подключенному к шине 19.1. Состояние входных и выходных сигналов, а также направления передачи сообщений блоков 12 и 15.1 описывается в табл. 1 и 2 (состояния i oi 3 и В 3) . На вход 45 дешифратора 15 (фиг. 1) с выхода регистра 94 (фиг. 5) поступает код номера 1-го канала, который по мик рооперации с выхода 77.1 (фиг. 3) блока 6, поступающей на вход 52 блока 15, вьщает сигнал на вькоде ;53.1. Кроме того, код 1-го канала с выхода 45 блока 8 (фиг. 5) поступает на дешифратор 14 (фиг. 1),который по микрооперации с выхода 40 блока 6 (фиг. 3) выдает сигнал с 1-го выхода 48 на одноименньй вход блока 11 (фиг. 8) только в режиме записи данных из блока 2 в бЛок 4.1. По этому сигналу срабатывает соответствующий коммутатор 106.1 и выдает сигнал разрешения записи на вход 29.1 блока 3.1. В нашем же случае при чтении из блока 4.1 сигнал на выходе 40 блока 6 не вырабатывается, а вырабатывается только сигнал обращения на выходе 38 блока 6. I. . Адреса записи в блок 3.1 и чтения из блока 4.1 формируются следующим образом. Адрес записи сообщения поступает с входа 18 устройства через коммутатор 9 адреса на его выход 27, а с выхода 43 блока 8 на вькод 31 блока 9 (фиг. 6), в котором при единичном значении первого разряда выхода 44 регистра 95 коммутатор 102 передает адрес записи с входа 18 устройства через выход 27 коммута|тора 9 на одноименный вход блока 3.1, а адрес чтения сообщения, поступающий в коммутатор 9 (фиг. 6) с выхода 43 блока 8, передается на выход 31 коммутатора 9 с помощью коммутатора 103 (фиг. 6), так как сигнал на его входе 44 равен единице. На вход 32 блока 4.1 с одноименного выхода коммутатора 10 (фиг. 7) поступает сигнал разрешения обращения. Этот сигнал формируется коммутатором 105 блока 10, который передает на выход 32 сигнал с входа 38 и одноименного выхода блока 6 (фиг. 1). Адрес, по которому записывается в блок 2 сообщение из блока 4.1, формируется на входе 25 блока 2 счетчиком 91 блока 8 (фиг. 5).Сообщение из блока 4.1 передается в блок 2 через шину 34.1, блок 5.1, шину 35.1, магистраль 16 и шину 26, при этом сигналы обращения и записи на входы 23 и 24 блока 2 поступают с выходов 77.5 регистра 65 и элемента И 72 (фиг. 3). Для записи информации, поступающей в блоки 3.1 (1 1,2,..., га) с шин 19.1 на вход 46коммутатора 10 поступает сигнал с группы входов 18, по которому на выходе 28 коммутатора 10 вырабатывается сигнал обращения, а на вход 47коммутатора 11 записи поступает I сигнал разрешения записи, по котор му в момент поступления сигнала на СИ1ГХРОВХОД коммутатора 11 с выхода 42.2 блока 7 на вькодах 29.1 (i 1,2,..., m) вьграбатывается си нал записи в блоки 3.1. По окончании выполнения програм мы формируется микрооперация окончания работы на выходе 76 (41) бло ка 6 (фиг. 3), по которой триггер 88 (фиг. 4) блока 7 устанавливается в нуль и отключает генератор 87. Технико-экономическая эффективность данного устройства заключаетс в следующем. Предлагаемое устройство превосхо дит известное по быстродействию, чт можно оценить величиной ДТ, равной разности суммарного среднего времени одного цикла работы i-ro канала (iel, m) известного Т. и изобрете ния по формуле лт т,,. Причем величина Т оценивается выражением : ,Г п,ах tj, t-, Подставив выражения (1) и (3) в (2), получим | 4 K- 4Sri l Относительный выигрыш в производительности на одно повторение цикл ввода-вывода 8 Т при использовании изобретения составляет величину, оц ниваемую по формуле Z.lj + ijc-max(ij, -lOOVo -,t t)H Положив tj tjc 0,510 c, k 2 получим ST 50%. Таким образом, пре.ялагаемое устройство превосходит известное и базовы объект по быстродействию в среднем на 50%. Предлагаемое устройство превосходит базовый объект по области применения, так как обеспечивает произвольньй порядок записи и считывания сообщений в каналы, а также опроса каналов; допускает реализацию гибкой, изменяемой программно-микропрограммными средствами дисциплины обмена сообщениями и позволяет, благодаря использованию блока буферной памяти, осуществить согласование по быстродействию работы процессоров вычислительной системы, которые производят обмен сообщениями с помощью предлагаемого устройства, этим достигается снижение времени простоя процессоров системы и повышению коэффициента их использования. Предлагаемое устройство может организовать обмен сообщениями между процессорами, подкпюченньми к его внешним шинам 19.1-19.m непосредственно либо через сеть передачи сообщений, при этом такт обмена прокладьшается из соответствующего блока хранения сообщений - источником через коммутационные и транслирующие узлы устройства в блок буферной памяти, из которого сообщенке пересылается аналогичным образом в блок хранения сообщений - приемника. Это позволяет использовать предлагаемое у стройство в вычислительной сети в качестве коммуникационного устройства (процессора) обмена. Предлагаемое устройство обладает также большей надежностью по сравнению с базовым объектом, так как опускает возможность распределения ли концентрации программ функциониования по трем источникам: блок памяти команд, блок буферной памяти или внешние процессоры. Ввиду этого в устройстве возможна модификация или замена программ в случаях изменения режимов обмена сообщениями, а также появления дефектных участков (команд) в блоке памяти команд.

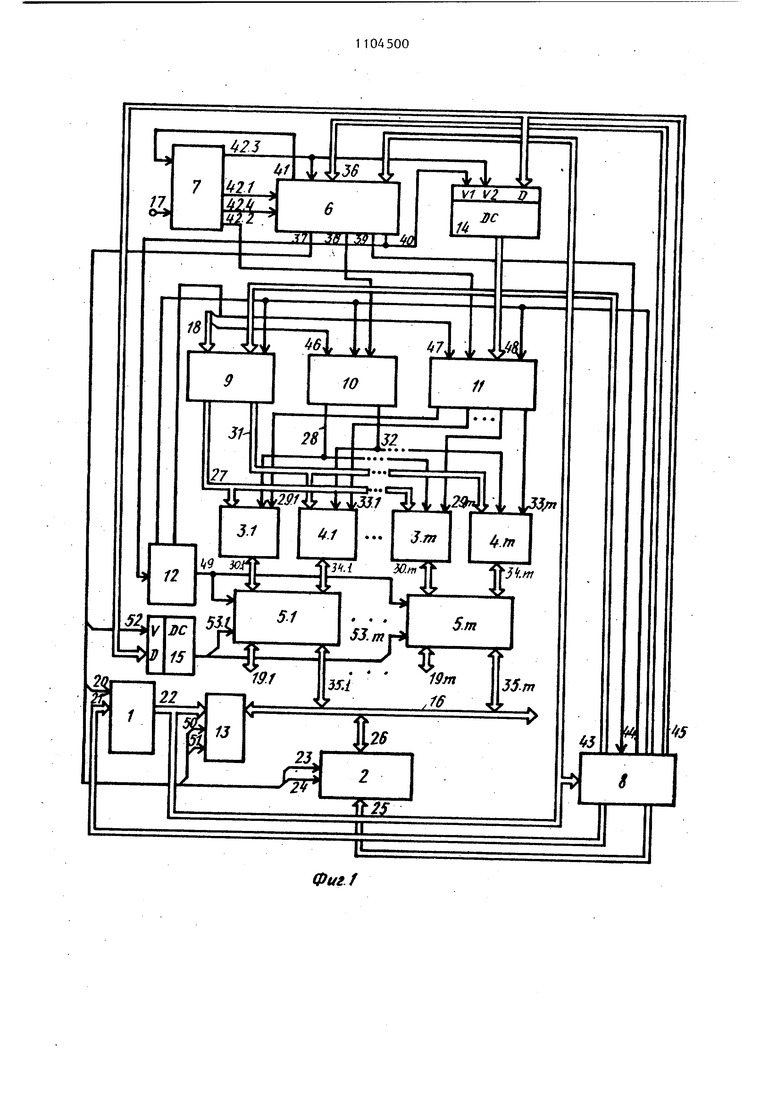

jT а, б л и ц а 1

Фиг./

.

Фиг.з

Ф«г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

1. МНОГОКАНАЛЬНОЕ ШКРОПРОГРАММНОЕ УСТРОЙСТВО ВВОДА-ВЫВОДА, содержащее блок синхронизации, коммутатор обращений, коммутатор записи, первую и вторую группы блоков приема сообщений, блок счетчиков, дешифратор выбора канала и блок управления, первый выход которого соединен с синхровходом дешифратора выбора канала, второй выход блока управления соединен с первым входом коммутатора обращений, второй вход которого соединен с выходом блока счетчиков, выходы первой группы которого соединены с входами первой группы блока управления, первый вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом коммутатора записи, вы- ходы первой группы которого соединены с первыми входами блоков приема сообщений первой группы, вторые входы которых соединены с первым выходом коммутатора обращений, второй выход которого соединен с первыьи входами блоков приема сообщений второй группы, вторые входы которых соединены с выходами второй группы коммутатора записи, третий и четвертый выходы блока синхронизации соединены соответственно с вторым и третьим входами блока управления, третий выход которого соединен с nepabtM входом блока синхронизации, выходы второй группы блока счетчиков соединены с информационными входами дешифратора выбора канала, второй вход коммутатора записи соединен с вторым входом коммутатора обращений, выходы группы блока управления соединены с входами первой грзт1пы блока счетчиков, второй вход блока синхронизации является первым входом устройства, третий вход коммутатора ббращений является вторым входом устройства, третий вход коммутатора записи является третьим входом устройства, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введены коммутатор управляющих сигналов, блок памяти команд, блок буферной памяти, коммутатор магистралей, дешифратор записи, первый коммутатор адреса и коммута.торы данных, входы первой группы кой торьк соединены с выходами коммутатора управляющих сигналов, первый ел вход которого соединен с четвертым выходом блока управления и с первым входом дешифратора записи, второй вход которого соединен с вторым вхЬдом блока управления, входы второй группы которого соединены с входами второй группы блока счетчиков, с входами-выходами первой группы коммутатора магистралей и с выходами блока памяти команд, входы группы которого соединены с выходами третьей группы блока счетчиков, выходы четвертой группы которого соединены с адресными входами блока буферной па

27

.6

1

JZ

7 2Z

-tt

«

/a7.f f

т.

L..

25/

0i/e.7 ftS

«V о

/

Г(/7я1 /

/(75. m r

j5./rt

5/n

/e. J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU615472A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1980 |

|

SU941979A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-20—Подача