Изобретение относится к вычислительной технике и может найти применение в системах числового программного управления станками, чертежным оборудованием и другим оборудованием в котором необходимо осуществлять круговую интерполяцию, Целью изобретения является повышение быстродействия и уменьшение в два раза разрядности устройства.

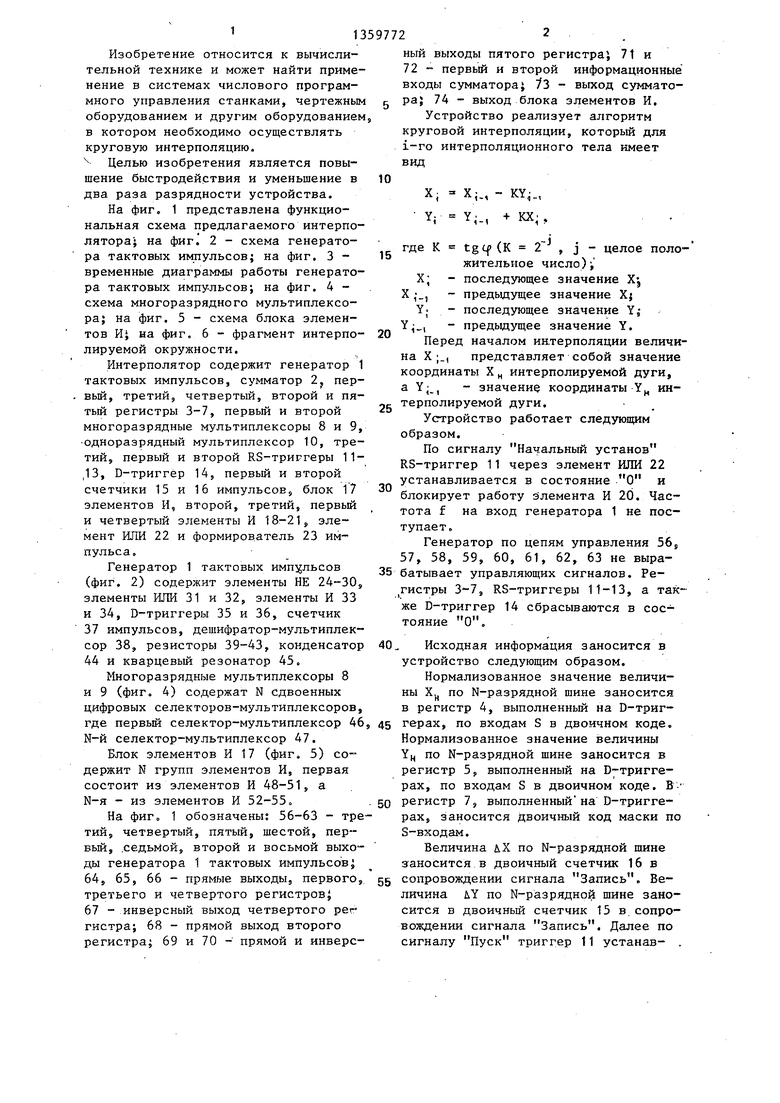

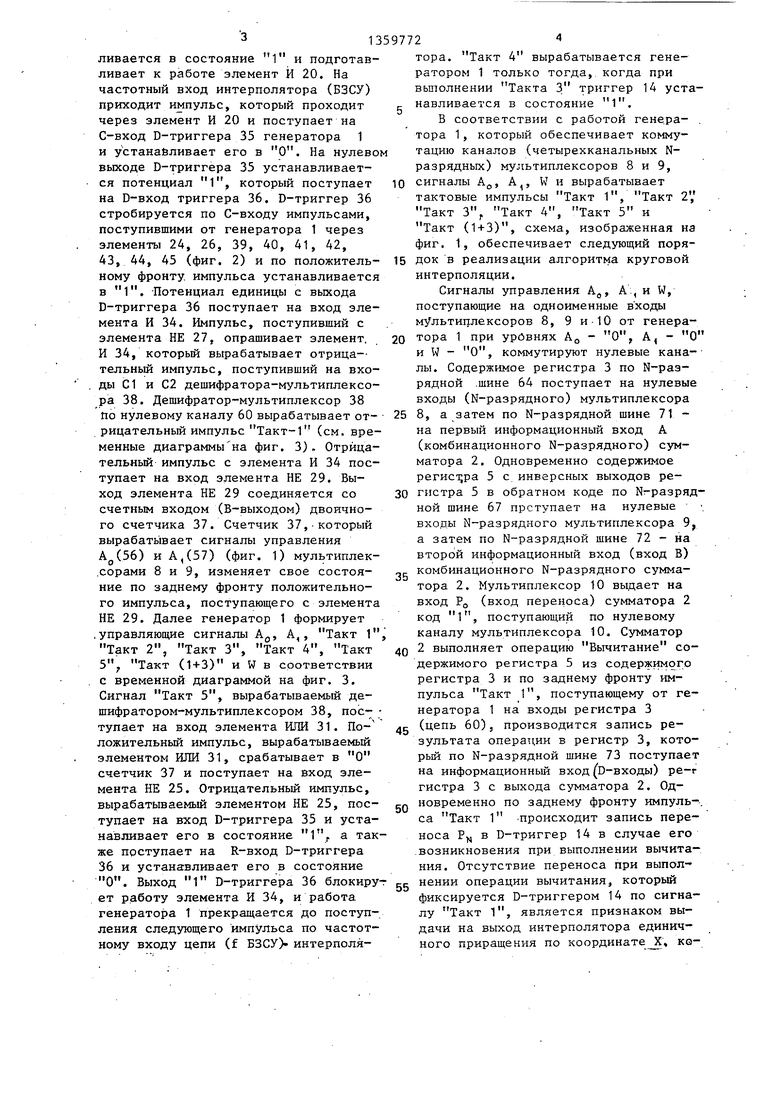

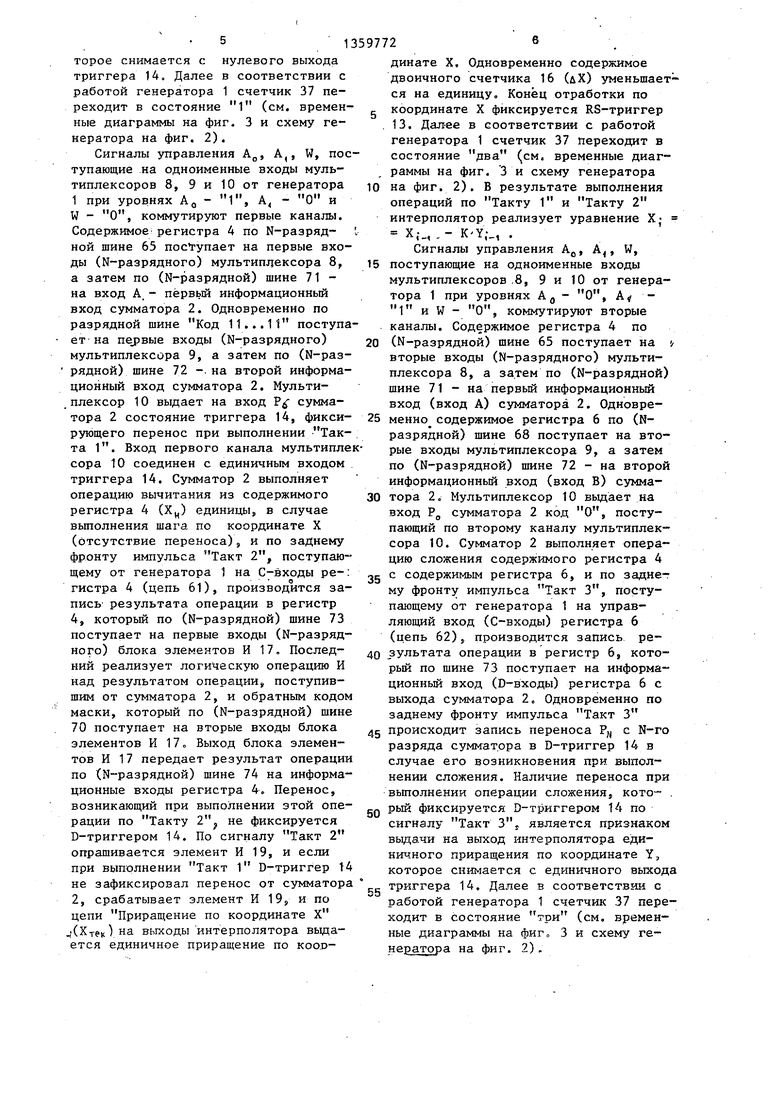

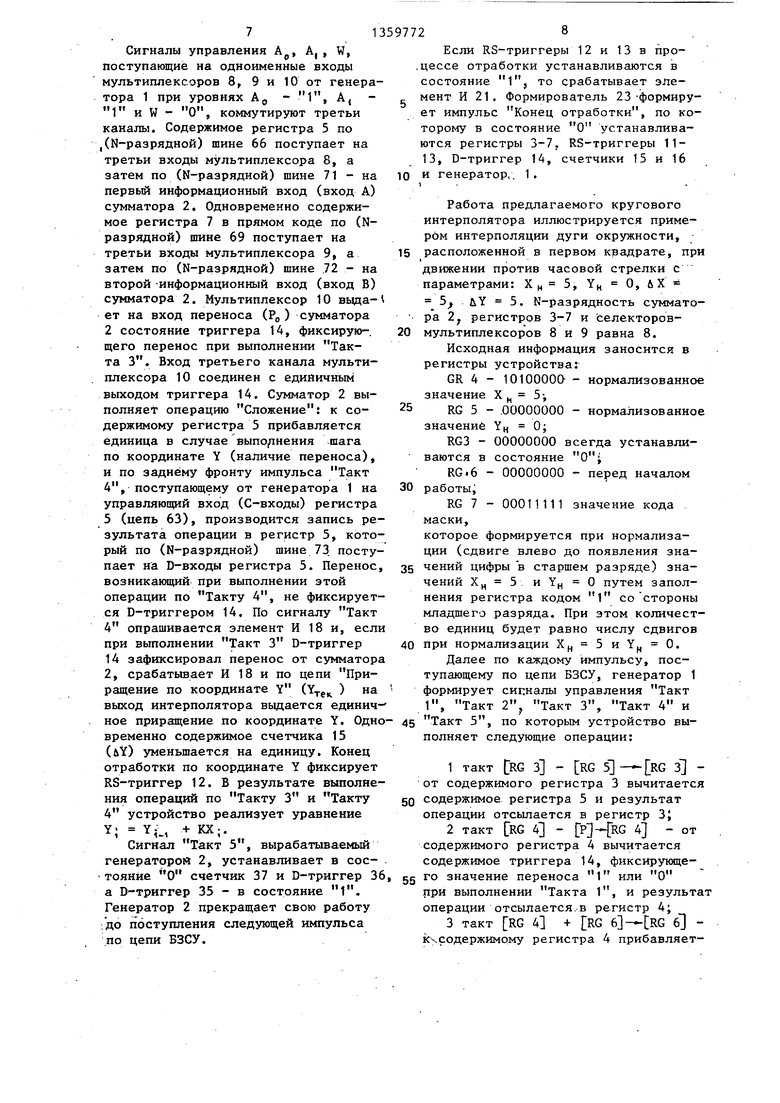

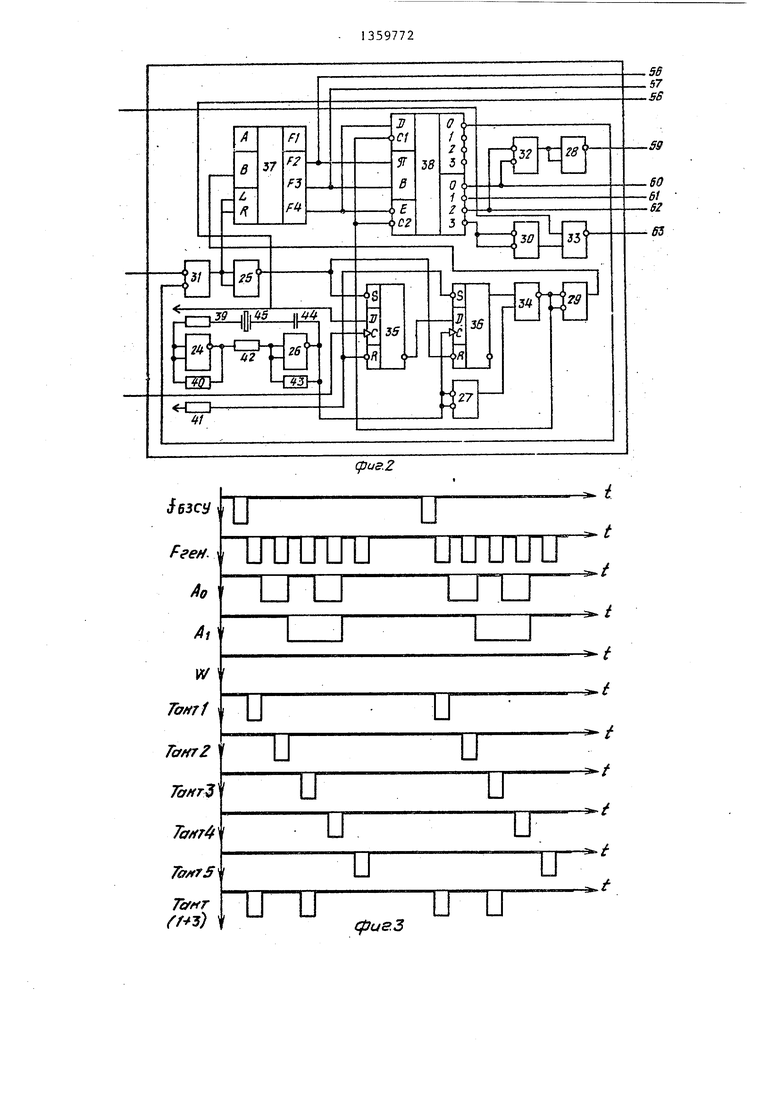

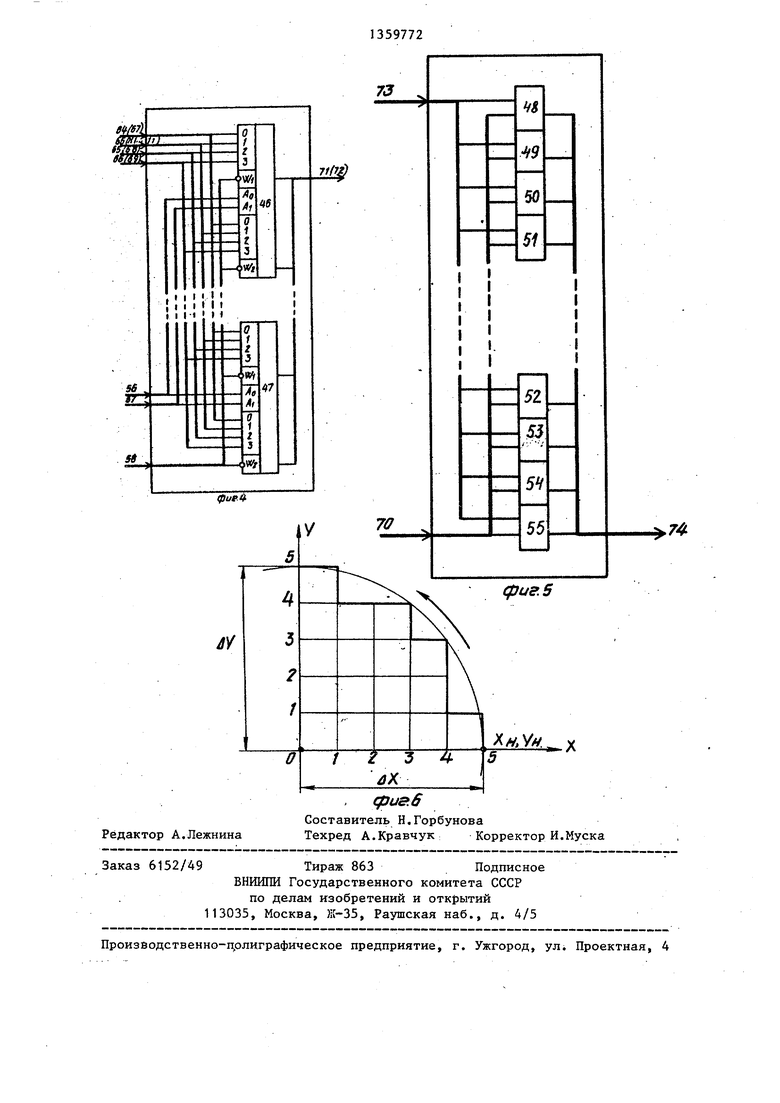

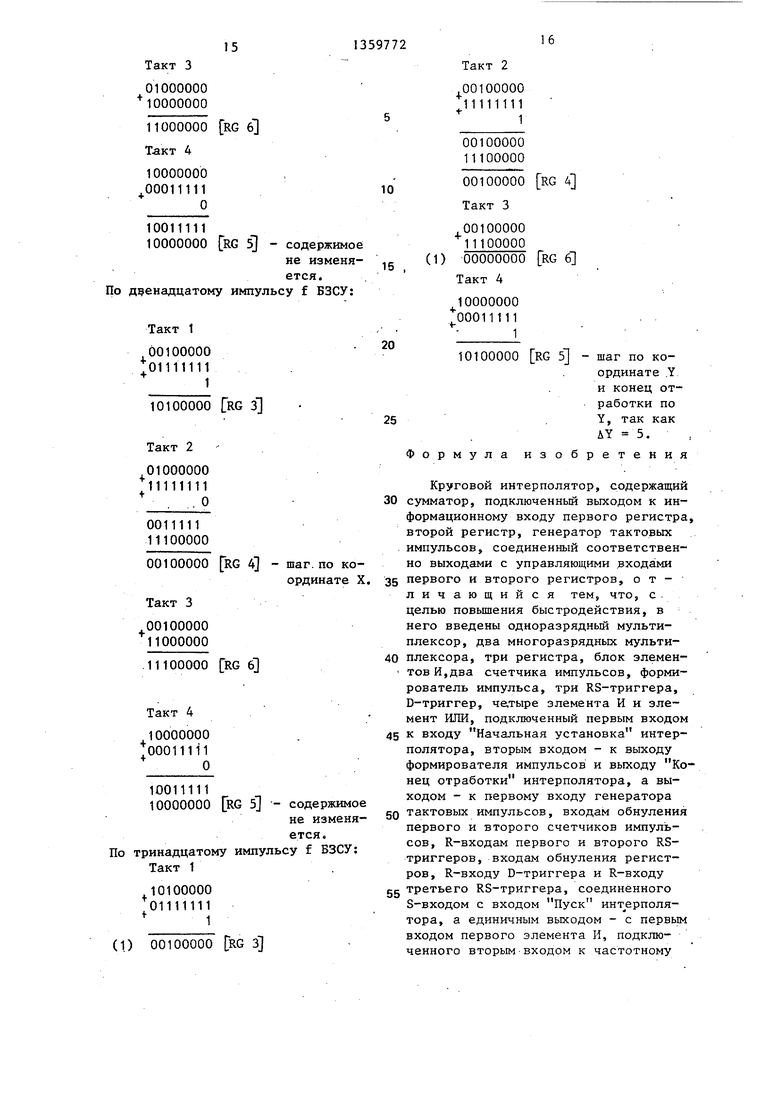

На фиг. 1 представлена функциональная схема предлагаемого интерполятора; на фиг 2 - схема генератора тактовых импульсов; на фиг, 3 - временные диаграммы работы генератора тактовых импульсов; на фиг. 4 - схема многоразрядного мультиплексора; на фиг. 5 - схема блока элементов Hi на фиг, 6 - фрагмент интерполируемой окружности.

Интерполятор содержит генератор 1 тактовых импульсов, сумматор 2, пер- вьй, третий, четвертый, второй и пятый регистры 3-7, первый и второй многоразрядные мультиплексоры 8 и 9, одноразрядный мультиплексор 10, третий, первый и второй RS-триггеры 11- ,13, D-триггер 14, первый и второй счетчики 15 и 16 импульсов, блок 17 элементов И, второй, третий, первьй и четвертый элементы И 18-21, элемент ИЖ 22 и формирователь 23 импульса,

Генератор 1 тактовых импз льсов (фиг, 2) содержит элементы НЕ 24-30, элементы ИЛИ 31 и 32, элементы И 33 и 34, D-триггеры 35 и 36, счетчик 37 импульсов, дешифратор-мультиплексор 38, резисторы 39-43, конденсатор 40 Исходная информация заносится в

44 и кварцевый резонатор 45.

Многоразрядные мультиплексоры 8 и 9 (фиг. 4) содержат N сдвоенных цифровых селекторов-мультиплексоров,

где первьй селектор-мультиплексор 46, 45 герах, по входам S в двоичном коде.

N-Й селектор-мультиплексор 47,

Блок элементов И 17 (фиг, 5) содержит N групп элементов И, первая состоит из элементов И 48-51, а N-я - из элементов И 52-55.

На фиг. 1 обозначены; 56-63 - третий, четвертый, пятый, шестой, пер- вьй, .седьмой, второй и восьмой выходы генератора 1 тактовых импульсов; 64, 65, 66 - прямые выходы, первого, третьего и четвертого регистров 67 - инверсный выход четвертого per гистра; 68 - прямой выход второго регистра; 69 и 70 - прямой и инверсный выходы пятого регистра 71 и 72 - первый и второй информационные входы сумматора; УЗ - выход суммато- pa; 74 - выход блока элементов И, Устройство реализует алгоритм круговой интерполяции, который для i-ro интерполяционного тела имеет вид

X:

Х,., - KY,

Y: Y:

+ КХ:

5

где К

0-J

X

0

X;1-1

у.i-i

tgcp (К , J - целое положительное число); последующее значение Х , предыдущее значение Xj последующее значение У,- предьодущее значение У, Перед началом интерполяции величина X;., представляет собой значение координаты Х„ интерполируемой дуги, а У;, - значение координаты У„ ин- с терполируемой дуги.

Устройство работает следующим образом.

По сигналу Начальный установ RS-триггер 11 через элемент ИЛИ 22

30

устанавливается в состояние О и

блокирует работу элемента И 20. Частота f на вход генератора 1 не поступает,

Генератор по цепям управления 56j 57, 58, 59, 60, 61, 62, 63 не выра- 35 батывает управляющих сигналов. Ре- гистры 3-7, RS-триггеры 11-13, а также D-триггер 14 сбрасываются в состояние О.

устройство следующим образом.

Нормализованное значение величины Хц по N-разрядной шине заносится в регистр 4, выполненный на D-тригНормализованное значение величины Уц по N-разрядной шине заносится в регистр 5, выполненный на D-тригге- рах, по входам S в двоичном коде. В.

регистр 7, выполненный на D-тригге- рах, заносится двоичный код маски по S-входам.

Величина &Х по N-разрядной щине заносится в двоичный счетчик 16 в

сопровождении сигнала Запись. Величина дУ по N-разрядной шине заносится в двоичный счетчик 15 в.сопровождении сигнала Запись. Далее по сигналу Пуск триггер 11 устанав- .

ливается в состояние 1 и подготавливает к работе элемент И 20. На частотный вход интерполятора (БЗСУ) приходит импульс, который проходит через элемент И 20 и поступает на С-вход D-триггера 35 генератора 1 и устанайливает его в О. На нулево выходе D-триггера 35 устанавливается потенциал 1, который поступает на D-вход триггера 36. D-триггер 36 стробируется по С-входу импульсами, поступившими от генератора 1 через элементы 24, 26, 39, 40, 41, 42, 43, 44, 45 (фиг. 2) и по положитель- ному фронту, импульса устанавливается в 1. -Потенциал единицы с вьпсода D-триггера 36 поступает на вход элемента И 34. Импульс, поступивший с элемента НЕ 27, опрашивает элемент. И 34, который вырабатывает отрица-- тельньй импульс, поступивший на входы С 1 и С2 дешифратора-мультиплексора 38. Дешифратор-мультиплексор 38 По нулевому каналу 60 вырабатывает от- рицательный импульс Такт-1 (см. временные диаграммы на фиг. 3). Отрицательный импульс с элемента И 34 поступает на вход элемента НЕ 29. Выход элемента НЕ 29 соединяется со счетным входом (В-выходом) двоичного счетчика 37. Счетчик 37,-который вырабатывает сигналы управления A|j(56) и А,(57) (фиг. 1) мультиплек- .сорами 8 и 9, изменяет свое состоя- ние по заднему фронту положительного импульса, поступающего с элемента НЕ 29. Далее генератор 1 формирует .управляющие сигналы А, А,, Такт 1 Такт 2, Такт 3, Такт 4, Такт 5, Такт (1+3) и W в соответствии с временной диаграммой на фиг. 3. Сигнал Такт 5, вырабатываемый дешифратором-мультиплексором 38, пос- тупает на вход элемента ИЛИ 31. По- ложительный импульс, вырабатываемый элементом ИЛИ 31, срабатывает в О счетчик 37 и поступает на вход элемента НЕ 25. Отрицательный импульс, вырабатываемый элементом НЕ 25, пос- тупает на вход D-триггера 35 и устанавливает его в состояние Г% а также поступает на R-вход D-триггера 36 и устанавливает его в состояние О. Выход 1 D-триггера 36 блокиру ет работу элемента И 34, и работа генератора 1 прекращается до поступления следующего импульса по частотному входу цепи (f БЗСУ)« интерполятора. Такт 4 вырабатывается генератором 1 только тогда, когда при вьшолнении Такта 3. триггер 14 устанавливается в состояние 1.

В соответствии с работой гене.ра- тора 1, который обеспечивает коммутацию каналов (четырехканальных N- разрядных) мультиплексоров 8 и 9, сигналы Ад, А,, W и вырабатывает тактовые импульсы Такт 1, Такт 2, Такт 3 Такт 4, Такт 5 и Такт (1+3), схема, изображенная на фиг. 1, обеспечивает следующий порядок в реализации алгоритма круговой интерполяции.

Сигналы управления Ад, А., и W, поступающие на одноименные входы мультиплексоров 8, 9 и-10 от генератора 1 при уровнях АО - О, А, - О и W - О, коммутируют нулевые каналы. Содержимое регистра 3 по N-раз- рядной .шине 64 поступает на нулевые входы (N-разрядного) мультиплексора 8, а затем по N-разрядной шине 71 - на первый информационный вход А (комбинационного N-разрядного) сумматора 2. Одновременно содержимое perncTjpa 5 с инверсных выходов регистра 5 в обратном коде по Кт-разряд ной шине 67 прступает на нулевые входы N-разрядного мультиплексора 9, а затем по N-разрядной шине 72 - на второй информационный вход (вход В) комбинационного N-разрядного сумматора 2. Мультиплексор 10 выдает на вход РО (вход переноса) сумматора 2 код 1, поступающий по нулевому каналу мультиплексора 10. Сумматор 2 выполняет операцию Вычитание содержимого регистра 5 из содержимог;о регистра 3 и по заднему фронту импульса Такт 1, поступающему от генератора 1 на входы регистра 3 (цепь 60)5 производится запись результата операции в регистр 3, который по N-разрядной шине 73 поступает на информационный вход (D-входы) ре-г гистра 3 с выхода сумматора 2. Одновременно по заднему фронту импульса Такт 1 -происходит запись переноса Р в D-триггер 14 в случае его возникновения при выполнении вычитания. Отсутствие переноса при выполнении операции вычитания, который фиксируется D-триггером 14 по сигналу Такт 1, является признаком выдачи на выход интерполятора единичного приращения по координате, которое снимается с нулевого выхода триггера 14. Далее в соответствии с работой генератора 1 счетчик 37 переходит в состояние 1 (см. временные диаграммы на фиг. 3 и схему генератора на фиг. 2).

Сигналы управления А, А,, W, поступающие на одноименные входы мультиплексоров 8, 9 и 10 от генератора

13597726

динате X. Одновременно содержимое двоичного счетчика 16 (дХ) уменьшается на единицу. Конец отработки по координате X фиксируется RS-триггер 13, Дал-ее в соответствии с работой генератора 1 счетчик 37 переходит в

1 при уровнях АО - 1, А - О и W - О, коммутируют первые каналы. Содержимое регистра 4 по N-разряд- ; ной шине 65 поступает на первые входы (N-разрядного) мультиплексора 8, а затем по (N-разрядной) шине 71 - на вход А. - пёрвьгй информационный вход сумматора 2. Одновременно по разрядной шине Код 11...11 поступает на входы (N-разрядного) мультиплексора 9, а затем по (N-pas рядной) шине 72 -.на второй информационный вход сумматора 2. Мультиплексор 10 выдает на вход Р сумматора 2 состояние триггера 14, фиксирующего перенос при выполнении Такта 1. Вход первого канала мультиплексора 10 соединен с единичным входом . триггера 14. Сумматор 2 выполняет операцию вычитания из содержимого регистра 4 (Хц) единицы, в случае вьшолнения шага по координате X (отсутствие переноса), и по заднему фронту импульса Такт 2, поступающему от генератора 1 на С-входы ре-: гистра 4 (цепь 61), производится запись- результата операции в регистр 4, который по (N-разрядной) шине 73 поступает на первые входы (N-разрядного) блока элементов И 17, Последний реализует логическую операцию И над результатом операции, поступившим от сумматора 2, и обратным кодом маски, который по (N-разрядной) шине 70 поступает на вторые входы блока элементов И 17,, Выход блока элементов И 17 передает результат операции по (N-разрядной) шине 74 на информационные входы регистра 4. Перенос, возникающий при выполнении этой операции по Такту не фиксируется D-триггером 14. По сигналу Такт 2 опрашивается элемент И 19, и если при выполнении Такт 1 D-триггер 14 не зафиксировал перенос от сумматора ° 2, срабатывает элемент И 19, и по цепи приращение по координате X

„( выходы интерполятора вьща- ется единичное приращение по KOO.D-

состояние два (см. временные диаграммы на фиг. 3 и схему генератора

10 на фиг. 2). В результате выполнения операций по Такту 1 и Такту 2 интерполятор реализует уравнение Х- Х;, .- K Y;, .

Сигналы управления А, А, W,

15 поступающие на одноименные входы мультиплексоров .8, 9 и 10 от генератора 1 при уровнях Ад - О, А - 1 и W - О, коммутируют вторые каналы. Содержимое регистра 4 по

20 (N-разрядной) шине 65 поступает на вторые входы (N-разрядного) мультиплексора 8, а затем по (N-разрядной) шине 71 - на первый информационный вход (вход А) сумматора 2. Одновре25 менио содержимое регистра 6 по (N- разрядной) шине 68 поступает на вторые входы мультиплексора 9, а затем по (N-разрядной) шине 72 - на второй информационный вход (вход В) сумма30 тора 2. Мультиплексор 10 выдает на Р„ сумматора 2 код О,

вход PQ сумматора i код и , поступающий по второму каналу мультиплексора 10. Сумматор 2 выполняет операцию сложения содержимого регистра 4

25 с содержш-шм регистра 6, и по заднег му фронту импульса Такт 3, поступающему от генератора 1 на управ- ЛЯЮ1ЦИЙ вход (С-входы) регистра 6 (цепь 62) J, производится запись ре40 зультата операции в регистр 6, который по шине 73 поступает на информационный вход (D-ВХОДЫ) регистра 6 с выхода сумматора 2. Одновременно по заднему фронту импульса Такт 3

45 происходит запись переноса PJJ с N-ro разряда сумматора в D-триггер 14 в случае его возникновения при выполнении сложения. Наличие переноса при выполнении операции сложения} кото- .

CQ рый фиксируется D-триггером 14 по сигналу Такт является признаком выдачи на выход интерполятора единичного приращения по координате Y, которое снимается с единичного выхода триггера 14. Далее в соответствии с работой генератора 1 счетчик 37 переходит в состояние три (см. временные диаграммы на фиг„ 3 и схему ге- нератора на фиг. 2).

55

состояние два (см. временные диаграммы на фиг. 3 и схему генератора

на фиг. 2). В результате выполнения операций по Такту 1 и Такту 2 интерполятор реализует уравнение Х- Х;, .- K Y;, .

Сигналы управления А, А, W,

поступающие на одноименные входы мультиплексоров .8, 9 и 10 от генератора 1 при уровнях Ад - О, А - 1 и W - О, коммутируют вторые каналы. Содержимое регистра 4 по

(N-разрядной) шине 65 поступает на вторые входы (N-разрядного) мультиплексора 8, а затем по (N-разрядной) шине 71 - на первый информационный вход (вход А) сумматора 2. Одновременио содержимое регистра 6 по (N- разрядной) шине 68 поступает на вторые входы мультиплексора 9, а затем по (N-разрядной) шине 72 - на второй информационный вход (вход В) сумматора 2. Мультиплексор 10 выдает на Р„ сумматора 2 код О,

вход PQ сумматора i код и , поступающий по второму каналу мультиплексора 10. Сумматор 2 выполняет операцию сложения содержимого регистра 4

с содержш-шм регистра 6, и по заднег му фронту импульса Такт 3, поступающему от генератора 1 на управ- ЛЯЮ1ЦИЙ вход (С-входы) регистра 6 (цепь 62) J, производится запись результата операции в регистр 6, который по шине 73 поступает на информационный вход (D-ВХОДЫ) регистра 6 с выхода сумматора 2. Одновременно по заднему фронту импульса Такт 3

происходит запись переноса PJJ с N-ro разряда сумматора в D-триггер 14 в случае его возникновения при выполнении сложения. Наличие переноса при выполнении операции сложения} кото- .

рый фиксируется D-триггером 14 по сигналу Такт является признаком выдачи на выход интерполятора единичного приращения по координате Y, которое снимается с единичного выхода триггера 14. Далее в соответствии с работой генератора 1 счетчик 37 переходит в состояние три (см. временные диаграммы на фиг„ 3 и схему ге- нератора на фиг. 2).

Сигналы управления А, А, , W, поступающие на одноименные входы мультиплексоров 8, 9 и 10 от генератора 1 при уровнях Ар - 1, А, - 1 и W - О, коммутируют третьи каналы. Содержимое регистра 5 по ,(N-paзpяднoй) шине 66 поступает на третьи входы мультиплексора 8, а затем по (N-разрядной) шине 71 - на первый информационный вход (вход А) сумматора 2. Одновременно содержимое регистра 7 в прямом коде по (N- разрядной) шине 69 поступает на третьи входы мультиплексора 9, а затем по (N-разрядной) шине 72 - на второй -информационный вход (вход В) сумматора 2. Мультиплексор 10 вьщает на вход переноса (Р) сумматора 2 состояние триггера 14, фиксирую-, щего перенос при выполнении Такта 3. Вход третьего канала мультиплексора 10 соединен с единичным выходом триггера 14. Сумматор 2 выполняет операцию Сложение : к содержимому регистра 5 прибавляется единица в случае выпо;1нения шага по координате Y (наличие переноса), и по заднему фронту импульса Такт 4, поступающему от генератора 1 на управляющий вход (С-входы) регистра 5 (цепь 63), производится запись результата операции в регистр 5, который по (N-разрядной) шине 73. поступает на D-входы регистра 5. Перенос, возникающий при выполнении этой операции по Такту 4, не фиксируется D-триггером 14. По сигналу Такт 4 опрашивается элемент И 18 и, если при вьшолнении Такт 3 D-триггер 14 зафиксировал перенос от сумматора 2, срабатьюает И 18 и по цепи Приращение по координате Y (Yyg ) на выход интерполятора выдается единичДалее по каждому импульсу, поступающему по цепи БЗСУ, генератор 1 формирует сигналы управления Такт 1, Такт 2, Такт 3, Такт 4 и

ное приращение по координате Y. Одно- 45 Такт 5, по которым устройство вы- временно содержимое счетчика 15 (iY) уменьшается на единицу. Конец отработки по координате Y фиксирует RS-триггер 12. В результате выполнения операций по Такту 3 и Такту 4 устройство реализует уравнение Y; У,., + КХ;.

Сигнал Такт 5, вырабатываемый генератороя 2, устанавливает в сосполняет следующие операции:

1 такт OG З - RG З - от содержимого регистра 3 вычитается 50 содержимое регистра 5 и результат операции отсылается в регистр 3J

2 такт CRG 4 - ГрЦд от

содержимого регистра 4 вычитается содержимое триггера 14, фиксирующетоянйе О счетчик 37 и D-триггер 36,gg го значение переноса 1 или О

а В-триггер 35 - в состояние 1.при выполнении Такта 1, и результат

Генератор 2 прекращает свою работуоперации отсылается,в регистр 4;

. до поступления следующей импульса3 такт RG 4 + RG 6j по цепи БЗСУ.кчсодержимому регистра 4 прибавляетЕсли RS-триггеры 12 и 13 в про- цессе отработки устанавливаются в состояние 1, то срабатывает элемент И 21, Формирователь 23-формирует импульс Конец отработки, по которому в состояние О устанавливаются регистры 3-7. RS-триггеры 11- 13, D-триггер 14, счетчики 15 и 16

и генератор,. 1 . 1

Работа предлагаемого кругового интерполятора иллюстрируется примером интерполяции дуги окружности, - расположенной в первом квадрате, при движении против часовой стрелки с параметрами: Хц 5, Уц О, йХ 3 ЛУ 5. N-разрядность суммато- ра 2, регистров 3-7 и селекторов- мультиплексоров 8 и 9 равна 8.

Исходная информация заносится в регистры устройства:

GR 4 - 1010000Q - нормализованное значение X 5-,

RG 5 - .00000000 - нормализованное значение YH 0;

RG3 - 00000000 всегда устанавли- ваются в состояние

RG.6 - 00000000 - перед началом работы

RG 7 - ОООП111 значение кода маски,

которое формируется при нормализации (сдвиге влево до появления зна- чений цифры в старшем разряде) значений Х„ 5. и YH О путем заполнения регистра кодом 1 со стороны младшего разряда. При этом количество единиц будет равно числу сдвигов при нормализации .

Далее по каждому импульсу, поступающему по цепи БЗСУ, генератор 1 формирует сигналы управления Такт 1, Такт 2, Такт 3, Такт 4 и

Такт 5, по которым устройство вы-

45 Такт 5, по которым устройство вы-

полняет следующие операции:

1 такт OG З - RG З - от содержимого регистра 3 вычитается 50 содержимое регистра 5 и результат операции отсылается в регистр 3J

2 такт CRG 4 - ГрЦд от

содержимого регистра 4 вычитается содержимое триггера 14, фиксирующе 13

ся содержимое регистра 6 и результат операции отсылается в регистр 6;

А такт RG 5 + 5 - к

содержимому регистра 5 прибавляется содержимое триггера 14, фиксирующего значение переноса 1 или О при вьшолнении Такта 3 и результат . операции отсьшается в регистр 5

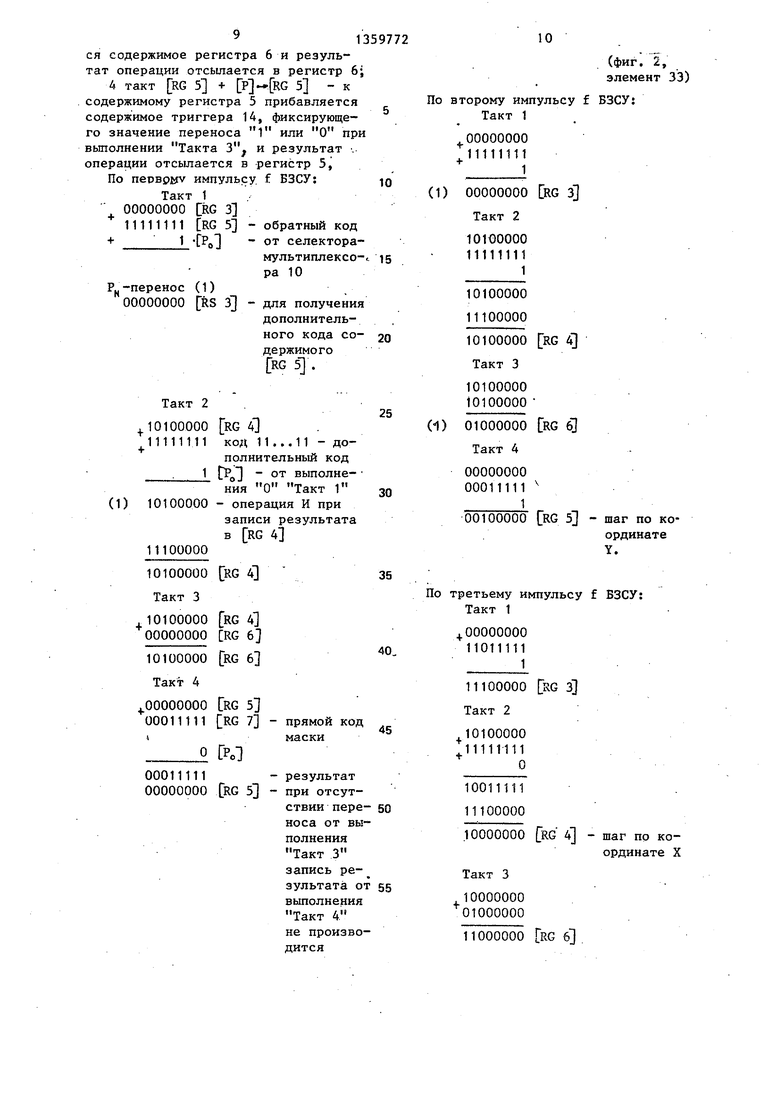

По neoBptfv импульсу f БЗСУ;

Такт 1 00000000 RG 3

11111111 RG 5 - обратный код

Р.. -перенос

N

±-ГРо1

(1)

- от селектора- мультиплексора 10

00000000 RS З - для получения дополнительного кода содержимого

RG 5 .

Такт 2

10100000 11111111

RG 4

код 11 ... 11 - дополнительный код ° выполне1) 10100000

О Такт 1

11100000

10100000

Такт 3

10100000 00000000

10100000 Такт 4

00000000 00011111

t

00011111 00000000

о. ния

- операция И при записи результата

в RG 4

RG 4

RG 4

RG 6

RG 6

RG 5 CRG 7

ГРс

RG 5

прямой код

маски

25

30

35

40.

45

результат при отсутствии пере- 50 носа от выполненияТакт 3 запись ре- зультата от 55 выполнения Такт 4 не производится

10

(фиг. 2, элемент 33)

По второму импульсу f БЗСУ: Такт 1

00000000 11111111

(1) 00000000 RG з

Такт 2 10100000

11111111 1

10100000 11100000

10100000 RG 4

Такт 3

10100000 10100000

(1) 01000000 CRG б

Такт 4

00000000 00011111

1

00100000 RG 5 - шаг по координатеY.

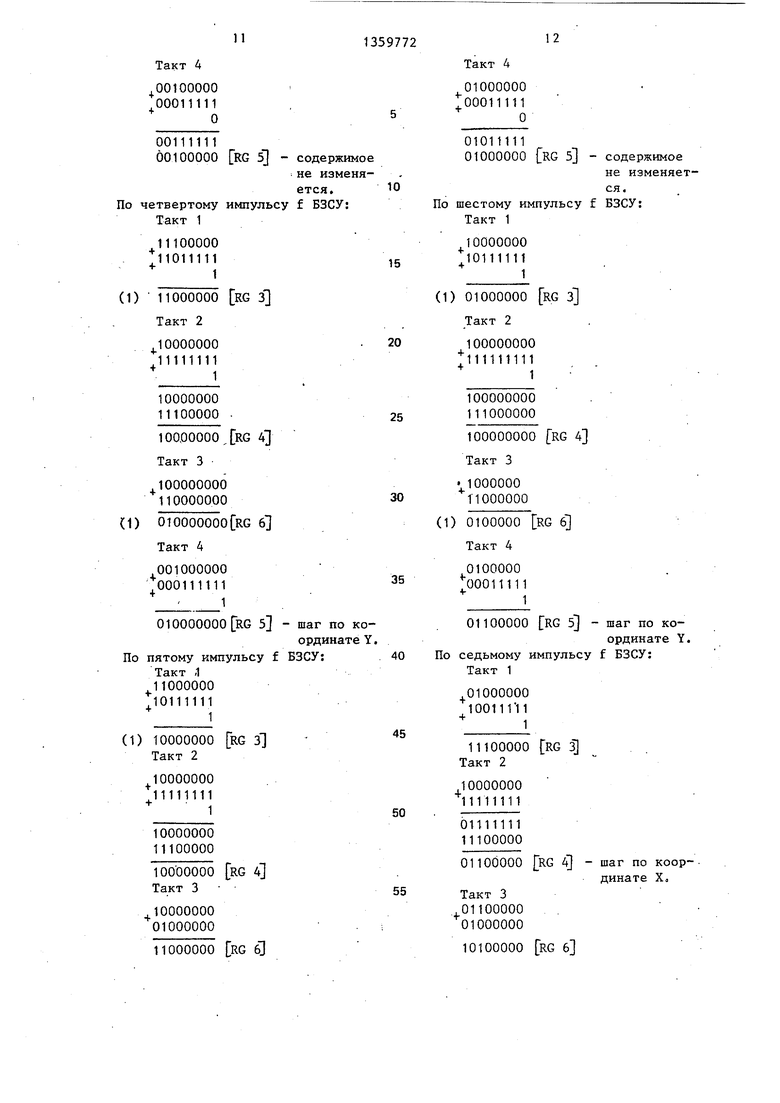

По третьему импульсу f БЗСУ: Такт 1

00000000

11011111

1

11100000 RG з

Такт 2 10100000

11111111 о

RG 4 - шаг по координате X

11000000 RG б

Такт 4

00100000 00011111 О5

00111111

00100000 RG 5 - содержимое не изменяется. 10 о четвертому импульсу f БЗСУ:

Такт 1

11100000 11011111

(1) 11000000

Такт 2

10000000 11111111

10000000 11100000 .

100.00000,RG

Такт 3

100000000 110000000

010000000 RG 6

Такт 4 ,001000000

000111111

010000000 RG з - шаг по координате Y.

пятому импульсу f БЗСУ: Такт ,1 11000000 10111111

(1) 10000000 RG з

Такт 2 10000000

11111111

10000000 11100000

юо ооооо

Такт 3

1 10000000 01000000

11000000 RG б

Такт 4

01000000 00011111

о

01011111

01000000 RG з - содержимое не изменяется. По шестому импульсу f БЗСУ:

Такт 1

10000000

10111111

1

(1) 01000000 RG з

Такт 2 100000000

;|;iiiiiiiii

1

100000000 111000000

100000000 RG 4

Такт 3

1000000 11000000

(1) 0100000 RG б

Такт 4

0100000 00011111

01100000 RG з - шаг по координате Y.

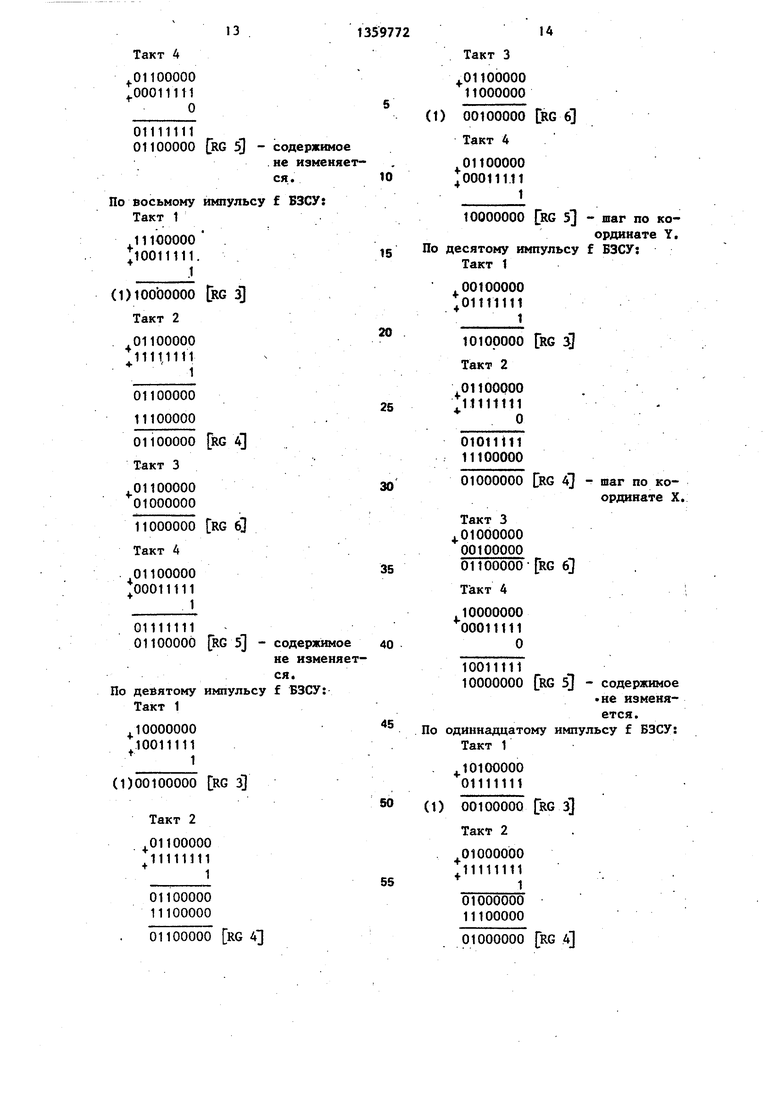

По седьмому импульсу f БЗСУ: Такт 1

01000000 10011111

11100000 RG з

Такт 2

10000000 11111111

01111111 11100000

01100000 RG 4 - шаг по координате X, Такт 3 01100000 01000000

10100000 RG б

13

Такт 4

01100000 ..00011 HI Vо5

01111111

01100000 (RG 5) - содержимое

.не изменяется. 10

о восьмому импульсу ВЗСУ: Такт 1

11100000

10011111.

(1)10000000 IRG

Такт 2

01100000 1111,111

01100000 11100000

01100000

Такт 3

01100000 01000000

11000000 RG б

Такт 4

01100000 00011111

01111111

01100000 (RG 5 - содержимое 40 не изменяется. девятому импульсу f БЗСУ:

Такт 1

10000000 5

10011111 1

(1)00100000 RG з

Такт 2

01100000 11111111

01100000 11100000

01100000 RG 4

5

10

14

Такт 3

01100000 11000000

(1) 00100000 RG 6

Такт 4

01100000

00011111

1

10000000 RG 5 - шаг по координате Y.

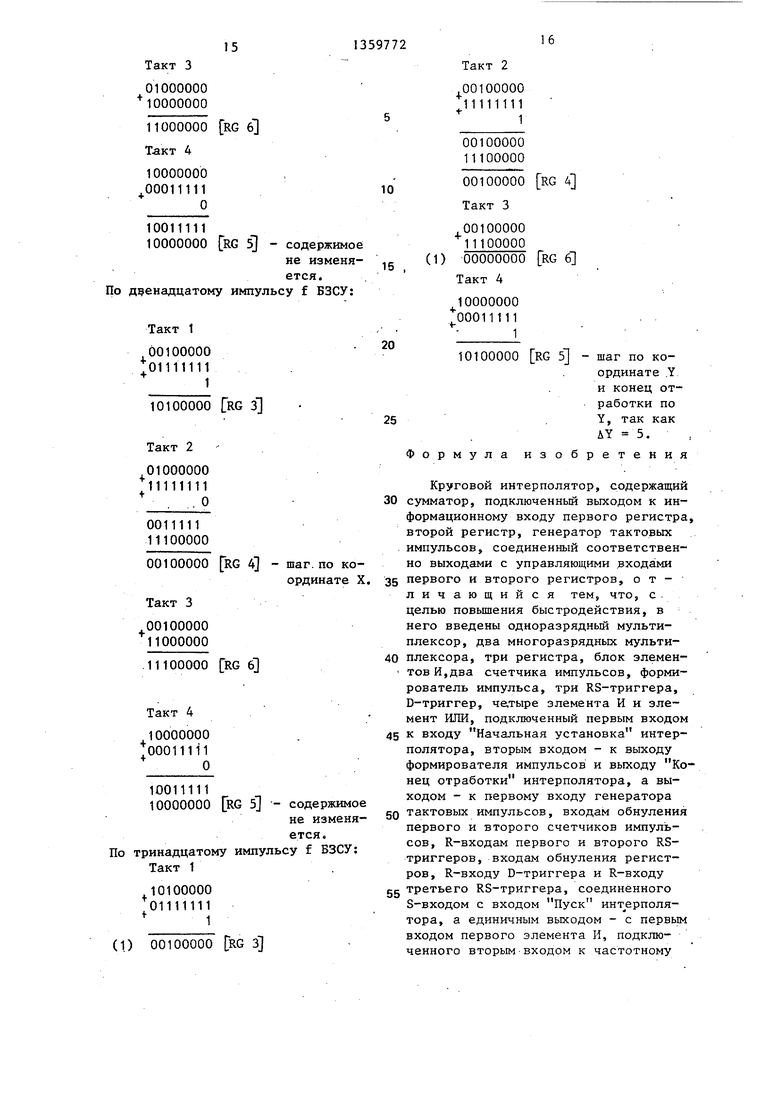

По десятому импульсу f БЗСУ: Такт 1

00100000

+01111111

1

Л

10100000 TRG з

Такт 2 01100000

11111111

01011111 11100000

01000000 RG 4 - шаг по координате X.

Такт 3 4.01000000 00100000

01100000- RG б

Т акт 4

10000000

00011111

О

10011111

10000000 RG з - содержимое не изменяется.

одиннадцатому импульсу f БЗСУ: Такт Г

10100000 01111111

(1) 00100000 RG з

Такт 2

01000000 11111111

01000000 11100000

01000000 RG 4

Такт 3

01000000 Ч 0000000

11000000

Такт 4

10000000

00011111

О

10011111

10000000 RG 5 - содержимое не изменяется. двенадцатому импульсу f БЗСУ:

Такт 1

00100000 J;01111111

10100000 CRG з

Такт 2

01000000

11111111

. О

0011111 11100000

RG 4

RG б

- шаг.по координате X.

10011111

10000000 RG 5 - содержимое не изменяется. тринадцатому импульсу f БЗСУ:

Такт 1.

10100000 01111111

1

(1) 00100000 RG з

е

10

15

20

25

16 Такт 2

00100000 11111111

00100000 11100000

00100000 ко 4 Такт 3

00100000 11100000

(1) 00000000 RG 6

Такт 4

10000000 00011111

;1

10100000 RG з - шаг по координате .Y и конец отработки по Y, так как AY 5.

Формула изобретения

Круговой интерполятор, содержащий

сумматор, подключенный вьпсодом к информационному входу первого регистра, второй регистр, генератор тактовых импульсов, соединенный соответственно выходами с управляющими входами

первого и второго регистров, отличающийся тем, что, с . целью повьш1ения быстродействия, в него введены одноразрядный мультиплексор, два многоразрядных мультиплексора, три регистра, блок элемен- тов И,два счетчика импульсов, формирователь импульса, три RS-триггера, D-триггер, четыре элемента И и элемент ИЛИ, подключенный первым входом

к входу Начальная установка интерполятора, вторым входом - к выходу формирователя импульсов и выходу Конец отработки интерполятора, а выходом - к первому входу генератора

тактовых импульсов, входам обнуления первого и второго счетчиков импульсов, R-входам первого и второго RS- триггеров, входам обнуления регистров, R-входу D-триггера и R-входу

третьего RS-триггера, соединенного S-входом с входом Пуск инт ерполя- тора, а единичным выходом - с первым входом первого элемента И, подключенного вторым входом к частотному

входу интерполятора, а выходом - к второму входу генератора тактовых импульсов, связанного третьим входом с первым входом второго элемента И и единичным выходом D-триггера, а также третьим, четвертым и пятым выходами - с соответствующими управляющими входами мультиплексора, шестым выходом - с С-входом D-триггера, а седьмым и в осьмым выходами - с управляющими входами соответственно третьего и четвертогр регистров, подключенных установочными входами соответственно к шинам Начальная координата по X и Начальная коор- дината по Y, причем информационный вход третьего регистра соединен с выходом блока элементов И, а инфор- 1ационный вход четвертого регистра подключен к информационному входу второго регистра, первому входу блока элементов И и первому выходу сумматора, связанного первым и вто- рым выходами, переноса соответственно с выходом одноразрядного мультиплексора и S-входом D-триггера, а первым информационным входом - с выходом первого многоразрядного мультиплек- сора, подключенного нулевым информационным входом к выходу первого регистра, первым и вторым информационными входами - к выходу третьего ре- Гистра, а третьим информационным входом - к прямому выходу четвертого егистра, соединенного инверсным выодом с нулевым информационным вхоом второго многоразрядного мультиплексора, подключенного выходом к второму информационному входу сумматора, первым, вторым и третьим информационным входами - соответствен- но к шине Код II...II интерполятора, выходу второго регистра и прямому выходу пятого регистра, соединен- ного инверсньм выходом с вторым входом блока элементов И, а установочным входом --с шиной Код маски ин0 терполятора, входная шина Код 1 которого подключена к первому информационному входу одноразрядного мультиплексора связанного вторым, третьим и четвертым информационными вхо5 дами соответственно с единичным

выходом D-триггера, шиной Код О и первым входом второго элемента И, подключенного вторым входом к восьмому выходу генератора тактовых импульсов, соединенного седьмым выходом с первым входом третьего элемента И, подключенного вторым входом к нулевому выходу D-трйггера, причем выходы второго и третьего элементов

5 И связаны с выходами интерполятора соответственно Приращение по координате Y, Приращение по координате X со счетными входами соответ,ст- венно первого и второго счетчиков

0 импульсов, подключенных установочными входами соответственно к шинам Координата дХ, Координата дУ интерполятора, управляющими входами - к входу Запись интерполятора, а выходами - к S-входам соответственно первого и второго RS-триггеров, соединенных единичными выходами с входами четвертого элемента И, подключенного выходом к входу формирователя импульсов.

5

U

и

uuirmj uuLmu

u

и

u

u

и

и

и

и

u

и

LTLJLrrr

Cp(js.2

и

uuLm

и

u

и

и

и

Lrrr

ЛУ

Редактор А.Лежнина

дзи&б

Составитель Н.Горбунова

Техред А.Кравчук Корректор И.Муска

(риг. 5

.д X

6К

6152/49

Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-прлиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатный цифровой интерполятор | 1986 |

|

SU1315939A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для программного управления | 1985 |

|

SU1249482A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в системах числового программного управления станками, чертежным оборудованием и другим оборудованием, в котором необходимо осуществлять круговую интерполяцию. Целью изобретения является повышение быстродействия и уменьшение в два раза разрядности устройства. Интерполятор содержит генератор 1 тактовых импульсов, сумматор 2, регистры 3-7, многоразрядные мультиплексоры 8, 97- одноразрядный муль- . типлексор 10, RS-триггеры 11-13, D- триггер 14, счетчики импульсов 15, 16, блок элементов И 17, элементы И 18-21, элемент Ш1И 22, формирователь 23 импульса, 6 ил. СО ел QD . фи.1

| Авторское, свидетельство СССР № 499556, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-12-15—Публикация

1985-03-04—Подача