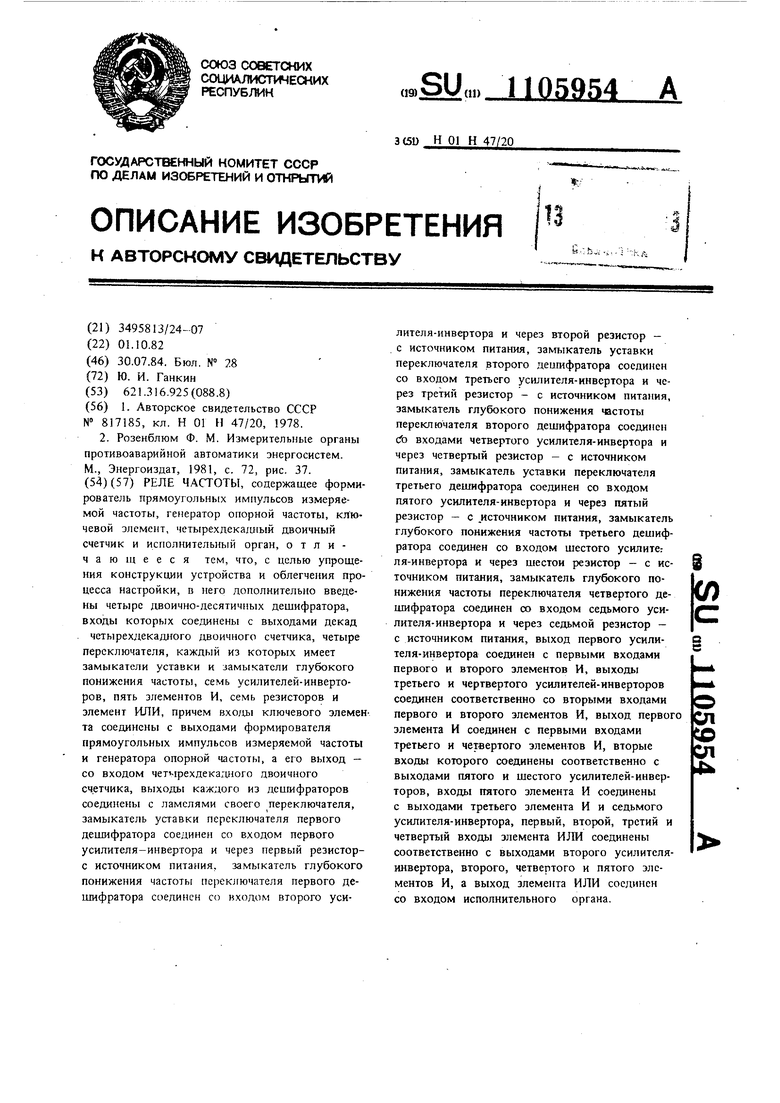

Изобретение относится к электротехнике, именно, к частоточувствительным устройствам противоаварийной автоматики энергосистем и предназначено для управления режимом работ энергосистем при возникновении аварийных дефицитов мощности. Известно реле частоты, используемое в противоаварийной автоматике энергосистем {1 Недостатком реле являются сложность устройства и его настройки. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является цифровое реле частоть, содержащее формирователь импульсов, кварцевый генератор опорной частоты, двоичные декадные счетчики, десятичные декодирующие переключа тели, логическую схему и исполнительный орган 2. Недостатки реле - необходимость пересчета частоты, задаваемой в герцах, в длитель ность периода, измеряемого в единицах време ни; сложность настройки, так как уставка за дается набором двоичного кода контактного поля декодирующих десятичных переключателей,сгепени регулировки составляют 0,03 Гщ а требуется 0,01 Гц. Целью изобретения является упрощение устройства и облегчение процесса настройки. Поставленная цель достигается тем, что в реле частоты, содержащее формирователь прямоугольных импульсов измеряемой частоты генератор опорной частоты, ключевой элемент четырехдекадный двоичный счетчик и исполни тельный орган, дополнительно введены четыре двоично-десятичных дешифратора, входы кото рых соединены с выходами декад четырехдекадного двоичного счетчика, четыре переключателя, каждый из которых имеет замыкатели установки и замыкатели глубокого понижения частоты, семь усилителей-инверторов, пять элементов И, семь резисторов и элемент ИЛИ причем входы ключевого элемента соединены с вьгходами формирователя прямоугольных импульсов измеряемой частоты и генератора опорной частоты, а его выход - со входом четырехдекадного двоичного счетчика, выходы каждого из деигафраторов соединены с ламелями своего переключателя, замыкатель устав ки переключателя первого дешифратора соеди нен со входом первого усилителя-инвертора и через первый резистор - с источником питания, замыкатель глубокого понижения частоты переключателя первого дешифратора соединен со входом второго усилителя-инвертора и через второй резистор - с источником пТТтаиня. замыкатель уставки переключателя второго дешифратора соединен со входом Tjicrben ycujiiiTejtfl-инвертора и через аретий резистор - с источником питания, замыкатель глубокого понижения частоты переключателя в второго дещифрагора соединен со входом четвертого усилителя-инвертора и через четвертый резистор - с источником питания, замыкатель уставки переключателя третьего деши- фратора соединен со входом пятого усилителя-инвертора и через пятый резистор - с источником питания, замыкатель глубокого понижения частоты третьего дешифратора соединен со входом -шестого усилителя-инвертора и через шестой резистор - с источником питания, замыкатель глубокого понижения частоты переключателя четвертого дешифратора соединен со входом седьмого усилителя-инвертора и через седьмой резистор - с источником питания,выход первого усилителя-инвертора соединен с первыми входами первого и второго элементов И, выходы третьего и четвертого усилителей-инверторов соединены соответственно со вторыми входами первого и второго элементов И, выход первого элемента И соединен с первыми входами третьего и четвертого элементов И, вторые входы которого соединены соответственно с выходами пятого и шестого усилителей-инверторов, входы пятого элемента И соединены с выходами третьего элемента И и седьмого усилителя-инвертора, первый, второй, третий и чертвертый входы элемента ИЛИ соединен соответственно с выходами второго усилителя-инвертора, второго, четвертого и пятого элементов И, а выход элемента ИЛИ соединен со входом исполнительного органа. На чертеже приведена функциональная схема реле частоты. Реле частоты содержит формирователь импульсов измеряемой частоты 1, генератор опорной частоты 2, выходы которых соединены со входами ключевого элемента 3. Выход ключевого элемента соединен со входом четырехдекадного двоичного счетчика 4, выходы которого соединены со входами двоично-десятичных дешифраторов 5-8. Выходы дешифратора 5 соответствуют значениям частоты О, 10, 20, 30, 40, 50, 60, 7.0, 80, 90 Гц (расположены на чертеже снизу вверх) и подключены к ламелям переключателя 9. Переключатель 9 содержит замыкатель уставки 10 и замыкатель глубокого понижения частоты 11, которые перемещаются по ламелям, замыкая их. Выходы дешифратора 6 соответствуют значениям частоты О, 1, 2, 3, 4, 5, 6, 7, 8, 9 Гц (расположены на чертеже снизу вверх) и подключены к ламелям переключателя 12. Переключатель 12 содержит замыкатель уставки 13 и замыкатель глубокого понижения частоты 14, которые перемещаются но ламелям, замыкая их. Выходы дешифратора 7 соответствуют зна чениям чистоты 0,1, 0,2, 0,3, 0,4, 0,5, 0,6, 0,7, 0,8, 0,9 Гц (расположены на чертеже сни вверх) и подключены к ламелям переключате ля 15. Переключатель 15 имеет замыкатель уставки 16 и замыкатель глубокого понижен частоты 17, которые перемещаются по ламеля замыкая их. Выходы дешифратора 8 соответствуют зна чениям частоты 0,01, 0,02, 0,03, 0,04, 0,05, 0,06, 0,07, 0,08, 0,09 Гц (расположены на чертеже снизу вверх) и подключены к ламелям переключателя 18. Переключатель 18 имеет замыкатель глубокого понижения час-тоты 19, который перемещается по ламелям, замыкая их. Замыкатели устайки 10, 13 и 16 соединен соответственно с резисторами 20, 21 и 22. Замыкатели глубокого понижения частоты 11, 14, 17 и 19 соединены соответственно с резисторами 23, 24, 25 и 26. Резисторы 2026 подсоединены к источнику питания. Замыкатели уставки 10, 13, 16 и замыкатели глубокого понижения частоты 11, 14, 17 и 19 соединены также соответственно со входами усилителей-инверторов 27-33. Выходы усилителей-инверторов 27 и 28 соединены со входами схемы И 34, выход схемы И 34 и выход усилителя-инвертора 29 соединен со входами схемы И 35. Выход усилителяинвертора 31, а также выход усилителя-инвер тора 27 соединены с выходами схемы И 36. Выход усилителя-инвертора 32, а также выход схемы И 34 соединены со входами схемы И 37. Выход усилителя-инвертора 33 и выход схемы И 35 соединены с входами схемы И 38. Выходы усилителя-инвертора 30, выходы схем И 36, 37 и 38 соединены со входами схемы ИЛИ 39. Выход схемы ИЛИ 39 соединен со входом исполнительного органа 40. Устройство работает следующим образом. Напряжение измеряемой частоты поступает на формирователь прямоугольных импульсов измеряемой частоты 1 и с выхода его поступают на один из входов ключевого злемента 3. На второй вход ключевого элемента 3 поступает сигнал с выхода генератора опорной частоты 2. С выхода ключевого элемента 3 импульсы счета периодически подаются на четырехдекадный двоичный счетчик 4. С выхо дов четырехдекадного двоичного счетчика 4 результат счета в двоичном коде подается на входы двоично-десятичных дешифрато|)ов 5-8. Дещифраторы представляют результат счета в десятичном коде, т.е. у каждого ИЗ четырех дешифраторов 5-8 открывается выход, соответствующий цифровому значению измеряемой частоты в каждой декаде. Выходы дешифраторов 5-8, соответствующие значениям цифр О, 1, 2, 3, 4, 5, 6, 7, 8, 9 на чертеже расположены снизу вверх. Для задания уставки частоты замыкатели уставки 10, 13 и 16 переключателей 9, 12 и 15 устанавливаются на нужные ламелн переключателей, соединенные с выходам:; л.ешифраторов 5-7, а замыкатель глубокого понижения частоты 19 переключателя 18 - на ламели Переключателя, соединенные с выходами дешифратора 8. При понижении измеряемой частоты до величины уставки срабатывание устройства осуществляется следующим образом. В разряде десятков герц ток от источника питания проходит через резистор 20, замыкатель уставки 10 и открытый выход дешифратора 5. Сигнал падения напряжения при прохождении тока поступает на вход усилителяинвертора 27, с выхода которого сигнал логической единицы поступает на один из входов схемы И 34. В разряде единиц герц ток от источника питания проходит через резистор 21, замыкатель уставки 13 и открытый выход дешифратора 6. Сигнал падения напряжения при прохождении тока поступает на вход усилителяинвертора 28, с выхода которого сигнал логической единицы поступает на второй вход схемы И 34, и с выхода ее сигнал логической единицы поступает на один из входов схемы И 35. В разряде десятых долей герц ток от источника питания проходит через резистор 22, замыкатель уставки 16 и открытый выход дешифратора 7. Сигнал падения напряжения при прохождении тока поступает на вход усилителя-инвертора 29, с выхода последнего сигнал логической единицы поступает на второй вход схемы И 35, с выхода которой сигнал логической единицы поступает на один из входов схемы И 38. В разряде сотых долей герц ток от источника питания проходит через резистор 26, замыкатель глубокого понижения частоты 19, открытый выход дешифратора 8. Сигнал паде ния напряжения при прохождении тока поступает на вход усилителя-инвертора 33, с выхода которого сигнал логической единицы поступает на второй вход схемы И 38. С выхода схемы И 38 сигнал логической единицы поступает на один из входов схемы ИЛИ 39, и с выхода этой схемы сигнал логической единицы поступает на вход исполнительного органа 40. Устройство срабатывает. При понижении измеряемой частоты на вел1гжну ниже уставки срабатывание устройства осуществляется следуюиош образом. При понижении измеряемой частоты на величину ниже уставки на десятки герц ток от источника питания проходит через резистор 23,замыкатель глубокого понижения частоты 11 н один из открытых выходов дешифратора 5. Сигнал падения напряжения при прохож дении тока поступает на вход усилителя-инвер тора 30, ас выхода его сигнал логической единицы поступает на один из входов схемы ИЛИ 39. С выхода этой схемы сигнал логической единицы поступает на вход исполнител ного органа 40 . Устройство срабатывает. При тмшжении измеряемой частоты на ве личину ниже уставки на единицы герц ток от источника питания проходит через резистор 24,замыкатель глубокого понижения частоты 14, и один из открытых выходов дешифратора 6. Сигнал падения напряжения при прохождении тока поступает на вход усилителяинвертора 31, с выхода его сигнал логической единицы поступает на один из входов схемы И 36. На второй вход схемы И 36 подается сигнал логической единицы с выхода усилител инвертора 27 при условии, что в разряде де сятков герц частота находится в пределах уставки. С выхода схемы И 36 сигнал логической единицы поступает на один из входов схемы ИЛИ 39. С выхода этой схемы сигнал логической единицы поступает на вход исполн тельного органа 40. Устройство срабатывает. При понижении измеряемой частоты на величину ниже уставки на десятые доли герц ток от ирточннка питания проходит через резистор 25, замыкатель глубокого понижения частоты 17 и один из открытых выходов дешифратора 7. Сигнал падения напряжения при прохождении тока поступает на вход усилителя инвертора 32, с выхода его сигнал логической единицы поступает на один из входов схемы И 37. На второй вход схемы И 37 подается сигнал логической единицы с выхода схемы . И 34 при условии, что в разрядах десятков и единиц герц частота находится в пределах уставки. С выхода схемы И 37 сигнал логичес кой единицы поступает на один из входов схемы ИЛИ 39. С выхода этой схемы сигнал логической единицы поступает на вход исполнительного органа 40. Устройство срабатывает. При понижении измеряемой частоты на величину ниже уставки на сотые доли герц ток от источника питания проходит через резистор 26, замыкатель глубокого понижения частоты 19 н один из открытых выходов дешифратора 8. Сигнал падения напряжения при прохождении тока поступает на вход усилителя инвертора 33, с выхода его сигнал логической единицы поступает на один из входов схемы И 38. На второй вход этой схемы подается сигнал логической единицы с выхода , схемы И 35 при условии, что в разрядах десятков, единиц, десятых долей герц частота находится в пределах уставки. С выхода схемы И 38 сигнал логической единицы поступает на один из входов схемы ИЛИ 39. С выхода- этой схемы сигнал логической единицы поступает на вход исполнительного органа 40. Устройство срабатьшает. Таким образом, для срабатывания устройсг ва необходимо, чтобы имелись разрешающие сигналы высших декад по отношению к низшим. Предлагаемое устройство, выполненное с применением двоично-десятичных дешифраторов имеет более простую схему логики и позволяет сократить время на настройку.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле частоты | 1984 |

|

SU1182589A2 |

| Устройство индикации формирования печатных строк | 1985 |

|

SU1306732A1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

| Сигнализатор предельного уровня | 1989 |

|

SU1700377A1 |

| Устройство для исследования магнитных свойств материалов | 1987 |

|

SU1518809A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| ТРЕХФАЗНОЕ РЕЛЕ НАПРЯЖЕНИЯ | 1992 |

|

RU2054219C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МОЩНОСТЬЮ ЭЛЕКТРОНАГРЕВАТЕЛЯ | 1995 |

|

RU2090014C1 |

| Реле времени | 1991 |

|

SU1800609A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

РЕЛЕ ЧАСТОТЫ, содержащее формирователь прямоугольных импульсов измеряемой частоты, генератор опорной частоты, ключевой элемент, четь рехдекаш1ЫЙ двоичный счетчик и исполнительный орган, отличающееся тем, что, с целью упрощения конструкции устройства и облегчения процесса настройки, в него дополнительно введены четыре двоично-десятичных дещифратора, входы которых соединены с выходами декад . четырехдекадного даоичного счетчика, четыре переключателя, каждый из которых имеет замыкатели уставки и замьЕкатели глубокого понижения частоты, семь усилителей-инверторов, пять элементов И, семь резисторов и элемент ИЛИ, причем BXO;U.I ключевого элемента соединены с выходами формирователя прямоугольных импульсов измеряемой частоты и генератора опорной частоты, а его выход - со входом чет1-1рехдекад{юго двоичного счетчика, выходы каждого из деишфраторов соединены с ламелями своего переключателя, замыкатель уставки переключателя первого дещифратора соединен со входом первого усилителя-инвертора и через первый резисторс источником питания, замыкатель глубокого понижения частоты псреюгючателя первого дещифратора соединен со входом второго усилителя-инвертора и через второй резистор - с источником питания, замыкатель уставки переключателя второго дешифратора соединен со входом третьего усилителя-инвертора и через третий резистор - с источником питания, замыкатель глубокого понижения частоты переключателя второго дещифратора соединен СЬ входами четвертого усилителя-инвертора и через четвертый резистор - с источником питания, замыкатель уставки переключателя третьего деигафратора соединен со входом PLHToro усилителя-инвертора и через пятый резистор - с источником питания, замыкатель глубокого понижения частоты третьего дешифратора соединен со входом щестого усилите: г ля-инвертора и через щестои резистор - с источником питания, замыкатель глубокого по(Л нижения частоты переключателя четвертого дещифратора соединен со входом седьмого усилителя-инвертора и через седьмой резистор о с источником питания, выход первого усилителя-инвертора соединен с первыми входами первого и второго элементов И, выходы третьего и чертвертого усилителей-инверторов соединен соответственно со вторыми входами СП первого и второго элементов И, выход первого элемента И соединен с первыми входами 00 третьего и четвертого элементов И, вторые сл входы которого соединены соответственно с 4 выходами пятого и щестого усилителей-инверторов, входы пятого элемента И соединены с выходами третьего элемента И и седьмого усилителя-инвертора, первый, второй, третий и четвертый входы элемента И.ЛИ соединены соответственно с выходами второго усилителяинвертора, второго, четвертого и пятого элементов И, а выход элемента ИЛИ соединен со входом исполнительного органа.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ монтажа башни | 1979 |

|

SU817185A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Розенблюм Ф | |||

| М | |||

| Измерительные органы противоаварийной автоматики энергосистем | |||

| М., Энергоиздат, 1981, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

Авторы

Даты

1984-07-30—Публикация

1982-10-01—Подача