Изобретение относится к автоматике и вычислительной технике и может быть использовано при цифровой обработке сигналов.

Известно устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару [1], содержащее n-разрядный счетчик и n каскадов преобразования n = log2N (где N - длина преобразуемой последовательности), каждый из которых содержит первый и второй коммутатор, сумматор-вычитатель и 2i-1-разрядный регистр сдвига (i = i= - номер каскада преобразования).

- номер каскада преобразования).

Недостатком известного устройства является низкое быстродействие.

Известно устройство ортогонального преобразования цифровых сигналов по Уолшу-Адамару [2], содержащее блок формирования временных интервалов, блоки элементов И, блоки элементов ИЛИ, регистры, сумматоры-вычитатели.

Недостатком известного устройства является низкое быстродействие.

Наиболее близким техническим решением к предлагаемому изобретению является устройство быстрого преобразования Уолша-Адамара, содержащее блоки элементов И с первого по 2n+2-й (2n - размерность преобразования), 2n блоков элементов ИЛИ, регистры с первого по 2n+1, сумматоры с первого по 2n+1-й, 2n элементов задержки, причем информационный вход (2i-1)-го (i = i=  ) блока элементов И является i-ым информационным входом устройства, выходы (2i-1)-го и 2i-го блоков элементов И подключены к входам i-го блока элементов ИЛИ, выход i-го блока элементов ИЛИ подключен к информационному входу i-го регистра, прямой выход (2j-1)-го (j = j=

) блока элементов И является i-ым информационным входом устройства, выходы (2i-1)-го и 2i-го блоков элементов И подключены к входам i-го блока элементов ИЛИ, выход i-го блока элементов ИЛИ подключен к информационному входу i-го регистра, прямой выход (2j-1)-го (j = j= ) регистра подключен к первым входам j-го и (2n-1 + j)-го сумматоров, прямой и инверсный выходы 2j-го регистра подключены к вторым входам j-го и (2n-1 + j)-го сумматоров соответственно, управляющие входы блоков элементов И с номерами 2i-1 подключены к управляющему входу ввода информации устройства, управляющие входы блоков элементов И с номерами 2i подключены к входу задания режима вычислений устройства, выход (2n+1 + i)-го блока элементов И через i-1 элемент задержки подключен к информационному входу (2n+1)-го регистра, прямой выход (2n + 2j - 1)-го регистра подключен к третьим входам j-го и (2n-1 + j)-го сумматоров, прямой и инверсный выходы (2n + 2j)-го регистра подключены к четвертым входам j-го и (2n-1 + j)-го сумматоров соответственно, выход поразрядных сумм и выход поразрядных переносов i-го сумматора подключены к информационным входам 2i-го и (2n+1 + i)-го блоков элементов И соответственно, прямые выходы i-го и (2n + i)-го регистров подключены к информационным входам (3 ˙2n + i)-го блока элементов И, выходы которого подключены к входам (2n + i)-го сумматора, выход (2n + i)-го сумматора является i-ым выходом первой группы устройства, входы (2n + i)-го сумматора подключены к выходам i-й подгруппы второй группы устройства, управляющий вход (2n+1 + i)-го блока элементов И соединен с управляющим входом 2i-го блока элементов И, входы установки в "0" всех регистров подключены к установочному входу устройства, управляющие входы блоков элементов И с (3 ˙2n+1)-го по 2n+2-й подключены к управляющему входу выдачи информации устройства.

) регистра подключен к первым входам j-го и (2n-1 + j)-го сумматоров, прямой и инверсный выходы 2j-го регистра подключены к вторым входам j-го и (2n-1 + j)-го сумматоров соответственно, управляющие входы блоков элементов И с номерами 2i-1 подключены к управляющему входу ввода информации устройства, управляющие входы блоков элементов И с номерами 2i подключены к входу задания режима вычислений устройства, выход (2n+1 + i)-го блока элементов И через i-1 элемент задержки подключен к информационному входу (2n+1)-го регистра, прямой выход (2n + 2j - 1)-го регистра подключен к третьим входам j-го и (2n-1 + j)-го сумматоров, прямой и инверсный выходы (2n + 2j)-го регистра подключены к четвертым входам j-го и (2n-1 + j)-го сумматоров соответственно, выход поразрядных сумм и выход поразрядных переносов i-го сумматора подключены к информационным входам 2i-го и (2n+1 + i)-го блоков элементов И соответственно, прямые выходы i-го и (2n + i)-го регистров подключены к информационным входам (3 ˙2n + i)-го блока элементов И, выходы которого подключены к входам (2n + i)-го сумматора, выход (2n + i)-го сумматора является i-ым выходом первой группы устройства, входы (2n + i)-го сумматора подключены к выходам i-й подгруппы второй группы устройства, управляющий вход (2n+1 + i)-го блока элементов И соединен с управляющим входом 2i-го блока элементов И, входы установки в "0" всех регистров подключены к установочному входу устройства, управляющие входы блоков элементов И с (3 ˙2n+1)-го по 2n+2-й подключены к управляющему входу выдачи информации устройства.

Устройство работает следующим образом.

Перед началом вычислений регистры сбрасываются в "0" по сигналу на установочном входе. В регистры с информационных входов через блоки элементов И и блоки элементов ИЛИ записываются 2n отсчетов входного сигнала. Запись осуществляется по сигналу на управляющем входе ввода информации устройства.

Итерационный процесс вычислений в соответствии с алгоритмом быстрого преобразования Уолша-Адамара обеспечивается подачей единичного потенциала на соответствующий управляющий вход устройства.

Особенность вычислительного процесса состоит в том, что результат суммирования представляется двухстрочным кодом. Первая строка представляется поразрядной суммой и переписывается с первого выхода сумматора в соответствующий регистр. Вторая строка представляет поразрядные переносы и с второго выхода сумматора записывается в соответствующий регистр. На сумматорах реализуется вычитание благодаря подключению инверсных выходов регистров.

После n итераций в регистрах формируются двухстрочные коды коэффициентов преобразования. По сигналу на управляющем входе выдачи информации устройства двухстрочные коды коэффициентов преобразования могут быть переданы на выходы устройства. При необходимости получения однострочного кода информация снимается с выходов сумматоров.

Недостатком устройства является низкое быстродействие.

Цель предлагаемого изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство быстрого преобразования Уолша-Адамара, содержащее 2n+2 блоков элементов И (2n - размерность преобразования), 2n блоков элементов ИЛИ, 2n+1 регистров первой группы, две группы по 2n сумматоров, причем входы i-го блока элементов ИЛИ (i =  ) соединены с выходами (2i-1)-го и 2i-го блока элементов И, управляющие входы которых соединены соответственно с управляющим входом ввода информации и входом задания режима устройства, (2i-1)-ый информационный вход которого соединен с информационным входом (2i-1)-го блока элементов И, вход задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И, выход i-го блока элементов ИЛИ соединен с информационным входом i-го регистра первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра первой группы и установочным входом устройства, i-й выход первой группы выходов которого соединен с выходом i-го сумматора второй группы, прямой выход (2j - 1)-го регистра первой группы (j =

) соединены с выходами (2i-1)-го и 2i-го блока элементов И, управляющие входы которых соединены соответственно с управляющим входом ввода информации и входом задания режима устройства, (2i-1)-ый информационный вход которого соединен с информационным входом (2i-1)-го блока элементов И, вход задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И, выход i-го блока элементов ИЛИ соединен с информационным входом i-го регистра первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра первой группы и установочным входом устройства, i-й выход первой группы выходов которого соединен с выходом i-го сумматора второй группы, прямой выход (2j - 1)-го регистра первой группы (j =  ) соединен с первыми входами j-го и (2n-1 + j)-го сумматора первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра первой группы, прямой выход (2n + 2j - 1)-го регистра первой группы соединен с третьими входами j-го и (2n-1 + j)-го сумматоров первой группы, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра первой группы, введены с (2n + 1)-го по 2n+1-й блоки элементов ИЛИ и 2n+1 регистров второй группы, причем 2i-й информационный вход устройства соединен с информационным входом (3 ˙2n + i)-го блока элементов И, управляющий вход которого соединен с управляющим входом ввода информации устройства, выходы ( 3˙ 2n + i)-го и (2n+1 + i)-го блоков элементов И соединен с входами (2n + i)-го блока элементов ИЛИ, выход которого соединен с информационным входом (2n + i)-го регистра первой группы, тактовый вход которого соединен с одноименным входом i-го регистра первой группы и первым тактовым входом устройства, второй тактовый вход которого соединен с одноименными входами всех регистров второй группы, выходы (2i - 1)-го и 2i-го регистров которой соединены с входами i-го сумматора второй группы и являются i-ым двухстрочным выходом второй группы выходов устройства, прямой выход i-го регистра первой группы соединен с информационным входом (2i - 1)-го регистра второй группы, информационный вход 2i-го регистра второй группы соединен с прямым выходом (2n + i)-го регистра первой группы.

) соединен с первыми входами j-го и (2n-1 + j)-го сумматора первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра первой группы, прямой выход (2n + 2j - 1)-го регистра первой группы соединен с третьими входами j-го и (2n-1 + j)-го сумматоров первой группы, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра первой группы, введены с (2n + 1)-го по 2n+1-й блоки элементов ИЛИ и 2n+1 регистров второй группы, причем 2i-й информационный вход устройства соединен с информационным входом (3 ˙2n + i)-го блока элементов И, управляющий вход которого соединен с управляющим входом ввода информации устройства, выходы ( 3˙ 2n + i)-го и (2n+1 + i)-го блоков элементов И соединен с входами (2n + i)-го блока элементов ИЛИ, выход которого соединен с информационным входом (2n + i)-го регистра первой группы, тактовый вход которого соединен с одноименным входом i-го регистра первой группы и первым тактовым входом устройства, второй тактовый вход которого соединен с одноименными входами всех регистров второй группы, выходы (2i - 1)-го и 2i-го регистров которой соединены с входами i-го сумматора второй группы и являются i-ым двухстрочным выходом второй группы выходов устройства, прямой выход i-го регистра первой группы соединен с информационным входом (2i - 1)-го регистра второй группы, информационный вход 2i-го регистра второй группы соединен с прямым выходом (2n + i)-го регистра первой группы.

Анализ известной технической и патентной литературы показывает, что совокупность приведенных выше отличительных признаков неизвестна, что позволяет сделать вывод о существенности отличий предлагаемого устройства от известных.

При этом необходимо подчеркнуть, что только использование всех перечисленных выше отличительных признаков позволит получить положительный эффект - повысить быстродействие.

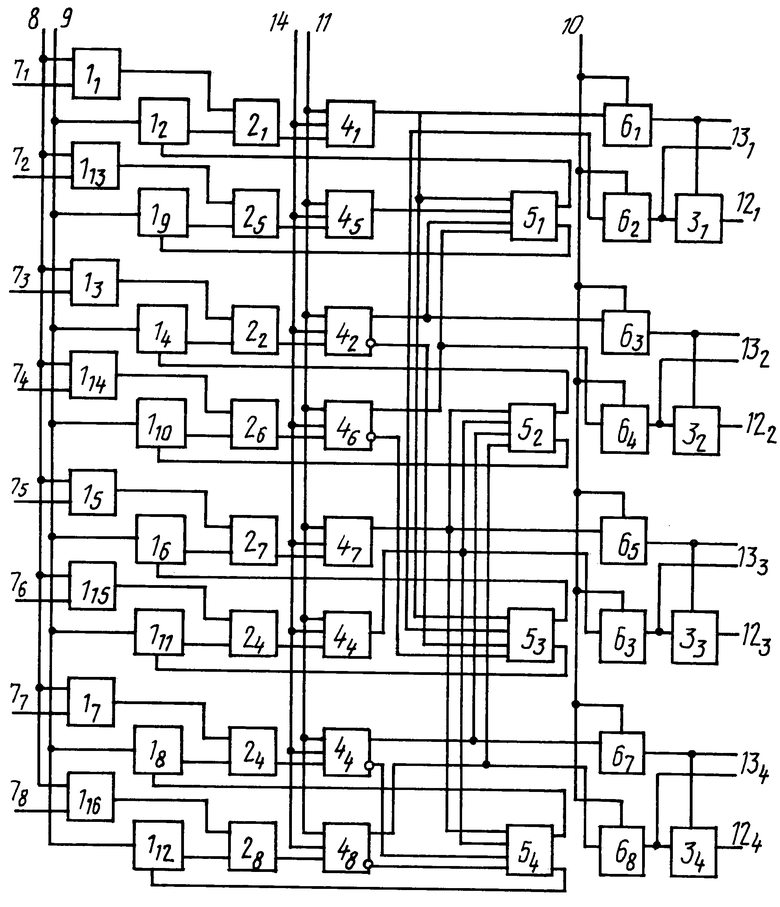

На чертеже представлена структурная схема устройства быстрого преобразования Уолша-Адамара для случая 2n = 4.

Устройство быстрого преобразования Уолша-Адамара содержит блоки элементов И 1, блоки элементов ИЛИ 2, сумматоры второй группы 3, регистры первой группы 4, сумматоры первой группы 5, регистры второй группы 6, информационные входы 7, управляющий вход ввода информации 8, вход задания режима устройства 9, второй тактовый вход 10, установочный вход 11, первую 12 и вторую 13 группу выходы, первый тактовый вход 14.

Элементы устройства соединены следующим образом. Входы i-го блока 2i элементов ИЛИ (i = (i= )) соединены с выходами (2i-1)-го и 2i-го блока элементов И 1, управляющие входы которых соединены соответственно с управляющим входом ввода информации 8 и входом 9 задания режима устройства, (2i - 1)-й информационный вход которого соединен с информационным входом (2i - 1)-го блока элементов И 1, вход 8 задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И 1, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы 5, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И 1, выходы i-го блока элементов ИЛИ 2 соединен с информационным входом i-го регистра 4 первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра 4 первой группы и уста- новочным входом 11 устройства, i-ый выход первой группы выходов 12 которого соединен с выходом i-го сумматора второй группы 3, прямой выход (2j - 1)-го регистра 4 первой группы (j =

)) соединены с выходами (2i-1)-го и 2i-го блока элементов И 1, управляющие входы которых соединены соответственно с управляющим входом ввода информации 8 и входом 9 задания режима устройства, (2i - 1)-й информационный вход которого соединен с информационным входом (2i - 1)-го блока элементов И 1, вход 8 задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И 1, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы 5, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И 1, выходы i-го блока элементов ИЛИ 2 соединен с информационным входом i-го регистра 4 первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра 4 первой группы и уста- новочным входом 11 устройства, i-ый выход первой группы выходов 12 которого соединен с выходом i-го сумматора второй группы 3, прямой выход (2j - 1)-го регистра 4 первой группы (j =  ) соединен с первыми входами j-го и (2n-1 + j)-го сумматора 5 первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра 4 первой группы, прямой выход (2n + 2j - 1)-го регистра 4 первой группы соединен с третьими входами j-го и (2n-1 + j)-го сумматоров первой группы 5, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра 4 первой группы, 2i-й информационный вход устройства 7 соединен с информационным входом (3˙2n + i)-го блока элементов И 1, управляющий вход которого соединен с управляющим входом 8 ввода информации устройства, выходы (3˙2n + i)-го и (2n+1 + i)-го блоков элементов И 1 соединены с входами (2n + i)-го блока элементов ИЛИ 2, выход которого соединен с информационным входом (2n + i)-го регистра 4 первой группы, тактовый вход которого соединен с одноименным входом i-го регистра 4 первой группы и первым тактовым входом 14 устройства, второй тактовый вход 10 которого соединен с одноименными входами всех регистров 6 второй группы, выходы (2i - 1)-го и 2i-го регистров 6 которой соединены с входами i-го сумматора второй группы 3 и являются i-ым двухстрочным выходом 13 второй группы выходов устройства, прямой выход i-го регистра первой группы 4 соединены с информационным входом (2i - 1)-го регистра второй группы 6, информационный вход 2i-го регистра второй группы 6 соединен с прямым выходом (2n + i)-го регистра первой группы 4.

) соединен с первыми входами j-го и (2n-1 + j)-го сумматора 5 первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра 4 первой группы, прямой выход (2n + 2j - 1)-го регистра 4 первой группы соединен с третьими входами j-го и (2n-1 + j)-го сумматоров первой группы 5, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра 4 первой группы, 2i-й информационный вход устройства 7 соединен с информационным входом (3˙2n + i)-го блока элементов И 1, управляющий вход которого соединен с управляющим входом 8 ввода информации устройства, выходы (3˙2n + i)-го и (2n+1 + i)-го блоков элементов И 1 соединены с входами (2n + i)-го блока элементов ИЛИ 2, выход которого соединен с информационным входом (2n + i)-го регистра 4 первой группы, тактовый вход которого соединен с одноименным входом i-го регистра 4 первой группы и первым тактовым входом 14 устройства, второй тактовый вход 10 которого соединен с одноименными входами всех регистров 6 второй группы, выходы (2i - 1)-го и 2i-го регистров 6 которой соединены с входами i-го сумматора второй группы 3 и являются i-ым двухстрочным выходом 13 второй группы выходов устройства, прямой выход i-го регистра первой группы 4 соединены с информационным входом (2i - 1)-го регистра второй группы 6, информационный вход 2i-го регистра второй группы 6 соединен с прямым выходом (2n + i)-го регистра первой группы 4.

Устройство работает следующим образом.

Перед началом вычислений регистры первой группы 4 устанавливаются в "0" по сигналу на установочном входе 11. Коды отсчетов входного сигнала в прямом и обратном кодах поступают на соответствующие информационные входы 7 устройства. После записи этой информации в регистры первой группы 4 через блоки элементов И 1 и ИЛИ 2, на входах каждой пары регистров 4i и 42n+i первой группы образуются двухстрочные коды, совокупность которых соответствует результатам выполнения первой итерации вычисления коэффициентов преобразования. Применительно к чертежу в регистры первой группы 41-44 с информационных входов 7 через блоки элементов И 11, 113, 13, 114, 15, 115, 17, 116 и блоки элементов ИЛИ 21, 25, 22, 26, 23, 27, 24, 28, записываются соответственно коды отсчетов входного сигнала х1, х2, х3, х4, х1, (-х2), х3 (-х4). Запись осуществляется по сигналу на управляющем входе 8 ввода информации и сигналу на первом тактовом входе 14. Такая организация ввода данных позволяет уменьшить на единицу число итераций.

Итерационный процесс вычислений в соответствии с алгоритмом быстрого преобразования Уолша-Адамара обеспечивается подачей единичного потенциала на вход задания режима устройства 9.

Особенность вычислительного процесса состоит в том, что результат суммирования на выходе сумматоров первой группы 5 представляется двухстрочным кодом. Первая строка является поразрядной суммой и переписывается с первого выхода сумматора первой группы 5 в соответствующий из регистров первой группы 41-44. Вторая строка представляет поразрядные переносы и с второго выхода сумматора первой группы 5 записывается в соответствующий из регистров первой группы 45-48. На сумматорах первой группы 53, 54 реализуется вычитание благодаря подключению инверсных выходов регистров первой группы 4.

После (n-1) итераций в регистрах первой группы 4 формируются двухстрочные коды коэффициентов преобразования. По сигналу на втором тактовом входе 10 устройства двухстрочные коды коэффициентов преобразования из регистров первой группы 4 переписываются в регистры второй группы 6 и выдаются на вторую группу выходов 13.

По сигналу на установочном входе 11 производится установка в "0" регистров первой группы 4, обеспечивая возможность приема очередных 2n отсчетов входного сигнала. При этом процесс вычисления двухстрочных кодов "новых" коэффициентов преобразования Уолша-Адамара совмещается с процессом преобразования i-го двухстрочного кода "старых" коэффициентов преобразования, записанных в регистрах второй группы 6, в традиционный однострочный код на сумматорах второй группы 3.

Необходимо отметить, что предлагаемое устройство обладает более широкими функциональными возможностями по сравнению с прототипом, т.к. может работать с двухстрочными кодами входных отсчетов сигнала. В этом случае на входы (2i - 1)-го и (3 ˙2n + i)-го блока 1 элементов И должны быть поданы соответственно первая и вторая составляющие i-го двухстрочного кода отсчета входного сигнала. Далее процесс функционирования устройства аналогичен ранее рассмотренному, за исключением того, что производится не (n-1), а n итераций.

Для технико-экономического обоснования преимуществ заявляемого устройства произведем сравнение по быстродействию заявляемого устройства и базового объекта, в качестве которого выберем прототип, как наиболее быстродействующее из устройств для быстрого преобразования Уолша-Адамара такого класса.

В качестве величины, определяющей быстродействие устройства, выберем время между поступлением групп отсчетов входного сигнала.

В базовом объекте (прототип) время между поступлением групп отсчетов входного сигнала равно времени на обработку устройством одной из таких групп и определяется

Тб = Тзап + n ˙Ти + Тпр, где Тзап - время записи отсчетов входного сигнала в регистры первой группы 4,

Тзап = Ти + Тили +ТRG;

Тит - время реализации одной из итерации,

Тит = ТSM + Tи + Тили + ТRG;

Тпр - время преобразования двухстрочного кода результата в однострочный,

Тпр = Тп +Тсум;

Ти, Тили, ТRG - время работы соответственно блоков элементов И, ИЛИ и регистров;

ТSM, Тсум - время работы сумматоров первой и второй группы соответственно.

В качестве быстродействующего сумматора второй группы выберем сверхпараллельной сумматор, у которого

Тсум = (2logкm + 3) τ, где K = 4; 5 - коэффициент объединения,

τ - время задержки в логическом элементе,

m - разрядность данных.

Результаты расчета Тпр в предположении, что Тn = τ , K = 4 и изменении разрядности m от 4 до 64 приведены в табл. 1.

Время преобразования ТSM четырехстрочного кода на входе сумматора первой группы 5 до двухстрочного кода не зависит от разрядности и определяется

ТSM = 2 ˙Tc, где Тс - время работы одноразрядного сумматора, Тс = 2 τ.

Полагая, что TRG = 2 τ, получим, что Тит = =ТSM + Ти + Тили + ТRG = 2Тс + τ+τ+2τ = =4τ+4τ=8τ, а время записи отсчетов входного сигнала

Тзап = Ти + Тили + ТRG = τ+τ+2τ=4τ.

Результаты расчета Тб = Тзап + n ˙Tит + +Тпр = 4τ+n˙8τ+Tпр для порядка преобразования n = 2, 4, 8, 16 и разрядности данных m = 4, 8, 16, 32 приведены в табл. 2.

В заявляемом устройстве совмещены операции получения двухстрочного кода результата и преобразования его к однострочному коду, поэтому интервал поступления очередных отсчетов входного сигнала будет определяться временем, необходимым для получения двухстрочного кода результата.

Время, необходимое для получения двухстрочного кода результата, как видно из анализа работы заявляемого устройства, определяется как

Tз=Tзап+(n-1)Tит=

= 4τ+(n-1)8τ=8nτ-4τ. и не зависит от разрядности данных.

Результаты расчета Тз при различных значениях n приведены в табл. 3. Определим выигрыш W, как

W = Тб/Тз. Результаты расчета выигрыша W при n = 2, 4, 8, 16, 32 и изменениях разрядности m от 4 до 64 приведены в табл. 4.

Анализ полученных результатов показывает, что предлагаемое устройство быстрого преобразования Уолша-Адамара превосходит в 1,1-2,4 раза по быстродействию базовый объект, что обеспечит обработку в реальном масштабе времени сигналов с более высокой частотой дискретизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство быстрого преобразования Уолша-Адамара | 1985 |

|

SU1377871A1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНЫХ ОРТОГОНАЛЬНЫХ ПРЕОБРАЗОВАНИЙ | 1990 |

|

RU2024931C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Устройство ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1980 |

|

SU951320A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1992 |

|

RU2072554C1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| ГЕНЕРАТОР ТРАНСОРТОГОНАЛЬНЫХ КОДОВ | 2000 |

|

RU2200972C2 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при цифровой обработке сигналов. Цель изобретения - повышение быстродействия. Поставленная цель достигается за чет совмещения во времени процессов получения двухстрочных кодов результата и преобразования их к однострочным, сокращения числа итераций алгоритма вычислений, для этого в устройство, содержащее блоки элементов И с первого по 2n+2 ( 2n - размерность преобразования), 2n блоков элементов ИЛИ, регистры с первого по 2n+1 первой группы, две группы по 2n сумматоров, введены с (2n+1) по (2n+1) блоки элементов ИЛИ и 2n+1 регистров второй группы. 1 ил.

УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА, содержащее 2n+2 блоков элементов U (2n - размерность преобразования), 2n блоков элементов ИЛИ, 2n+1 регистров первой группы, две группы по 2n сумматоров, причем входы i-го блока элементов ИЛИ (i =  ) соединены с выходами (2i - 1)-го и 2i-го блоков элементов И, управляющие входы которых соединены соответственно с управляющим входом ввода информации и входом задания режима устройства, (2i - 1)-й информационный вход которого соединен с информационным входом (2i - 1)-го блока элементов И, вход задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И, выход i-го блока элементов ИЛИ соединен с информационным входом i-го регистра первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра первой группы и установочным входом устройства, i-й выход первой группы которого соединен с выходом i-го сумматора второй группы, прямой выход (2j - 1)-го регистра первой группы (j =

) соединены с выходами (2i - 1)-го и 2i-го блоков элементов И, управляющие входы которых соединены соответственно с управляющим входом ввода информации и входом задания режима устройства, (2i - 1)-й информационный вход которого соединен с информационным входом (2i - 1)-го блока элементов И, вход задания режима устройства соединен с управляющим входом (2n+1 + i)-го блока элементов И, информационный вход которого соединен с выходом поразрядных переносов i-го сумматора первой группы, выход поразрядных сумм которого соединен с информационным входом 2i-го блока элементов И, выход i-го блока элементов ИЛИ соединен с информационным входом i-го регистра первой группы, вход сброса которого соединен с одноименным входом (2n + i)-го регистра первой группы и установочным входом устройства, i-й выход первой группы которого соединен с выходом i-го сумматора второй группы, прямой выход (2j - 1)-го регистра первой группы (j =  ) соединен с первыми входами j-го и (2n-1 + j)-го сумматоров первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра первой группы, прямой выход (2n + 2j - 1)-го регистра первой группы соединен с третьими входами j-го и (2n-1 + j) сумматоров первой группы, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра первой группы, отличающееся тем, что, с целью повышения быстродействия, оно содержит с (2n + 1)-го по 2n+1-й блоки элементов ИЛИ и 2n+1 регистров второй группы, причем 2i-й информационный вход устройства соединен с информационным входом (3 · 2n + i)-го блока элементов И, управляющий вход которого соединен с управляющим входом ввода информации устройства, выходы (3 · 2n + i)-го и (2n+1 + i)-го блоков элементов И соединены с входами (2n + i)-го блока элементов ИЛИ, выход которого соединен с информационным входом (2n + i)-го регистра первой группы, тактовый вход которого соединен с одноименным входом i-го регистра первой группы и первым тактовым входом устройства, второй тактовый вход которого соединен с одноименными входами всех регистров второй группы, выходы (2i - 1)-го и 2i-го регистров которой соединены с входами i-го сумматора второй группы и являются i-м двустрочным выходом второй группы устройства, прямой выход i-го регистра первой группы соединен с информационным входом (2i - 1)-го регистра второй группы, информационный вход 2i-го регистра второй группы соединен с прямым выходом (2n + i)-го регистра первой группы.

) соединен с первыми входами j-го и (2n-1 + j)-го сумматоров первой группы, вторые входы которых соединены соответственно с прямым и инверсным выходами 2j-го регистра первой группы, прямой выход (2n + 2j - 1)-го регистра первой группы соединен с третьими входами j-го и (2n-1 + j) сумматоров первой группы, четвертые входы которых соединены соответственно с прямым и инверсным выходами (2n + 2j)-го регистра первой группы, отличающееся тем, что, с целью повышения быстродействия, оно содержит с (2n + 1)-го по 2n+1-й блоки элементов ИЛИ и 2n+1 регистров второй группы, причем 2i-й информационный вход устройства соединен с информационным входом (3 · 2n + i)-го блока элементов И, управляющий вход которого соединен с управляющим входом ввода информации устройства, выходы (3 · 2n + i)-го и (2n+1 + i)-го блоков элементов И соединены с входами (2n + i)-го блока элементов ИЛИ, выход которого соединен с информационным входом (2n + i)-го регистра первой группы, тактовый вход которого соединен с одноименным входом i-го регистра первой группы и первым тактовым входом устройства, второй тактовый вход которого соединен с одноименными входами всех регистров второй группы, выходы (2i - 1)-го и 2i-го регистров которой соединены с входами i-го сумматора второй группы и являются i-м двустрочным выходом второй группы устройства, прямой выход i-го регистра первой группы соединен с информационным входом (2i - 1)-го регистра второй группы, информационный вход 2i-го регистра второй группы соединен с прямым выходом (2n + i)-го регистра первой группы.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство быстрого преобразования Уолша-Адамара | 1985 |

|

SU1377871A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-15—Публикация

1991-01-09—Подача