ния подключен к третьему входу третьего блока памяти, пятый выход блока управления подключен к третьим входам пятого блока памяти и второго буферного блока памяти, шестой выход блока управления подключен к вто рому входу ключа, второй выход которого подключен к второму входу вычитателя, седьмой выход блока управления подключен к третьему входу ключа и второму входу четвертого блока памяти, восьмой выход блока управления подключен к второму входу делителя и третьему входу четвертого блока па мяти, девятый выход блока управления подключен к второму входу первого сумматора, десятый выход блока управ ления подключен к третьему входу делителя . 2. Устройство по П.1, отличающееся тем, что блок управ ления содержит генератор тактовых импульсов, элементы сравнения, регистры, счетчики, триггеры и элементы И, выход генератора тактовых импульсов подключен к первым входам первого, второго, третьего и четвертого элементов И, выходы первого и второго элементов И подключены соответственно через первый и второй счетчики.к первым входам первого и второго элементов сравнения, выход первого элемента сравнения подключен через первый регистр к второму входу первого элемента сравнения и первому входу первого триггера, первый и второй выходы которого подключены соответственно к вторым входам первого и второго элементов И, выход второго элемента сравнения подключен к входу второго регистра и второму входу третьего элемента И, выход ко-. торого подключен к второму входу пер вого триггера, первый и второй выходы которого подключены к вторым входам соответственно первого и второго элементов И, первьш и второй выходы второго регистра ,подключе: ы соответственно к второму входу второго элемента сравнения и первому входу второго триггера, первый выход которого подключен к первому входу третьего триггера, первый выход которого подключен к третьим входам первого и второго элементов И, второй выход третьего триггера подключен к второму входу четвертого элемента И, выход которого подключен к первым входам пятого и шестого элементов И, выход пятого элемента И через третий счетчик подключен к первому входу четвертого триггера, первый и второй выходы которого подключены соответственно к вторым входам пятого и шестого элементов И, выход шестого элемента И подключен к входу четвертого счетчика, выход которого подключен к второму входу четвертого триггера и второму входу третьего триггера, второй вход второго триггера является входом блока управления, выход генератора тактовых имдульсов, первый и второй вькоды четвертого триггера, первый выход третьего триггера, второй выход второго триггера, второй и первый выходы первого триггера, выход первого элемента сравнения, выход второго элемента сравнения и выход первого регистра являются соответственно первым-десятым выходами: блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Устройство для сбора и анализа данных о работе информационно-вычислительной системы | 1990 |

|

SU1795476A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| Устройство для сопряжения абонентов с каналами связи | 1984 |

|

SU1233158A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ СБОРОЧНЫМ УСТРОЙСТВОМ | 1991 |

|

RU2029335C1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

1. УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ, содержащее аналого-цифровой преобразователь, первый вход которого является информационным входом устройства, первый блок памяти, выход которого подключен к первому входу блока сравнения, блок управления, ,первый выход которого подключен к второму входу аналогоцифрового преобразователя, отличающееся тем, что, с целью повьшения пропускной способности, в него введены буферные блоки памяти, второй, третий, четвертый и пятый блоки памяти, блок ортогонального преобразования, сумматоры, регистр, делитель, вычитатель, квадратор и ключ, выход аналого-цифрового преобразователя подключен к первому входу первого буферного блока памяти, выход которого подключен к первому входу второго блока памяти, первый выход которого подключен к входу регистра, первый выход регистра подключен к первому входу третьего блока памяти, первый выход которого подключен к первому входу второго буферного блока памяти, выход которого является выходом устройства, второй выход третьего блока памяти подключен к первому входу ключа, первый выход которого подключен к первому входу первого сумматора, выход которого подключен к первому входу делителя, выход делителя подключен к nepBONry входу четвертого блока памяти, первый выход которого подключен к вто.рому входу второго буферного блока памяти, второй выход четвертого блока памяти подключен к первому входу вычитателя, выход которого через квадратор подключен к первому входу второго сумматора, выход второго сум(Л матора подключен к второму входу блока сравнения, выход которого подключен к второму входу второго сумматора и входу блока управления, первый выход которого подключен к второму входу первого буферного блока памяти, второй выход блока управления подключен к третьему входу первого буферного блока памяти и второму входу второго блока памяти, второй выход и третий вход второго блока памяти подключены соответственно к первому входу и выходу блока ортогональногопреобразования, третий выход блока управления подключен к второму входу блока ортогонального преобразования, четвертому входу второго блока памяти, второму входу третьего блока памяти и первому входу пятого блока памяти, второй вход которого подключен к второму выходу регистра,5выход пятого блока памяти подключен к второму входу второго буферного блока па- мяти, четвертый выход блока управле

1

Изобретение относится к устройствам Для связи и может быть использовано в системах, передачи телеметрических данных. I

Известно устройство для передачи телеметрической информации, содержащее на передающей стороне последовательно соединенные датчики, блок прямого ортогонального преобразователя

Уолша, коммутатор, аналого-цифровой преобразователь, блок считьшания и передатчик, на приемной стороне блок промежуточной памяти, цифроаналоговьй преобразователь, дешифратор адреса и блок обратного ортогонального преобразователя Уолша 3.

Недостатком известного устройства является избыточность передаваемых

данных, так как количество передаваемых сигналов спектральных компонент постоянно и не зависит от динамичности исходного процесса.

Наиболее близким к предлагаемому является устройство для передачи телеметрической информации, содержащее последовательно соединенные коммутатор, аналого-цифровой преобразователь и блок считывания, выходы аналогоцифрового преобразователя подключены к первым входам схемы сравнения, а также через блок памяти - к вторым входам схемы сравнения, выход которой через счетчик подключен к вторым входам блока считывания и первому входу блока управления, выход которого подключен к второму входу аналого-цифрового преобразователя и схемы запуска, выход которой подключен к вторьп- входам коммутатора и блока памяти, вторые выводы блока считывания и схемы сравнения подключены соответственно к второму и третьему входам схемы запуска С 2 .

Недостатком описанного устройства является малая пропускная способность, обусловленная избыточностью передаваемых данных.

Цель изобретения - повышение пропускной способности устройства.

Поставленная цель достигается тем, что в устройство, содержащее аналого-цифровой преобразователь, первый вход которого является информационным входом устройства, первьш блок-памяти, выход которого подключен к первому входу блока сравнения, блок управления,первый выход которого подключен к второму входу аналого цифрового преобразователя,введены буферные блоки памяти, второй, третий, четвертый и пятый блоки.памяти, блок ортогонального преобразования, сумматоры, регистр, делитель, вычитатель, квадратор и ключ, выход аналого-цифрового преобразователя. подключен к первому входу первого буферного блока памяти, выход которого .подключен к первому входу второго блока памяти, первый выход которого подключен к входу регистра, первый выход регистра подключен к первому входу третьего блока памяти, первый выход которого подключен к первому входу второго буферного -блока памяти, выход которого является выходом устройства, второй выход третьего

блока памяти подключен к первому входу ключа, первый выход которого подключен к первому входу первого сумматора, выход которого подключен к первому входу делителя, выход делителя подключен к первому входу четвертого блока памяти, первьй выход которого подключен к второму входу второго буферного блока памяти, второй выход четвертого блока памяти подключен к первому входу вычитателя, вькод которого через квадратор подключен к первому входу второго сумматора, выход второго сумматора подключен к второму входу блока сравнения, выход которого подключен к второму входу второго сумматора и входу блока управления , первьй выход которого подключен к второму входу первого буферного блока памяти,.второй выход блока управления подключен к третьему входу первого буферного блока памяти и второму входу второго блока памяти, второй выход и третий вход второго блока памяти подключены соответственно к первому входу и выходу блока ортогонального преобразования,третий |Выход блока управления подключен к второму входу блока ортогонального преобразования, четвертому входу второго блока памяти, второму входу третьего блока памяти и первому входу пятого блока памяти, второй вход которого подключен к второму выходу регистра, выход пятого блока памяти подключен к второму входу второго буферного блока памяти, четвертьй выход блока управления подключен к третьему входу третьего блока памяти пятый выход блока управления подключен к третьим-входам пятого блока памяти и второго буферного блока памяти, шестой выход блока управления подключен к второму входу ключа, второй выход которого подключен к второму входу вычитателя, седьмой выход блока упрагления подключен к третьему входу ключа и второму входу четвертого блока памяти, восьмой выход блока управления подключен к второму входу делителя и третьему входу четвертого блока памяти, девятый выход блока управления подключен к второ- му входу первого сумматора, десятый выход блока управления подключен к третьему входу делителя.

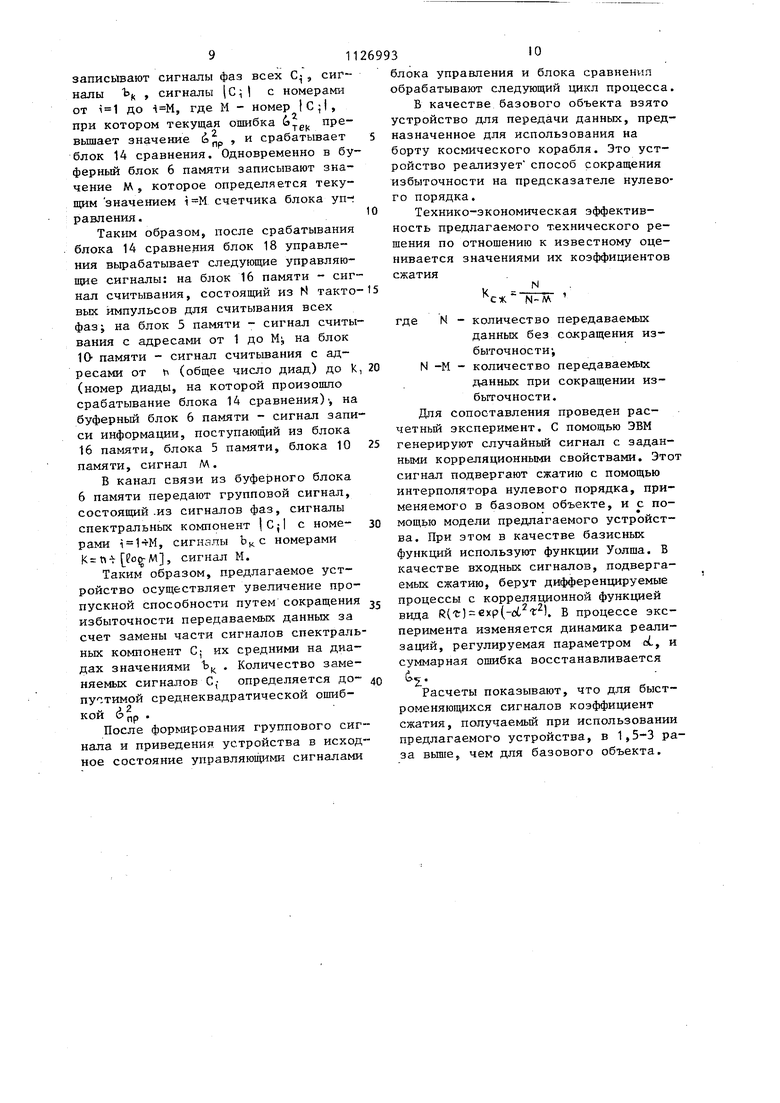

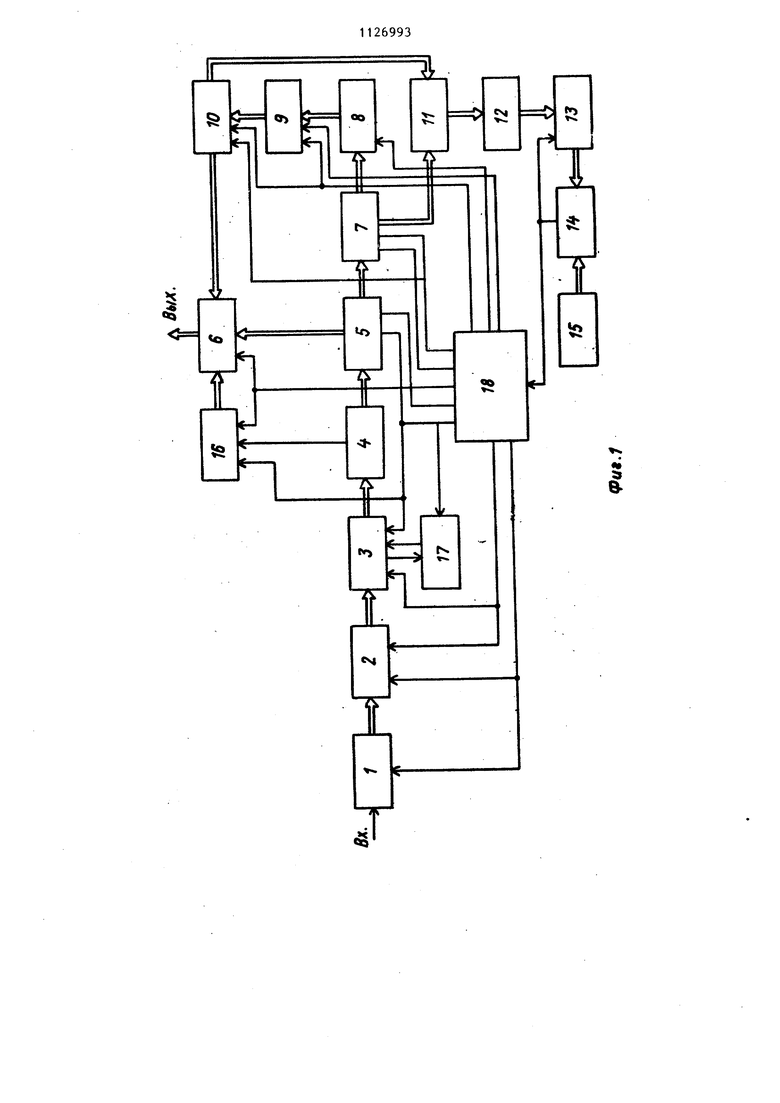

Кроме того, в блок управления введены генератор тактовых импульсов элементы сравнения, регистры, счетчики, триггеры и элементы И, выход генератора тактовых импульсов подклю чен к первым входам первого, второго, третьего и четвертого элементов И, выходы первого и второго элементов И подключены соответственно через первый и второй счетчики к пер вым входам первого и второго элементов сравнения, выход первого элемента сравнения подключен через первый регистр к второму входу первого элемента сравнения и первому входу первого триггера, первый и второй выходы которого подключены соответственно к вторым входам первого и второго элементов И, выход второго элемента сравнения подключен к входу второго регистра и второму входу третьего элемента И, выход которого подключен к второму входу первого триггера, первый и второй выходы которого подключены к вторым входам соответственно первого -vi второго эле ментов И, первый и второй выходы второго регистра подключены соответственно к второму входу второго элемента сравнения и первому входу вто роге триггера, первьм выход которого подключен-к первому входу третьего триггера, первый выход которого подключен к третьим входам первого и второго элементов И, второй выход третьего триггера подключен к второму входу четвертого элемента И, выход которого подключен к первым входам пятого и шестого элементов И, выход пятого элемента И через третий счетчик подключен к первому входу четвертого триггера, первый и второй выходы которого подключены соответственно к вторым входам пятого и шестого элементов И, выход шестого элемента И подключен к входу четвертого счетчика, выход которого подклю чен к второму входу четвертого триггера и второму входу третьего триггера, второй вход второго триггера является входом блока управления, вы ход генератора тактовых импульсов пер вый и второй выходы четвертого триггера первый выход третьего триггера5второй выход второго триггера,второй и первый выходы первого тригерра, первого элемента сравнения,выход второго эле мента сравнения и выход первого регисТ ра являются соответственно первым де сятым выходами блока управления. На фиг.1 приведена схема предлагаемого устройства; на фиг.2 - схема блока управления. Устройство содержит аналого-цифровой преобразователь (АЦП) 1, буферный блок 2 памяти, блок 3 , регистр 4, блок 5 памяти-, буферный блок 6 памяти, ключ 7, первый сумматор 8, делитель 9, блок 10 памяти, вьгчитатель 11,, квадратор 12, второй сумматор 13, блок 14 сравнения, блок 15 памяти, блок 16 памяти, блок 17 ортогонального преобразования и блок 18 управления, содержащий генератор 19 тактовых импульсов, элементы И 20-25, счетчики 26-29, регистры 30 и 31, элементы 32 и 33 сравнения, триггеры 34-37. Выходы блока 18 управления соединены с управляющим 1 входами блоков следующим образом: первый выход блока управления подключен к тактирующему входу АЦП 1 и входу разрешения записи буферного блока 2 памяти; второй выход подключен к входу разрешения считывания буферного блока 2 памяти и входу разрешения записи блока 3 памяти, третий выход подсоединен к тактирующему входу блока 17 ортогонального преобразования, входу разрешения считывания блока 3 памяти, входу разрешения записи блока 16 памяти и входу разрешения записи блока 5 памяти, четвертьй выход соединен с входом разрешения считывания блока 5 пвлмяти, девятый вькод соединен с входом обнуления первого (накапливающего) сумматора 8, восьмой вькод соединен с входом разрешения записи блока 10 и управляющим входом делителя 9J десятый выход подключен к первому информационному входу делителя 9, шестой выход подключен к первому управляющему входу ключа 7 седьмой выход соединен с вторым управляющим входом ключа и входом разрешения считьшания блока 10 памяти, пятый выход соединен с входом разрешения считьюания блока 16 памяти и входом разрешения записи буферного блока 6 памяти. Блок 18 управления вырабатывает управляющие сигналы: тактовые импульсы, сигналы разрешения записи и считьшания для блоков памяти, сигнал начала ортогонального.преобразования, сигнала обнуления первого накапливающего сумматора, сигнал управле,ния делителем,, сигнал управления .ключом , 1 Сигнал сброса второго накапливающего сумматора поступает с выхода блока сравнения. Устройство работает следующим образом. Перед работой задают количество цифровых сигналов N 2 , получаемых на выходе АЦП 1, и устанавливают допустимую ошибку преобразования с помощью клавиатуры в блоке 15 памяти. На выходе АЦП 1 с частотой тактовых импульсов, поступающих от блока 18 управления, получают N сигналов цифровых отсчетов х., которые записывают в буферньпЧ блок 2 памяти. По управляющему сигналу от блока управления эти сигтлы считывают из бу ферного блока 2 памяти и записывают в блок 3 памяти. В блоке 17 ортогонального преобразования по сигналу начала преобразования от блока управ ления получают М сигналов спектральных компонент С., которые записывают в блок 3 памяти по мере их вычислени и переписывают в регистр 4,.где разделяют сигналы С на абсолютные значения (модули) и фазы, В случа использования ортогонального преобра зователя Уолша фазой сигнала С- является его знак. Содержание знаковог разряда регистра 4 записывают в блок 16 памяти, а содержание остальных разрядов (модули) - в блок 5 памяти. Затем работа устройства ведется в двух последовательных режимах, управ ление которыми осуществляют по сигналам блока управления. В первом режиме N сигналов Ic I .считьшают из блока 5 памяти в. первый накапливающи сумматора 8 по диодам через ключ 7. Диада - группа сигналов Cjl в количестве 2, где К - номер текуще диады. Адреса границ диад записывают в кольцевые регистры блока управления до начала работы. Считывание сиг налов С. производят в обратном порядке: от до 1 1 . По сигналу блока управления, соответствующему концу первой обрабатываемой диады, на выходе делителя 9 формируют сигнал, пропорциональный среднему значению сигналов , где количество сигналов|С | К-й диаде. Значения N подают на делитель 9 с блока управления. Для , количество диад 5, границы диад приведены в таблиЗначение сигнала Ьц записывают в блок 10 памяти. После этого первый накапливающий сумматор 8 обнуляют сигналом с блока 18 управления. Во втором режиме сигналы через ключ 7 подают на первый вход вычитателя 11, на второй вход которого подают из блока 10 памяти сигнал Ъц . Разностный сигнал (), получаемьй на выходе вычитателя 11, возводят квадрат в квадраторе 12 и подают на второй накапливающий сумматор 13, на.выходе которого получают сигнал ек-(С,-Ч) которьй подают на блок 14 сравнения. На другой вход блока сравнения подают с блока 15 памяти сигнал допустимой опшбки преобразования . Если сигнал ( не превышает значения сигнала , то определяют сигнал Ьк. для следующей диады и т.д. При превьшении сигналом сигнала (ЭПР срабатывает блок 14 сравнения и сигнал с его выхода подают на блок управления, который вьфабатывает сигнал разрешения считывания сигналов фаз из блока 16 памяти и сигнал разрешения записи буферного блока 6 памяти, по которому в этот блок у1 записывают сигналы фаз всех С, сигналы Ь , сигналы (Ci1 с номерами от i 1 до , где М - номер 1С-|, при котором текущая ошибка ( превышает значение ( , и срабатывает блок 14 сравнения. Одновременно в бу ферный блок 6 памяти записывают значение М, которое определяется текущим значением i М счетчика блока уп-; равления. Таким образом, после срабатывания блока 14 сравнения блок 18 управления вырабатывает следующие управляющие сигналы: на блок 16 памяти - сиг нал считывания, состоящий из Н такто вых импульсов для считывания всех фаз J на блок 5 памяти - сигнал считы вания с адресами от 1 до М на блок 1О памяти - сигнал считьшания с адресами от ь (общее число диад) до К (номер диады, на которой произошло срабатывание блока 14 сравнения), на буферный блок 6 памяти - сигнал запи си информации, поступающий из блока 16 памяти, блока 5 памяти, блока 10 памяти, сигнал М. В канал связи из буферного блока 6 памяти передают групповой сигнал, состоящий-ИЗ сигналов фаз, сигналы спектральных компонент |С;| с номерами 1 1-тМ, сигналы Ь с номерами , сигнал М. Таким образом, предлагаемое устройство осуществляет увеличение пропускной способности путем сокращения избыточности передаваемых данных за счет замены части сигналов спектраль ных компонент Cj их средними на диадах значениями Ь . Количество заменяемых сигналов С; определяется допустимой среднеквадратической опшбё.2 После формирования группового сиг нала и приведения устройства в исход ное состояние управляющими сигналами 310 блока управления и блока сравненил обрабатывают следующий цикл процесса. В качестве базового объекта взято устройство для передачи данных, предназначенное для использования на борту космического корабля. Это устройство реализует способ сокращения избыточности на предсказателе нулевого порядка. Технико-экономическая эффективность предлагаемого технического решения по отношению к известному оценивается значениями их коэффициентов сжатия ,. N. N-Ж где N - количество передаваемых данных без сокращения избыточности;N -М - количество передаваемых данных при сокращении избыточности. Для сопоставления проведен расчетный эксперимент. С помощью ЭВМ генерируют случайный сигнал с заданными корреляционными свойствами. Этот сигнал подвергают сжатию с помощью интерполятора нулевого порядка, применяемого в базовом объекте, и с помощью модели предлагаемого устройства. При этом в качестве базисных функций используют функции Уолша. В качестве входных сигналов, подвергаемых сжатию, берут дифференцируемые процессы с корреляционной функцией вида R(r) exp(). в процессе эксперимента изменяется динамика реализаций, регулируемая параметром oL, и суммарная ошибка восстанавливается Расчеты показывают, что для быстроменяющихся сигналов коэффициент сжатия, получаемьм при использовании предлагаемого устройства, в 1,5-3 раза Bbmie, чем для базового объекта.

и

AUt

ч

Сл

Г «

«У N

fs.

«ч

CSI

7 и k

1126993 А

мг

е-

§ с-1

v ««

«Ч

«ч

г

ЭО k

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Телеизмерительная система | 1979 |

|

SU805380A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авдеев Б.Я | |||

| Адаптивные телеизмерительные системы | |||

| Энергоиздат, 1981, с | |||

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

Авторы

Даты

1984-11-30—Публикация

1983-08-03—Подача