i. . 1

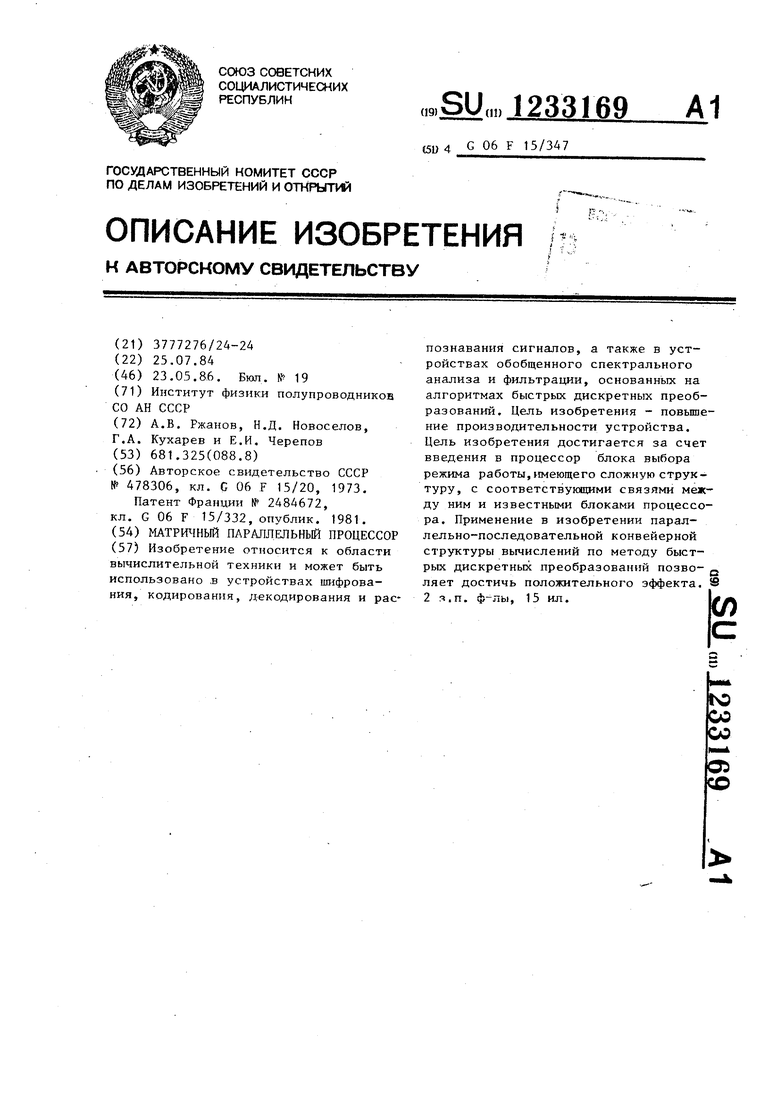

Изобретение относится к вычислительной технике и может быть использовано в устройствах шифрования,кодирования, декодирования и распознавания сигналов5 а также в устройствах обоб- ценного спектрального анализа и фильтрации, основанных на алгоритмах быстрых дискретных преобразований.

Цель изобретения - повьшюние производительности устройства. -

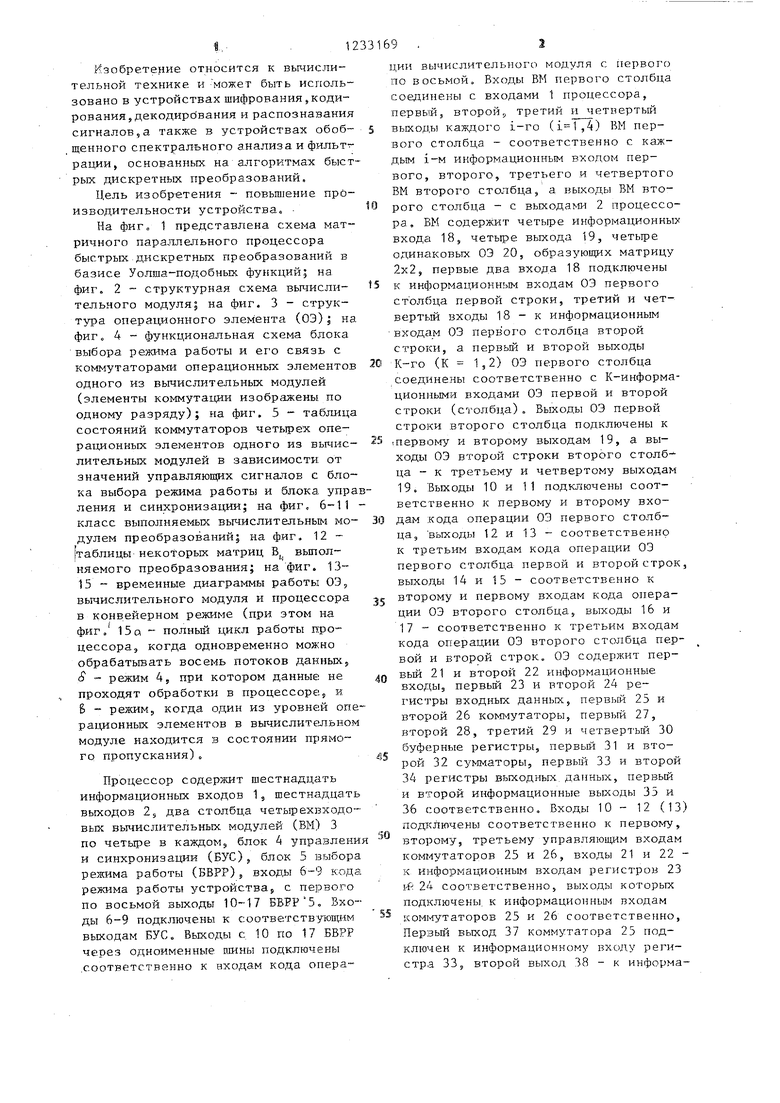

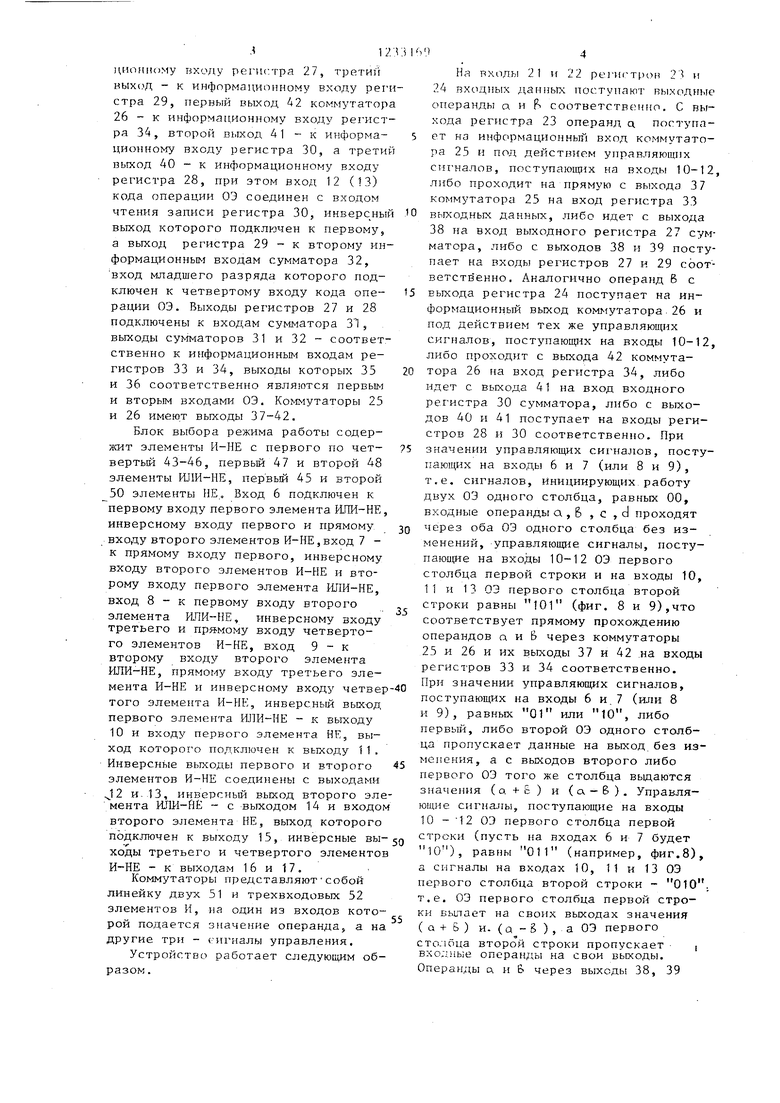

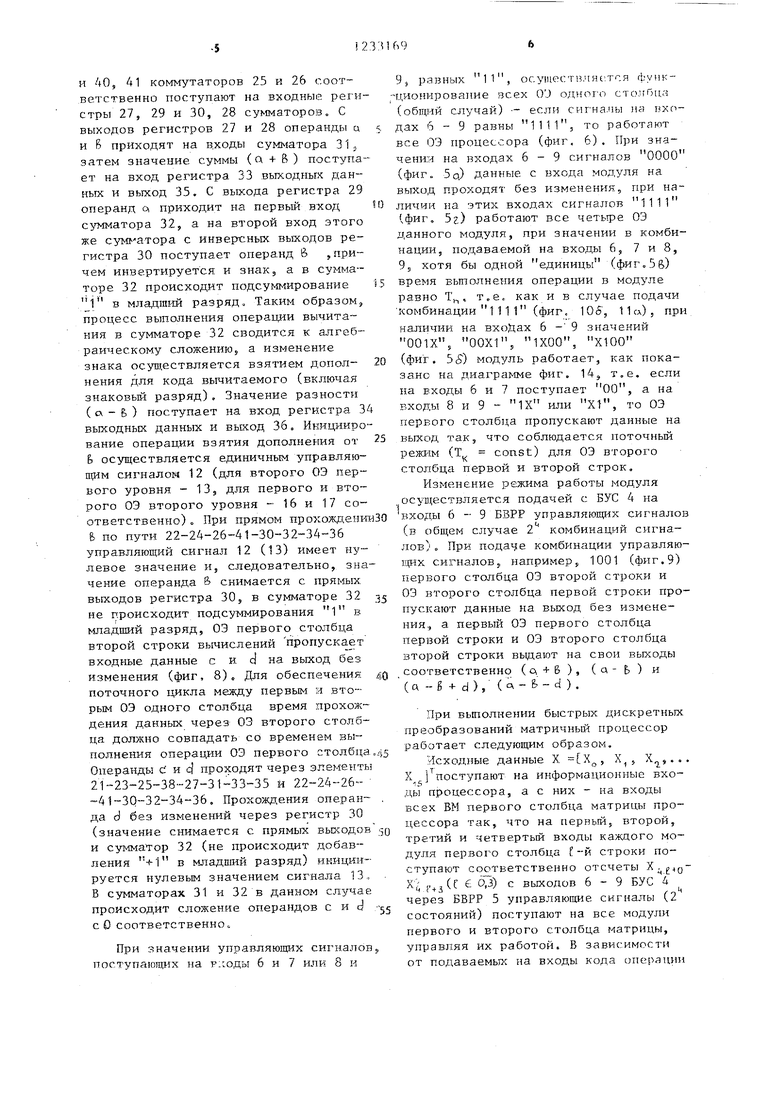

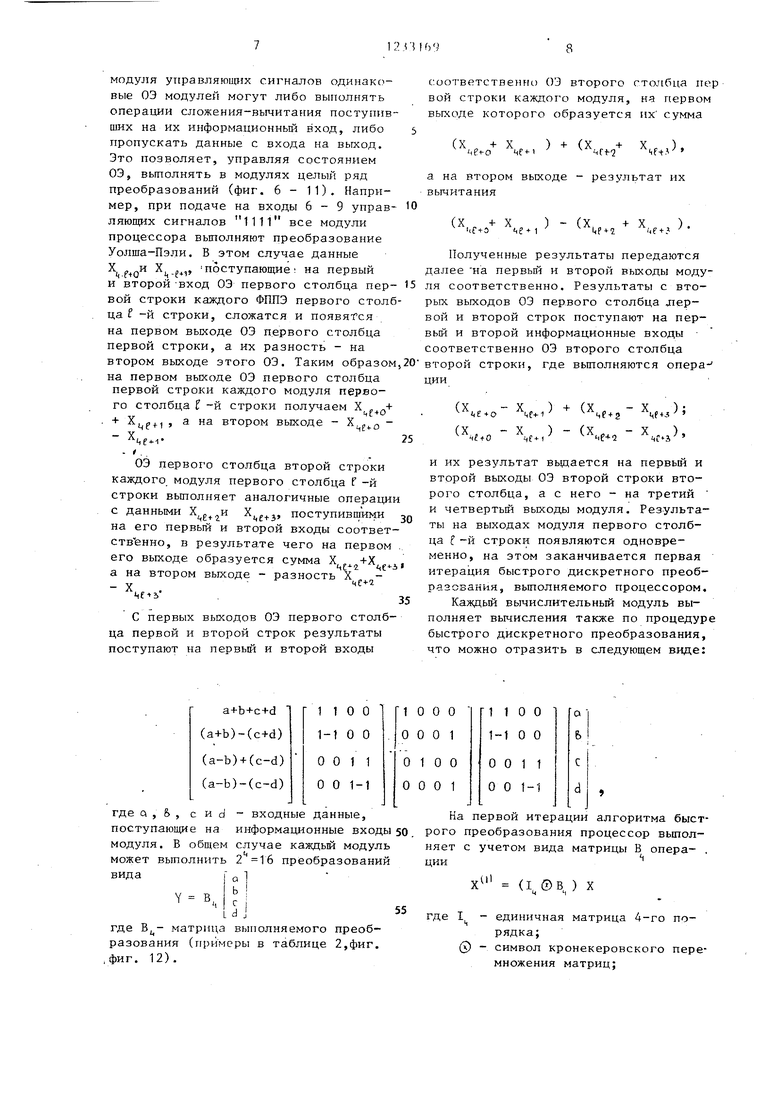

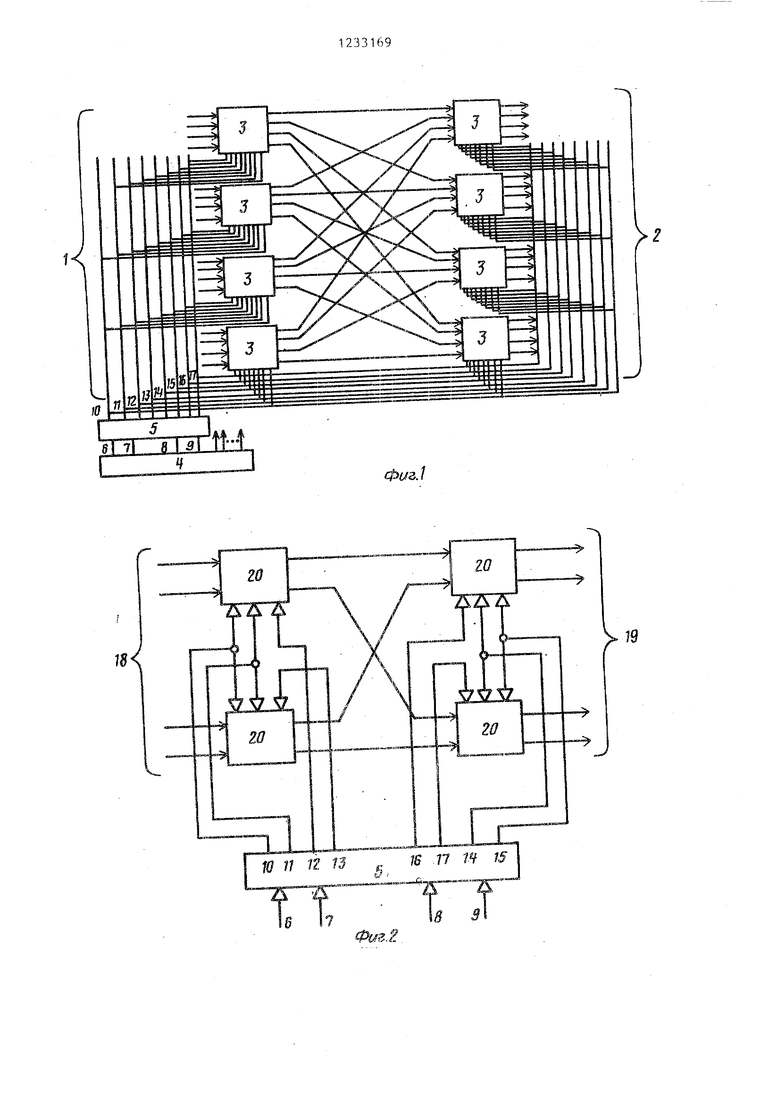

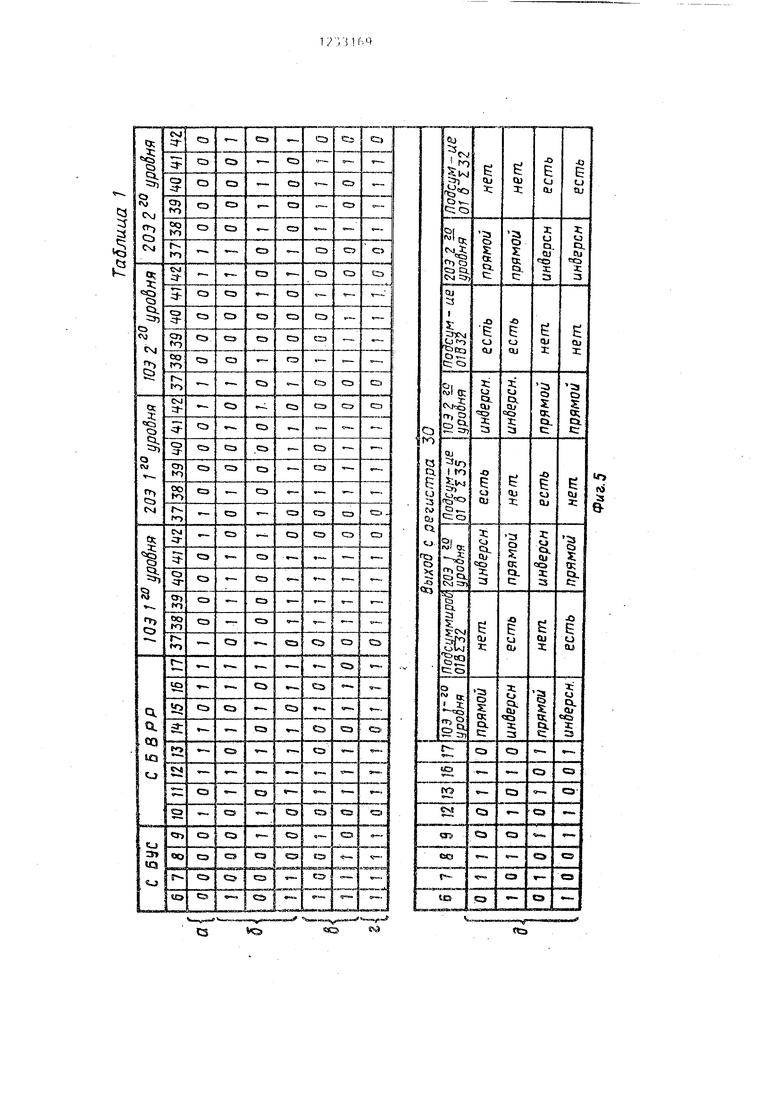

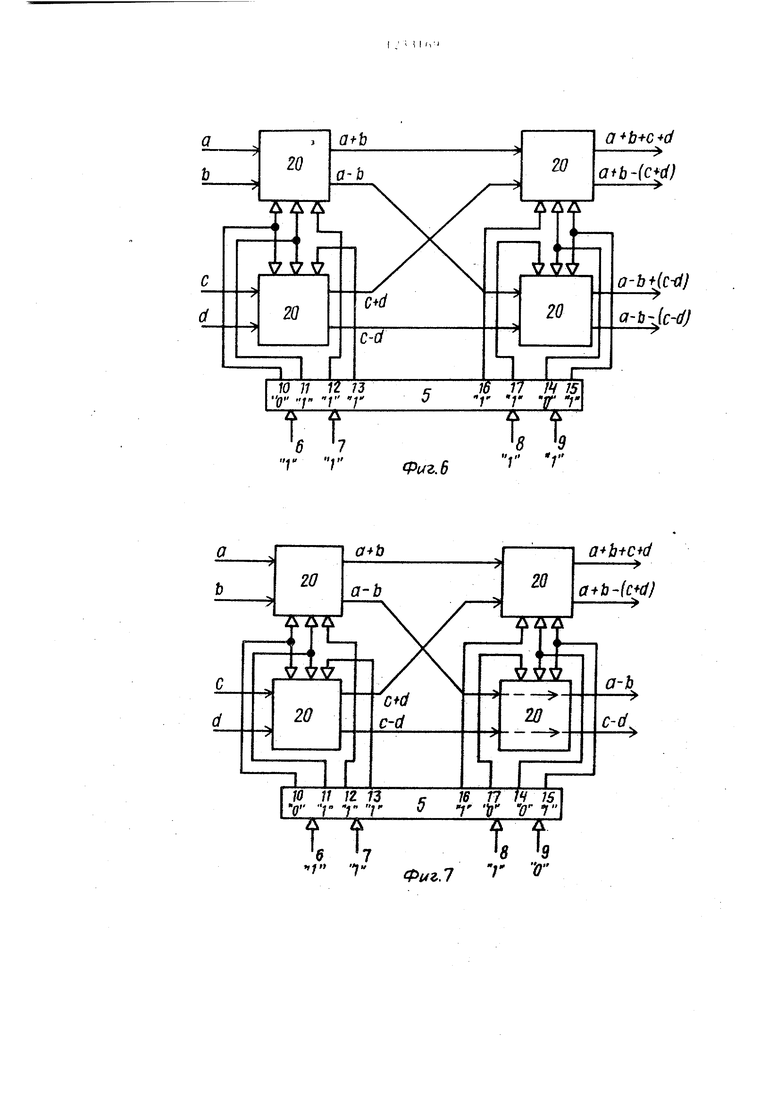

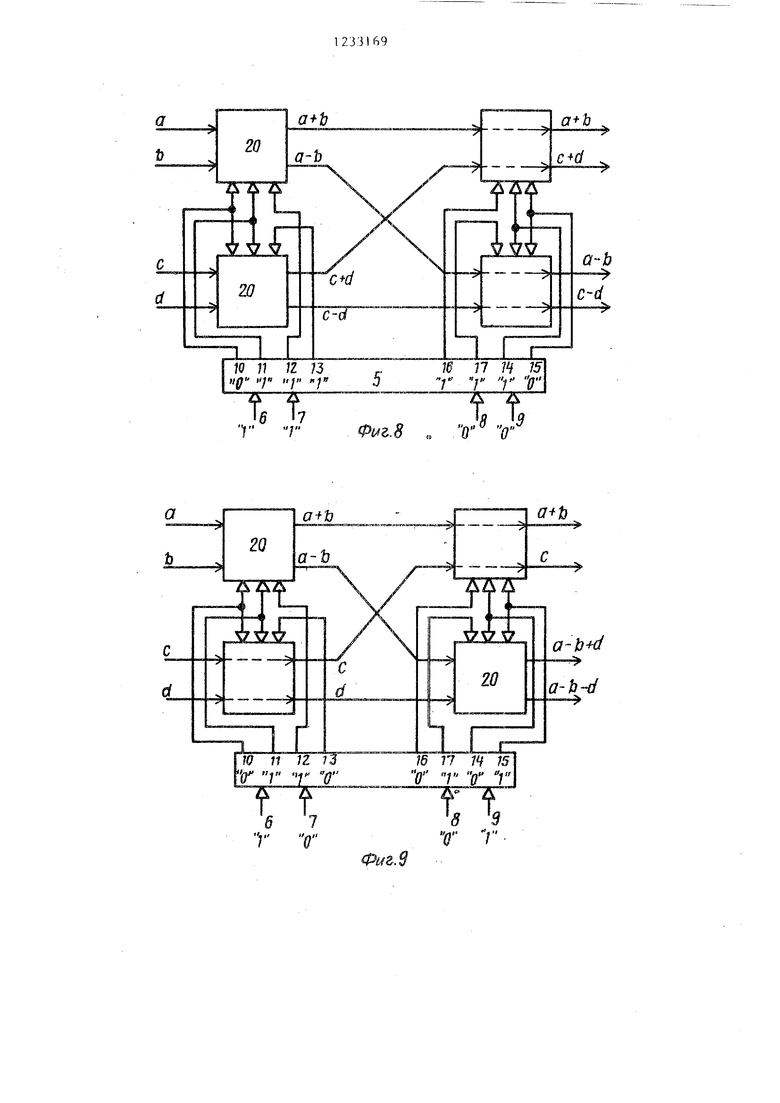

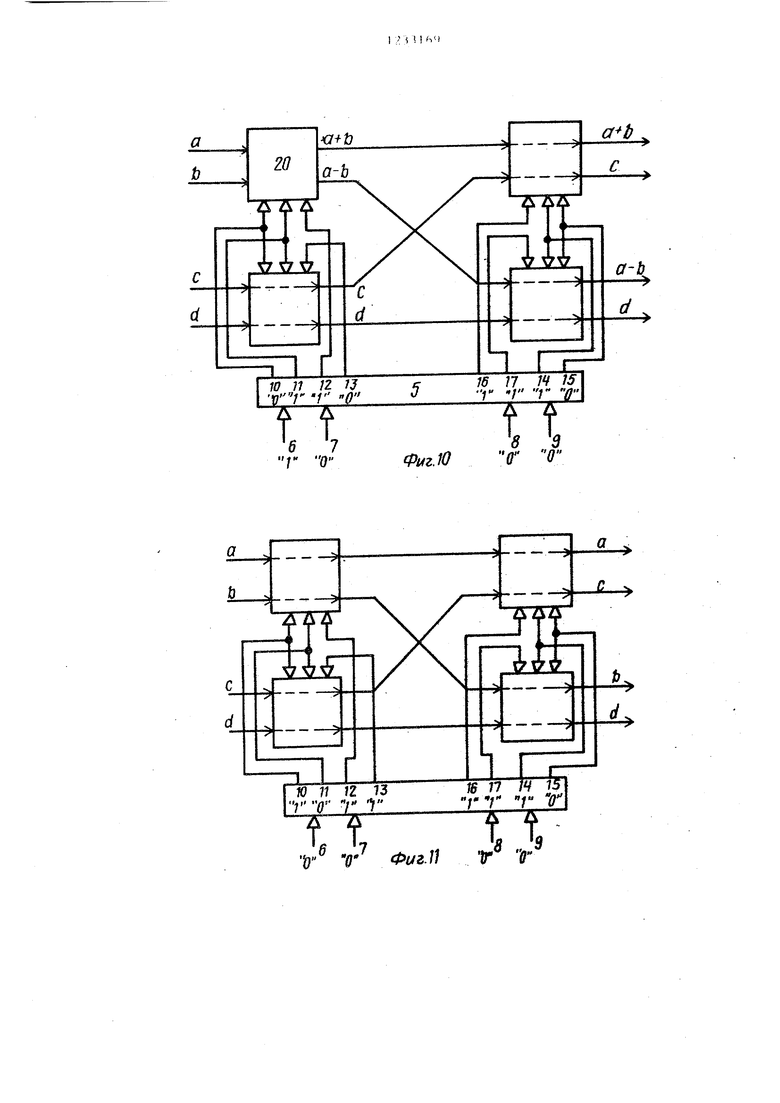

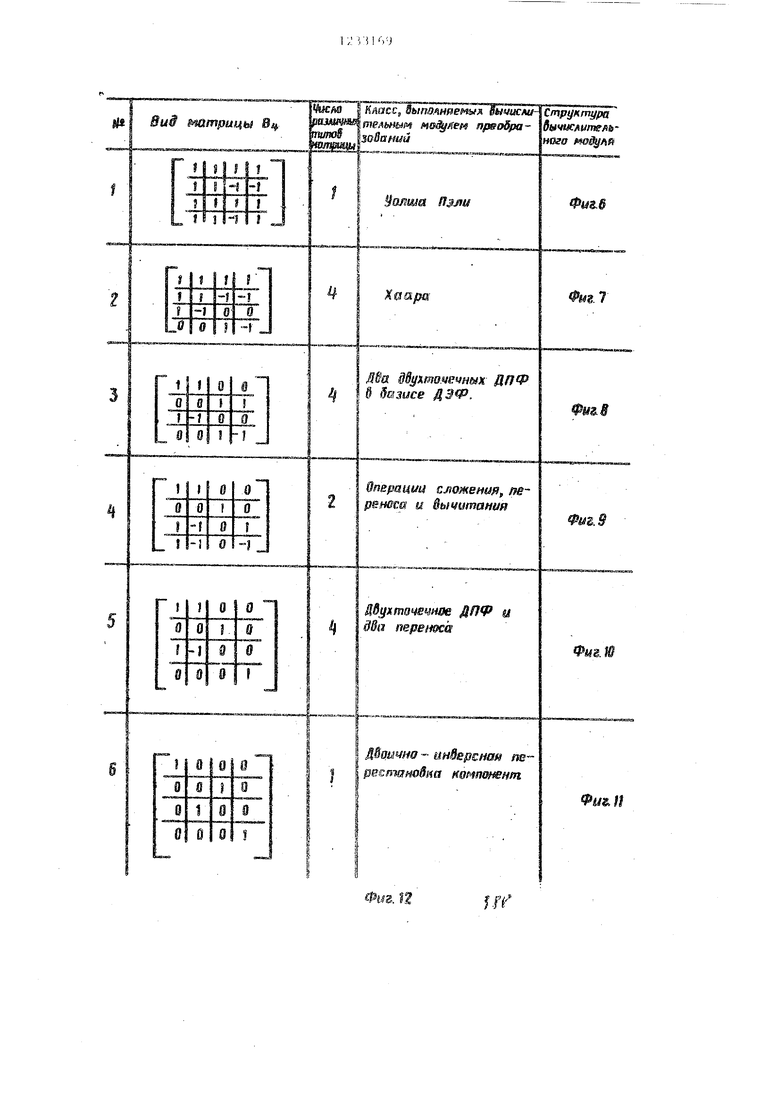

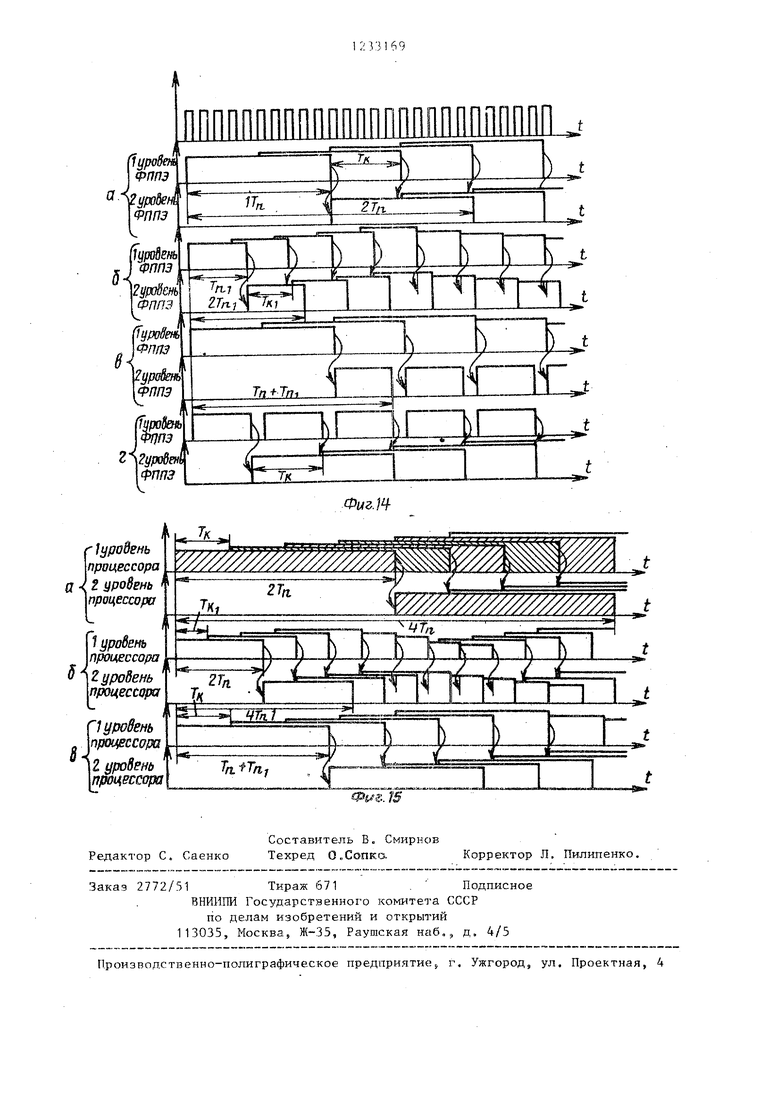

На фиго 1 представлена схема матричного параллельного процессора быстрых дискретных преобразований в базисе Уолша-подобных фу1 кций; на фиг. 2 структурная схема вычисли- тельного модуля; на фиг. 3 - структура операционного элемента (ОЭ)j на фиг о 4 - функциональная схема блока выбора режима работы и его связь с коммутаторами операционных элементов одного из вычислительных модулей (элементы коммутации изображены по одному разряду); на фиг. 5 - таблица состояний коммутаторов четырех операционных элементов одного из вычислительных модулей в зависимости от значений управляющих сигналов с блока выбора режима работы и блока, упраления и синхронизации; на фиг, 6-11 класс выполняемых вычислительным мо- дулем преобразований; на фиг. 12 - таблицы некоторых матриц В вьтол- няемого преобразования; на фиг. 13 15 - временные диагра1 ШЫ работы 03, вычислительного модуля и процессора в конвейерном режиме (при этом на фиг. 15а - полный цикл работы процессора, когда одновременно можно обрабатьгоать восемь потоков данных, S - режим 4, при котором данные не

проходят обработки в процессоре, и S - режим, когда один из уровней операционных элементов в вычислительном модуле находится в состоянии прямого пропускания).

Процессор содержит шестнадцать информационных входов 1, шестнадцать выходов 2; два столбца четьфехвходо- вык вычислительных модулей (ВМ) 3 по четьфе в каждомj блок 4 упразлени и синхронизации (БУС), блок 5 выбора режима работы (БВРР), входы 6-9 кода режима работы устройства с первого по восьмой выходы 10-17 БВБР Зо Входы 6-9 подключены к соответствующим выходам БУС, Выходы с 10 по 17 БВРР через одноименные ашны подключены .соответственно к входам кода операдни вычислительного модуля с первого по восьмой. Входы ВМ первого столбца соединены с входами 1 процессора, первьш, второй5 третий и четвертый выходы каждого i-ro (,4) ВМ первого столбца - соответственно с каждым i-M ииформационнь м входом первого, второго, третьего и четвертого ВМ второго столбца, а выходы БМ второго столбца - с выходами 2 процессора, БМ содержит четьфе информационных входа 18, четьфе выхода 19, четыре

5 0 0-5,5

S

40

45

одинаковых ОЭ 20, образующих матрицу 2x2, первые два входа 18 подключены к информационным входам ОЭ первого столбца первой строки, третий и чет- вертьй входы 18 - к информационным входам ОЭ первого столбца второй строки, а первый и второй выходы К-го (К 1,2) ОЭ первого столбца соединены соответственно с К-информа- ционными входами ОЭ первой и второй стро):и (столбца) . Выходы ОЭ первой строки второго столбца подключены к .первому и второму выходам 19, а выходы 03 второй строки второго столб- ца - к третьему и четвертому выходам 19, Выходы 10 и 11 подключены соответственно к первому и второму входам кода операции ОЭ первого столбца, выходы 12 и 13 - соответственно к третьим входам кода операции ОЭ первого столбца первой и второй строк, выходы 14 и 15 - соответственно к второму и первому входам кода операции ОЭ второго столбца, выходы 16 и 17 - соответственно к третьим входам кода операции ОЭ второго столбца первой и второй строк. ОЭ содержит пер- вьш 21 и второй 22 информационные входьц первый 23 и второй 24 регистры входных данных, первый 25 и второй 26 коммутаторы, первый 27, второй 28, третий 29 и четвертый 30 буферные регистры, первьй 31 и второй 32 сумматоры, первый 33 и второй 34 регистры выходных, данных, первьй и второй информационные выходы 35 и 36 соответственно. Входы 10 - 12 (13) подключены соответственно к первому, второму, третьему управляющим входам коммутаторов 25 и 26, входы 21 и 22 - к информационнь м входам регистров 23 tft 24 соответственно5 выходы которых подключены, к информационньм входам KOMi iyTaTopOB 25 и 26 соответственно, Перзьш выход 37 коммутатора 25 подключен к информационному входу регистра 33, второй выход 38 - к информал,нони)му входу регистра 27, трети1 г вых(.д к информационЕЮму входу регстра 29, первый выход 42 коммутатор 26 - к информационному входу регистра 34, второй выход 41 к информа- ционному входу регистра 30, а трети выход 40 - к информационному входу регисгра 28, при этом вход 12 (13) кода операции ОЭ соединен с входом чтения записи регистра 30, инверс ный выход которого подключен к первому, а выход регистра 29 - к второму информационным входам сумматора 32, вход младшего разряда которого подключен к четвертому входу кода one- рации ОЭ. Выходы регистров 27 и 28 подключены к входам сумматора 31, выходы сумматоров 31 и 32 - соответственно к информационным входам регистров 33 и 34, выходы которых 35 и 36 соответственно являются первь -) и вторым входами ОЭ, Коммутаторы 25 и 26 имеют выходы 37-42.

Блок выбора режима работы содер- лшт элементы И-НЕ с первого по чет- вертый 43-46, первьй 47 и второй 48 элементы ШШ-НЕ, первый 45 и второй 50 элементы НЕ, Вход 6 подключен к первому входу первого элемента ИЛИ-НЕ,

инверсному входу первого и прямому

входу второго элементов И-НЕ,вход 7 - к прямому входу первого, инверсному входу второго элементов И-НЕ и второму входу первого элемента ШШ-НЕ, вход 8 - к первому входу второго элемента ЕГ1И-Р Е, инверсному входу третьего и прямому входу четвертого элементов И-НЕ, вход 9 - к второму входу второго элемента ИЛИ-НЕ, прямому входу третьего элемента И-НЕ и инверсному входу четвер того элемента И-НЕ, инверсный выход первого элемента ИЛИ-НЕ - к выходу 10 и входу первого элемента НЕ, выход которого подключен к выходу 11. Инверснь1е выходы первого и второго элементов И-НЕ соединены с выходами J2 И-13, инверсный выход второго элемента ИЛИ-ЙЕ - с выходом 14 и входо второго элемента НЕ, выход которого подключен к выходу 15, инверсные выходы третьего и четвертого элементо

И-НЕ - к выходам 16 и 17.

Коммутаторы представляют собой

линейку двух 51 и трехвходовых 52 элементов И, на один из входов которой подается значение операнда, а на другие три - (-игналы управления.

Устройство работает следующим образом .

5 О 5 20

95

JQ

0 5 o

5

5

На входы 21 и 22 ре игтров 2 и 24 вхсщных данных гтостунают р;ыходные операнды а и Р соответственно. С выхода регистра 23 операнд а поступает на информационный вход коммутатора 25 и под действием управляющих сих налов, поступающих на входы 10-12, либо проходит на прямую с выхода 37 коммутатора 25 на вход регистра 33 выходных данных, либо идет с выхода 38 на вход выходного регистра 27 сумматора, либо с выходов 38 и 39 поступает на входы регистров 27 и 29 соот- ветств енно. Аналогично операнд 6 с выхода регистра 24 поступает на информационный выход коммутатора.26 и под действием тех же управляющих сигналов, поступающих на входы 10-12, либо проходит с выхода 42 коммутатора 26 на вход регистра 34, либо идет с выхода 41 на вход входного регистра 30 сумматора, либо с вьгхо- дов 40 и 41 поступает на входы регистров 28 и 30 соответственно. При значении управляюгцих сигналов, поступающих на входы 6 и 7 (или 8 и 9), т.е. сигналов. Инициирующих, работу двух 03 одного столбца, равных 00, входные операнды а,6 , с ,d проходят через оба ОЭ одного столбца без изменений, управляющие сигналы, поступающие на входы 10-12 03 первого столбца первой строки и на входы 10, 11 и 13 03 первого столбца второй строки равны 101 (фиг. 8 и 9),что соответствует прямому прохождению операндов а и & через коммутаторы 25 и 26 и их выходы 37 и 42 на входы регистров 33 и 34 соответственно. При значении управляющих сигналов, поступающих на входы 6 и,7 (или 8 и 9), равных 01 или 10, либо первый, либо второй ОЭ одного столбца пропускает данные на выход,без изменения, а с выходов второго либо первого ОЭ того же столбца ВЕ)1даются значения ( о. + & ) и ( а - 6 ) . Управляющие сигналы, поступающие на входы 10 - 12 ОЭ первого столбца первой строки (пусть на входах 6 и 7 будет 10), равны 011 (например, фиг.8), а сигналы на входах 10, 11 и 13 ОЭ первого столбца второй строки - 010. т.е. ОЭ первого столбца первой строки вылает на своих выходах значения (Q+S) и. (а-й),аОЭ первого

столбца второй строки пропускает , входные операнды на свои выходы.

Операнды о. i 6 через выходы 38, 39

и 40, 41 коммутаторов 25 и 26 соответственно поступают на входные регистры 27, 29 и 30, 28 сумматоров, С выходов регистров 27 и 28 операнды ц и 6 приходят на в.ходы сушчатора 31 , затем значение суммы (а + В) поступает на вход регистра 33 вькодных данных и выход 35. С выхода регистра 29 операнд о, приходит на первый вход сумматора 32, а на второй вход этого же суда атора с инверпшых выходов регистра 30 поступает операнд 6 /причем инвертируется и знак, а в сумматоре 32 происходит подсуммирование i в младший разряд. Таким образом, процесс выполнения операц1ии вычитания в сумматоре 32 сводится к алгебраическому сложению а изменение знака осуществляется взятием допол- нения для кода вычитаемого (включая знаковый разряд). Значение разности (а - 6) поступает на вход регистра 3 выходных данных и выход 36. Инициирование операции взятия дополнения от 6 осуществляется единичным управляю- ЕЩм сигналом 12 (для второго ОЭ первого уровня - 13, для первого и второго ОЭ второго уровня - 16 и 17 соответственно) о При прямом прохождени е по пути 22-24-26-41-30-32-34-36 управляющий сигнал 12 (13) имеет нулевое значение и, следовательно, значение операнда 6 снимается с прямых, выходов регистра 30j в сумматоре 32 не происходит подсуммирования 1 в младпшй разряд, ОЭ первого столбца второй строки вычислений пропускает входные данные с и d на выход без изменения (фиг, 8). Для обеспечения поточного цикла между первым и вторым ОЭ одного столбца время прохождения данных через ОЭ второго столбца должно совпадать со временем выполнения операции ОЭ первого столбца Операнды С и ci проходят через элементы 21 23 25 38--27-31- 33-35 и 22-24-26-- -41-30-32-34-36, Прохождения операн- да d без изменений через регистр 30 (значение снимается с прямых выходов и сумматгор 32 (не происходит добавления +1 в младший разряд) инициируется нулевым значением сигнала 13, В сумматорах 31 и 32 в данном случае происходит сложение операндов с и d с О соответственно.

При значении управляющих сигналов поступающих на Р:СОДЫ 6 и 7 или 8 и

9, равных П, осушествлиЕ .тся функ- -ционировапие всех O J одног о (общий случай) - если сиг налы на входах 6-9 равны 1111, то работают все ОЭ процессора (фиг, 6). При значении на входах 6-9 сигналов 0000 (фиг, 5о.) данные с входа модуля на выход проходят без изменения, при наличии на этих входах сигналов 1111 (фиг, 5г) работают все четьфе 03 данного модуля, при значении в комбинации, подаваемой на входы 6, 7 и 8, 9э хотя бы одной единицы (фиг.5б) время вьтолнения операции в модуле равно Т,, т.е. как и в случае подачи комбинации 111 Г (фиг. 105, Па), при наличии на входах 6 - 9 значений 001Х, 00X1, 1X00, Х100 (фиг. 5S} модуль работает, как показано на диаграмме фиг. 14, т.е. если на входы 6 и 7 поступает 00, а на входы 8 и 9 - IX или Х1, то 03 первого столбца пропускают данные на выход так, что соблюдается поточньш режим (Т. const) для ОЭ второго

1

столбца первой и второй строк. Изменение режима работы модуля

.осуществляется подачей с БУС 4 на входы 6 - 9 БВРР управляющих сигналов (в общем случае 2 комбинаций сигналов) „ При поца в комбинации управляю- 1цих сигналов, например, 1001 (фиг. 9) первого столбца ОЭ второй строки и ОЭ второго столбца первой строки пропускают данные на выход без изменения,, а первый ОЭ первого столбца первой строки и ОЭ второго столбца строки выдают на свои выходы соответственно (с + 6), (а-Ь) и

(а - g + d ), ( - Ь - ) .

При выполнении быстрых дискретных преобразований матричный процессор работает следующим образом.

Исходные данные X Х, Х, Х,... Х поступают на информационные входы процессора, а с них - на входы всех ВМ первого столбца матрицы процессора так, что на первый, второй, третий и четвертый входы каждого модуля первого столбца Е-и строки поступают сос тветственно отсчеты Х,24о У- l i +a f выходов 6-9 БУС 4 через БВРР 5 управляющие сигналы (2 состояний) поступают на все модули первого и второго столбца матрицы, управляя их работой. В зависимости от подаваемьж на входы кода операции

модуля управляющих сигналов одинаковые ОЭ модулей могут либо выполнять операции сложения-вычитания поступивших на их информационный в ход, либо пропускать данные с входа на выход. Это позволяет, управляя состоянием ОЭ, выполнять в модулях целый ряд преобразований (фиг. 6 - 11). Например, при подаче на входы 6-9 управ- ляющих сигналов 1111 все модули процессора выполняют преобразование Уолша-Пэли. В этом случае данные X , Поступающие: на первый и второй -вход ОЭ первого столбца пер- вой строки каждого ФППЭ первого столбца f -и строки, сложатся и появятся на первом выходе ОЭ первого столбца первой строки, а их разность - на втором выходе этого ОЭ. Таким образом на первом выходе ОЭ первого столбца первой строки каждого модуля первого столбца t -и строки получаем X

+ Х(р, , а на втором выходе - X

- X

1,е-ц

ОЭ первого столбца второй строки каждого модуля первого столбца f-и строки выполняет аналогичные операции с данными ,и Х., поступившими о на его первый и второй входы соответ- ств енно, в результате чего на первом его выходе образуется сумма Х,+Х,, а на втором выходе - разность X

VЧС

е + ь35

С первых выходов ОЭ первого столбца первой и второй строк результаты поступают на первьй и второй входы

где Q, Б, с и d - входные данные, На первой итерации алгоритма быст- поступающие на информационные входы 50. рого преобразования процессор выпол- модуля. В общем случае каждьй модуль может выполнить 2 16 преобразований вида

няет с учетом вида матрицы В опера- .

ции

Y в,,

ь

55

Х (, ) X

где I - единичная матрица 4-го порядка;

где матрица выполняемого преобразования (примеры в таблице 2,фиг. ,фиг. 12).

с:оответственно ОЭ второго столбца пер вой строки каждого модуля, нч первом выходе которого образуется их сумма

е.о е., .г..X

i,ffA

).

з Ю 15 0

5

о

5

а на втором выходе - результат их вычитания

(..г./ е.1 - Р.. е.з)Полученные результаты передаются далее на первьй и второй выходы модуля соответственно. Результаты с вторых, выходов ОЭ первого столбца лер- вой и второй строк поступают на первьй и второй информационные входы соответственно ОЭ второго столбца второй строки, где вьшолняются опера- ции

. (Х.е.о- Vi) + ( f-)5 .o . .

и их результат вьщается на первьв1 и второй выходы ОЭ второй строки второго столбца, а с него - на третий и четвертый выходы модуля. Результаты на выходах модуля первого столбца f-и строки появляются одновременно, на этом заканчивается первая итерация быстрого дискретного преобразования, вьтолняемого процессором, Каждьй вычислительньй модуль выполняет вычисления также по процедуре быстрого дискретного преобразования, что можно отразить в следующем виде:

На первой итерации алгоритма быст- рого преобразования процессор выпол-

няет с учетом вида матрицы В опера- .

ции

На первой итерации алгоритма быст- рого преобразования процессор выпол-

Х (, ) X

где I - единичная матрица 4-го порядка;

0 - символ кронекеровского перемножения матриц;

х - вектор размера 16x1, компоненты которого определены в соответствии со структурой матриц В 1, ,

. Результаты выходов каждого модуля первого столбца строки цередают ся далее на f-тые входы модуля второго столбца, где над ними совершаются операции, аналогичные указанным, а в целом вьшолняется вторая итерация алгоритма быстрого преобразования

Х () х ,

Результаты на выходе модуля второ ;го столбца являются результатами вы- :полненного быстрого преобразования и передаются на выходы процессора. Если принять условно время сложения в сумматоре равным 2t хранения-выборки регистров, то в процессоре в общем случае можно одновременно обрабатывать восемь потоков данных (по. два потока в каждом 03 и, следовательно, по четыре потока в каждом модуле. Работа ОЭ, вычислительного модуля и процессора в конвейерном режиме отражена на временных диаграммах (фиг,13 - 15). Функционирование отдельных элементов процессора происходит синхронно по синхросигналам, инициируемым блоком 4,

Применение в предложенном процессоре параллельно-последовательной конв ейерной структуры вычислений по методу быстрых дискретных преобразований позволяет повысить его производительность.

Ф ормула изобретения

1. Матричный параллельный процессор, содержащий матрицу размером 4x2 вычислительных модулей, причем информационные входы вычислительных модулей первого столбца матрицы подключены к информационным входам процессора, первый, второй, третий,,чет вертыи выходы вычислительного модухгя первого столбца первой строки матрицы подключены к первым информационным входам вычислительных модулей вторг. Го столбца соответственно первой, второй, третьей, четвертой стро

матрицы, первые выходы вьгчислит«шь- ных модулей первого столбца второй, третьей и четвертой строк матриць; подключены соответственно к второму,

0

5

5

.5

третЕ.ему и четвертстму иш юрмлии тщилм входам вычислрггельного мод.у.чя первой строки второг о столбца матрицы, выходы вычислите. модулеГ второго столбца матрицы, подключены к инфс рмапц- онным выходам процессора, о т л и чающийся тем, что, с целью повьшкгния производительности, он дополнительно содержит блок выбора режима работы, причем первый, второй, третий, четвертый входы блока выбора режима работы подключены к соответст- в тащим входам кода режима процессора, первьп, второй, третий, четвертый, пятьй., шестой, седьмой и восьмой выходы блока выбора режима работы соединены соот аетственно с первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами кода операции всех вычислительных модулей, й (J 1,2,3,4) вычисли- те пьного модуля строки первого столбца матрицы подключен к i-му информационному входу вьиислительного модуля j-й строки второго столбца матрицы (i 1,2,3,4), причем каждый вычислительный модуль содержит матрицу размером 2x2 операдаонных элементов, при этом информационные входы операционньк элементов первой строки первого столбца матрицы подключены соответственно к первому и второму информационным входам модуля, информационные входы операгщонных элементов второй строки первого столбца матриць подключены к третьему и четвертому информационным входам модуля , первые информационные выходы операционных элементов первого столбца первой и второй стргж матрицы подключены соответственно к первому и второму информационным входам операционного элемента первой CTPOKVJ первого столбца матрицы, а вторые ин- форма днонные выходы операционных элементов первого столбца перкой и второй строк матрицы лодключень соответственно к первому и BTopof y инфор- мационньв- входам операционных эле- менто второго столбца второй строки матрицы, выходы операционных элементов пе.рвой строки второго столбца матрицы подключены к первому и второму информащюнньм выходам модуля, а выходы операционного элемента второй строки второго столбца матрицы к третьему и четвертому информационным

выходам модуля, причем первый и второй входы кода операции модуля под-- соответственно к первому и второму входам кода операции опера- ционных элементов первого столбца матрицы, третий и четвертый входы кода операции модуля подключепы к третьим входам кода операции операционных элементов первого столбца соответственно первой и второй строки матрицы, пятый и шестой входы кода операции модуля подключены соответственно к первым и вторым входам кода операции операционных элемен- тов второго столбца матрицы, седьмой и восьмой входы кода операции модуля подключены к третьим входам кода операции операционньтх элементов второго столбца соответственно первой и второй строк матрицы.

2. Процессор по п.1, о т л и - чающийс я тем, что операционный элемент содержит первый и второй сумматоры, первый и второй регистры входных данных, первьш и второй регистры выходных данных, четьфе буферных регистра, первый и второй коммутаторы, причем первый и второй информационные входы операционного эле- мента подключены к входам первого и второго регистров входных данных, выходы которых подключены к информационным входам первого и второго коммутаторов соответственно, первые вы- ходы которых подключены соответственно к входам первого и второго регистров вькодных данных, вторые выходы первого и второго коммутаторов соединены соответственно с информационными

входами первого и второго буферных регистров, третьи выходы первого и второго коммутаторов соединены соответственно с входами третьего к четвертого буферных регистров, выход первого и инверсньй выход второго буферных регистров подключены к первым входам соответственно первого и второго сумматоровJ вторые входы

которых подключены соответственно к выходам четвертого и третьего буферных регистров, выходы первого и второго сумматоров подключены к.входам

, 10 15 20

25 зо ..,

U

.,

0

первого и EiToporo регистров выходных данных, выходы которых подключены к первому и второму информационным выхо;1ам операционного элемента, первый;, BTOpot J и третий входы кода one- рации которого подключены соответственно к первым, вторым, третьим управляющим входам коммутаторов, причем третий вход кода операции операционного элемента подключен также к входу чтения/записи второго буферного регистра, а четвертый - к второму информационному входу младшего разряда второго сумматора.

3. Процессор по п.1, о т л и - чающийся тем,, что блок выбора режима работы содержит четыре элемента И-НЕ, два элемента ИЛИ-НЕ и два элемента НЕ, причем первый вход первого элемента ИЛИ-НЕ соединен с инверсным входом первого элемента И-НЕ и прямым входом второго элемента И-НЕ и является первым входом блока, второй вход первого элемента ИЛИ-НЕ соединен с прямым входом первого элемента И-НЕ и инверсным входом второго элемента И-НЕ и является вторым входом блока, выход первого элемента ИЛИ-НЕ соединен с входом первого элемента НЕ и является первым выходом блока, выход первого элемента НЕ является вторым выходом блока, выходы первого и второго эле- менгов И-НЕ являются соответственно третьим и четвертым выходами блока, первый вход второго элемента ИЛИ-НЕ соединен с инверсным входом третьего элемента И-НЕ и прямым входом четвертого элемента И-НЕ и является третьим входом блока, второй вход второго элемента ИЛИ-НЕ соединен с прямым входом третьего элемента И-НЕ и инверсным входом четвертого элемента И-НЕ и является четвертым входом блока, выход второго элемента ИЛИ-НЕ соединен с входом второго элемента НЕ и является пятым выходом блока, выход второго элемента НЕ является шестым выходом блока, выходы третьего и четвертого элементов И-НЕ являются соответственно седьмым и восьмым выходами блока.

p S 3 f feEZEpEjM

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для операций над матрицами | 1990 |

|

SU1735868A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С КОРРЕКЦИЕЙ ОШИБКИ | 1992 |

|

RU2018950C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1996 |

|

RU2125290C1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

Изобретение относится к области вычислительной техники и может быть использовано .в устройствах шифрования, кодирования, декодирования и распознавания сигналов, а также в устройствах обобщенного спектрального анализа и фильтрации, основанных на алгоритмах быстрых дискретных преобразований. Цель изобретения - повышение производительности устройства. Цель изобретения достигается за счет введения в процессор блока выбора режима работы,имеющего сложную структуру, с соответствующими связями между ним и известными блоками процессора. Применение в изобретении параллельно-последовательной конвейерной структуры вычислений по методу быстрых дискретных преобразований позво- Q ляет достичь положительного эффекта. ® 2 з.п. ф-лы, 15 нл. (D

«о иутацнр I °03 I уровня KoMHi rrKmuf 2 03 I уровня fSun с К23 ISuin с KZ4tSum с К23 iSum с Ягч

15ит с Я 24 ISum с К 23 ISum с К2 ( Wum с К23

Коммутация 1 2 уровня KoMnymai ua 2. ОЭ J уроВня Фиг.

Фиг.З

сз :j

Й

C3

iO

о to s 8«1

геэ

т тГТ

в 3

.7 О

Фмг-.д

I T

. в .h

I I

r T Фиг.П tr r

I I

r r

пппппппппппопппопппппппппп

бад

527,30 528,23

657,32 533,34.

Б23,2Ч 627,30

528,29 Б31д2

Тк

Т(

П) П) r.t

п (п ti t

Fh П

26

Плппппп

п п rf n п nn,t

П) П) r.t

Fh П

In,

ът,у

п Т1 п r,.t

п л Г1 л .t

Ы-

f-Тк

п Т1 п r,.t

Фиг. 13

шщ

Ф/7Я5

Y{/podi

ФППЭ V

ФигМ

г уровень прои,ессора

уровень процессора

уровень процессора

ZijpoSeHb процессора

8

1 уровень

Z уровень щтцессора

. 15

Составитель В. Смирнов Редактор С. Саенко Техред О.Сопка Корректор Л. Пилипенко.

Заказ 2772/51 Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,,, д. 4/5

Производственно-полиграфическое предприятие г, Ужгород, ул. Проектная, 4

| Матричный параллельный процессор для вычисления преобразования адамара | 1973 |

|

SU478306A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ ПРОИЗВОДСТВА КОНСЕРВОВ "ПОЧКИ ТУШЕНЫЕ С ФАСОЛЬЮ И ГРИБАМИ" | 2012 |

|

RU2484672C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1986-05-23—Публикация

1984-07-25—Подача