Изобретение относится к автоматике и вычислительной технике и может быть использовано при отладке логических блоков, микропроцессорных систем, ЭВМ и т.д.

Известен логический пробник (см.а.с. N 970281, кл. G 01 R 31/28 публик. в N 40 "ОИПОТЗ", 1982), содержащий первый и второй пороговые блоки, коммутатор, счетчик, первый, второй и третий триггеры, элемент И, первый, второй, третий и четвертый индикаторы.

Однако известный логический пробник имеет ограниченные функциональные возможности, обусловленные фиксацией результата контроля только для одного такта работы контролируемого устройства, что не позволяет использовать его для контроля работы устройств под управлением сложных программ.

Известен также логический пробник, содержащий пороговый блок, четыре индикатора, три элемента НЕ, IK-триггер, RS-триггер, два элемента И, элемент ИЛИ, счетчик, дешифратор, делитель частоты, переключатель, кнопку и регистр сдвига.

Однако известный логический пробник не позволяет накапливать результаты контроля выборочно для определенных состояний контролируемого устройства.

Из известных технических решений наиболее близким по технической сущности к предлагаемому устройству является логический пробник, содержащий контрольный щуп, ограничительный резистор, блок согласования, двухкаскадный эмиттерный повторитель, блок обнаружения импульсов, одновибратор, индикатор, формирователь фронтов тактовых импульсов, блок останова. Блок согласования содержит два транзистора, три диода, резистор. Блок обнаружения импульсов содержит пять элементов НЕ, два элемента ИЛИ-НЕ. Формирователь фронтов тактовых импульсов содержит переключатель, два резистора, элемент НЕ, два элемента И-НЕ, элемент И, управляющий триггер, элемент задержки, счетчик, задатчик кода номера такта, первый и второй информационные триггеры (регистр). Блок останова содержит элемент сравнения и задатчик кода признака команды (наборное поле).

Недостатком прототипа является то, что он не фиксирует результаты контроля, сохраняя их только до поступления следующей выбранной команды, которая обновляет состояние индикации, что затрудняет контроль при высокой частоте следования выбранных команд. Кроме того известный логический пробник не позволяет накапливать результаты контроля, что затрудняет его использование для наблюдения за работой контролируемого устройства под управлением сложных программ.

Техническим результатом предлагаемого изобретения является расширение функциональных возможностей логического пробника путем накопления результатов контроля в оперативном запоминающем устройстве для определенных состояний контролируемого устройства и последующим выводом результатов контроля на индикатор.

Технический результат достигается тем, что в логический пробник, содержащий блок согласования, блок останова, регистр, счетчик, управляющий триггер, первый элемент 2И, элемент НЕ, элемент задержки, первый индикатор, входы которого соединены с выходами регистра, входы блока согласования являются первой группой информационных входов логического пробника, информационные входы блока останова являются второй группой информационных входов логического пробника, дополнительно введены блок памяти, мультиплексор, второй индикатор, второй и третий элементы 2И, первый и второй элементы 2ИЛИ, элемент 5И со следующими связями: выход элемента 5И соединен со входом записи блока памяти, счетным входом счетчика, входом установки управляющего триггера и первым входом второго элемента 2И, выход которого соединен с первым входом первого элемента 2ИЛИ, выход которого соединен со входом записи регистра, информационные входы которого соединены с выходами мультиплексора, первая группа информационных входов которого соединена с информационными входами блока памяти и выходами блока согласования, вторая группа информационных входов мультиплексора соединена с выходами блока памяти, адресные входы которой соединены с информационными выходами счетчика и входами второго индикатора, вход чтения блока памяти соединен с вычитающим входом счетчика, входом элемента задержки и выходом третьего элемента 2И, первый вход которого соединен со входом сброса управляющего триггера, с первым входом первого элемента 2И и является входом готовности логического пробника, выход первого элемента 2И соединен со входом сброса счетчика, выход переполнения которого соединен с первым входом элемента 5И, второй вход которого соединен с выходом блока останова, управляющий вход которого соединен со входом синхронизации адреса логического пробника, третий вход элемента 5И соединен с выходом второго элемента 2ИЛИ, первый и второй входы которого соединены соответственно с первым и вторым управляющими входами логического пробника, четвертый вход элемента 5И соединен со входом режима индикации логического пробника, вторым входом первого элемента 2И, управляющим входом мультиплексора и входом элемента НЕ, выход которого соединен со вторым входом третьего элемента 2И, выход элемента задержки соединен со вторым входом первого элемента 2ИЛИ, пятый вход элемента 5И соединен с третьим управляющим входом логического пробника, выход управляющего триггера соединен со вторым входом второго элемента 2И.

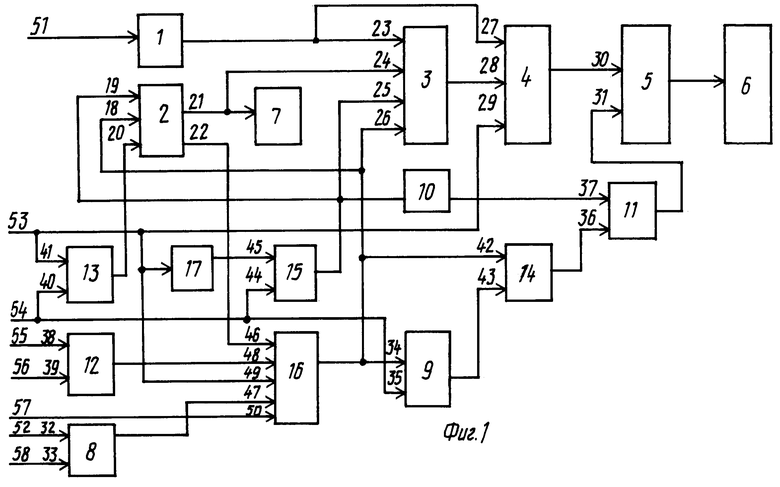

Блок останова содержит элемент сравнения, наборное поле, D-триггер, причем информационный вход блока останова соединен с первым входом элемента сравнения, второй вход которого соединен с наборным полем, выход элемента сравнения соединен с информационным входом D-триггера, вход синхронизации которого соединен с управляющим входом блока останова, выход D-триггера соединен с выходом блока останова.

Наличие отличительных признаков обуславливает соответствие заявляемого технического решения критерию "новизна".

Поскольку у предлагаемого устройства появляются свойства, не совпадающие со свойствами известного решения, можно сделать вывод о том, что предлагаемое техническое решение соответствует критерию "существенные отличия".

Возможность достижения технического результата предлагаемого изобретения обусловлена введением новых блоков и связей, что расширяет функциональные возможности логического пробника путем фиксаций данных, передаваемых по системной шине микропроцессорной системы в циклах записи и чтения памяти или внешнего устройства по определенному адресу, заданному на наборном поле блока останова, и индикации их на первом индикаторе, накоплением результатов контроля в ОЗУ с одновременным подсчетом и индикацией числа обращений по заданному адресу на втором индикаторе и последующим последовательным выводом результатов контроля, записанных в ОЗУ, на первый индикатор. Это позволяет контролировать взаимодействие микропроцессора и внешних устройств или микропроцессоров в многопроцессорной системе в динамическом режиме, исключая использование для контроля пошагового режима работы или останова по выбранному адресу искажающих динамику контролируемых процессов.

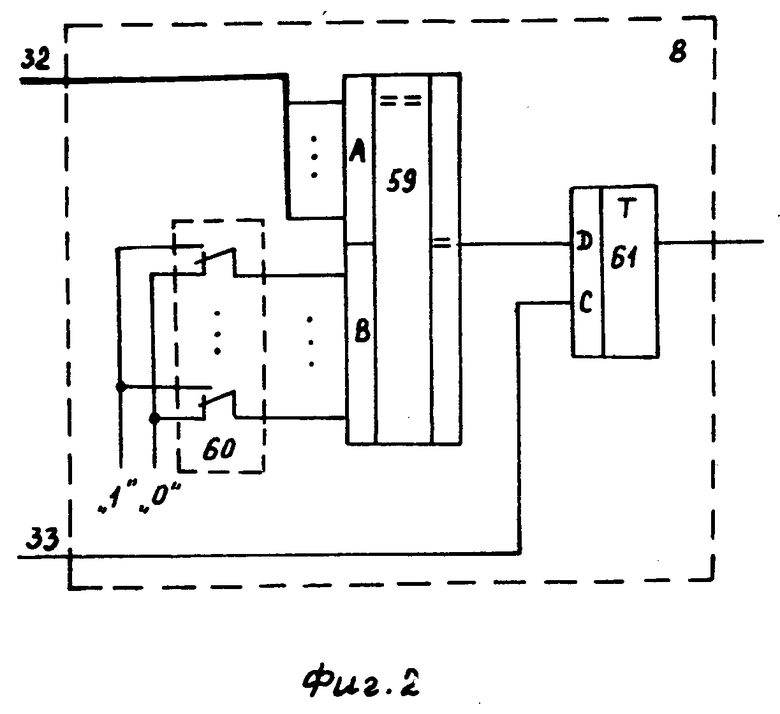

На фиг. 1 изображена структурная схема логического пробника; на фиг.2 функциональная схема блока останова.

Логический пробник фиг.1 содержит блок согласования 1, счетчик 2, блок памяти 3, мультиплексор 4, регистр 5, первый индикатор 6, второй индикатор 7, блок останова 8, управляющий триггер 9, элемент задержки 10, первый элемент 2ИЛИ 11, второй элемент 2ИЛИ 12, первый элемент 2И 13, второй элемент 2И 14, третий элемент 2И 15, элемент 5И 16, элемент НЕ 17, счетный 18, вычитающий 19 и сброса 20 входы счетчика 2, информационные 21 и переполнения 22 выходы счетчика 2, информационные 23 и адресные 24 входы блока памяти 3, вход чтения 25 и вход записи 26 блока памяти 3, первая группа информационных входов 27, вторая группа информационных входов 28 и управляющий вход 29 мультиплексора 4, информационные 30 и записи 31 входы регистра 5, информационные 32 и управляющий 33 входы блока останова 8, вход установки 34 и вход сброса 35 управляющего триггера 9, первый 36 и второй 37 входы первого элемента 2ИЛИ, первый 38 и второй 39 входы второго элемента 2ИЛИ 12, первый 40 и второй 41 входы первого элемента 2И 13, первый 42 и второй 43 входы второго элемента 2И 14, первый 44 и второй 45 входы третьего элемента 2И 15, первый 46, второй 47, третий 48, четвертый 49, пятый 50 входы элемента 5И 16, первая 51 и вторая 52 группы информационных входов логического пробника, вход режима индикации 53 логического пробника, вход готовности 54 логического пробника, первый 55, второй 56 и третий 57 управляющие входы логического пробника, вход синхронизации адреса 58 логического пробника.

Блок останова 8 (фиг.2) содержит элемент сравнения 59, наборное поле 60, D-триггер 61.

Вход 53 логического пробника соединен со входом блока согласования 1, выход котоpого соединен с входом 23 блока памяти 3 и входом 27 мультиплексора 4, выход мультиплексора 4 соединен со входом 30 регистра 5, выход которого соединен со входом первого индикатора 6, вход 53 логического пробника соединен со входом 41 первого элемента 2И 13, входом элемента НЕ 17, входом 49 элемента 5И 16 и входом 29 мультиплексора 4, вход 54 логического пробника соединен со входом 40 первого элемента 2И 13, входом 44 третьего элемента 2И 15, входом 35 управляющего триггера 9, выход элемента 5И соединен со входом 34 управляющего триггера 9, входом 42 второго элемента 2И 14, входом 26 блока памяти 3 и входом 18 счетчика 2, выход 21 счетчика 2 соединен со входом второго индикатора 7 и входом 24 блока памяти 3, выход которого соединен со входом 28 мультиплексора 4, вход 55 логического пробника соединен со входом 38 второго элемента 2ИЛИ 12, вход 56 логического пробника соединен со входом 39 второго элемента 2ИЛИ 12, выход которого соединен со входом 48 элемента 5И 16, вход 57 логического пробника соединен со входом 50 элемента 5И 16, вход 52 логического пробника соединен со входом 32 блока останова 8, вход 58 логического пробника соединен со входом 33 блока останова 8, выход блока останова 8 соединен со входом 47 элемента 5И 16, выход элемента НЕ 17 соединен со входом 45 третьего элемента 2И 15, выход которого соединен со входом элемента задержки 10, входом 25 блока памяти 3 и входом 19 счетчика 2, выход 22 которого соединен со входом 46 элемента 5И 16, выход управляющего триггера 9 соединен со входом 43 второго элемента 2И 14, выход которого соединен со входом 36 первого элемента 2ИЛИ 11, выход которого соединен со входом 31 регистра 5, выход первого элемента 2И 13 соединен со входом 20 счетчика 2, выход элемента задержки соединен со входом 37 первого элемента 2ИЛИ 11, вход 32 блока останова 8 соединен с первыми входами А элемента сравнения 59, наборное поле 60 соединено со вторыми входами В элемента сравнения 59, выход которого соединен с информационным входом D-триггера 61, вход 33 блока останова 8 соединен со входом синхронизации С триггера 61, выход которого соединен с выходом блока останова 8.

Устройство работает следующим образом. Первая 51 группа информационных входов логического пробника подключается к шине данных микропроцессорной (МП) системы. Вторая 52 группа информационных входов логического пробника подключается к адресной шине микропроцессорной системы при разделенных шинах адреса и данных или параллельно первой группе 51 информационных входов логического пробника в случае совмещенной шины адреса и данных, при этом на вход 58 синхронизации логического пробника поступает соответствующий сигнал с системной шины МП системы. На первый 55 и второй 56 управляющие входы логического пробника поступают соответственно сигналы записи и считывания с системной шины МП системы или один из них в зависимости от вида контроля. На третий управляющий вход 57 логического пробника поступает сигналы готовности от внешних устройств. При работе с быстрыми внешними устройствами на этом входе должен быть установлен уровень "логическая 1".

При контроле входных данных на входе 53 режима индикации логического пробника необходимо установить уровень "логическая 1". При этом уровень "логическая 1" на входе 49 элемента 5И 16 разрешает прохождение сигналов через элемент 5И 16, уровень "логическая 1" на входе 41 первого элемента 2И 13 разрешает прохождение сигнала с входа 54 готовности логического пробника через первый элемент 2И 13 на вход 20 сброса счетчика 2, уровень "логическая 1" на входе 29 мультиплексора 4 подключает выходы блока согласования 1 к информационным входам 30 регистра 5, уровень "логический 0" на входе 45 третьего элемента 2И 15 запрещает прохождение сигналов готовности со входа 54 логического пробника через третий элемент 2И 15. По импульсу готовности, сформированному по инициативе оператора и поступившему на вход 54 логического пробника, устанавливается в нулевое состояние счетчик 2 и сбрасывается управляющий триггер 9. Сигнал с инверсного выхода управляющего триггера 9 разрешает прохождение сигналов со входа 42 второго элемента 2И 14 на вход 36 первого элемента 2ИЛИ 11. Сигнал с инверсного выхода переполнения 22 счетчика 2 разрешает прохождение сигналов через элемент 5И 16. При совпадении адреса, поступившего на вход 52 пробника, с установленным на наборном поле 60 на выходе блока останова 8 устанавливается уровень "логическая 1", разрешающий прохождение сигналов через элемент 5И 16. В момент появления сигналов записи или считывания, поступающих на первый 55 или второй 56 управляющие входы логического пробника, и поступлении сигнала готовности от внешнего устройства на третий управляющий вход 57 логического пробника на выходе элемента 5И 16 появляется сигнал, который, поступая на вход записи 26 блока памяти 3 и через элементы 2И 14 и 2ИЛИ 11 на вход 31 записи регистра 5, разрешает запись информации, поступающей на входы 51 логического пробника, в блок памяти 3 и регистр 5. По окончании сигнала на выходе элемента 5И 16 увеличивается состояние счетчика 2 и взводится триггер 9, запрещая дальнейшее прохождение сигналов записи через элемент 2И 14 на вход 31 записи регистра 5. При последующих обращениях по установленному на наборном поле 60 адресу работа логического пробника аналогична описанной выше, исключая запись в регистр 5. В случае переполнения счетчика 2 инверсный сигнал переполнения с его выхода 22 запрещает прохождение сигналов через элемент 5И 16, запрещая тем самым перезапись данных, записанных в блоке памяти 3. По окончании процесса контроля индикатор 6 индицирует данные, зафиксированные при первом обращении по установленному адресу, индикатор 7 количество обращений, блок памяти 3 хранит результаты всех обращений. Для считывания данных, накопленных в блоке памяти 3, необходимо на вход 53 режима индикации логического пробника подать уровень "логический 0". При этом запрещается прохождение импульсов готовности со входа 54 логического пробника через элемент 2И 13 на вход 20 сброса счетчика 2, запрещается прохождение сигналов через элемент 5И 16, разрешается прохождение импульсов готовности со входа 54 логического пробника через элемент 2И 15 на вход чтения 25 блока памяти 3, вычитающий вход 19 счетчика 2 и через элемент задержки 10 и элемент 2ИЛИ 11 на вход записи регистра 5. Мультиплексор 4 подключает выходы памяти к информационным входам 30 регистра 5. По каждому импульсу готовности, формируемому по инициативе оператора и поступающему на вход 54 логического пробника, считывается информация из блока памяти 3, записывается в регистр 5 и уменьшается на единицу содержимое счетчика 2. При этом на индикаторе 6 индицируются считанные из блока памяти 3 данные, а на индикаторе 7 количество оставшихся в блоке ОЗУ 3 данных. Таким образом осуществляется последовательный обратный просмотр результатов контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| РАСШИРИТЕЛЬ ИНТЕРФЕЙСА "КАНАЛ ОБЩЕГО ПОЛЬЗОВАНИЯ" | 2009 |

|

RU2402805C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

Использование: логический пробник относится к автоматике и вычислительной технике и может быть использовано при отладке логических блоков, микропроцессорных систем, ЭВМ и т.д. Устройство содержит блок согласования 1, счетчик 2, блок памяти 3, мультиплексор 4, реестр 5, индикаторы 6,7, блок останова 8, тригер 9, элемент задержки 10, элементы 2 ИЛИ 11,12, элементы 2И, 13, 14, 15, элемент 5И 16, элемент НЕ 17. 1 з.п. ф-лы, 2 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логический пробник | 1983 |

|

SU1132268A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-08-09—Публикация

1991-12-26—Подача