выход второго регистра адреса через В орую it третью памяти соединен соответственно входами блока сравнения и элементов ИЛИ группы, выходы регистров группы соединены с входами соответствующих умножителей группы, выходы регистра сдвига соединены с входами соотпетствующих UIOKOD элемс1- тов И группы и элементов И группы, выходы которых через соответствующие счетчики группы соединены с входами соответствующих коммутаторов второй группы, выходы которых соединены с группой входов первого регистра адреса, выходы второго и регистров соединены соответственно с входами первого и второго вычитателей, выход элемента НЕ через соединенные последовательно первый коммутатор и четвертый регистр - с входами третьего вычитателя и четвертого коммутатора, выходы пятого регистра и третьего йычитателя соединены с входами схемы сравнения, первый выход которой соединен с входами второго элемента задержки, четвертого элемента ИЛИ, элементов И группы, и через четвертый коммутатор с входами первого и шестого регистров, второй выход схемы сравнения через соединенные последовательно четвертый элемент ИШ и третий коммутатор соединен с входом блока сравнения, выход второго элемента задержки соединен с входами второго коммутатора и коммутаторов группы, выход шестого регистра соединен с входом третьего вычитателя, выходы первого элемента ИЛИ и перв(5го элемента задерлски соединены с входами регистра сдвиг-а.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Устройство для контроля дискретного объекта | 1984 |

|

SU1218398A1 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В ПОЛНОСВЯЗНЫХ МАТРИЧНЫХ СИСТЕМАХ ПРИ ОДНОНАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2010 |

|

RU2470357C2 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Арифметическое устройство | 1984 |

|

SU1229754A1 |

СИСТЕМА СБОРА И ОБРАБОТКИ ИHФOP Ь ДИИ, содержащая генератор, выход которого через первый и второй элементы И соединены с входами первого элемента ИЛИ, регистр сдвига, выходы которогосоединены с входами второго элемента ИЛИ и третьего элемента И, выход которого соединен с входом первого элемента задержки, входы устройства соединены с входами коммутаторов первой группь, первый регистр адреса, выход которого соединен с входом первой памяти, четвертый элемент И, выход которого соединен с входом третьего элемента ИЛИ, счетчик, отличающаяся тем, что, с целью повышения коэффициента использования оборудования, достоверности и оперативности контроля, в нее введены две памяти, блок сравнения, регистр адреса, блок регистрации, два триг-1-ера, схема сравнения, три вычитателя, nieci ь регистров, четыре коммутатора, элем(чгг задержки, группа э.ементов запрета, группа элементов , группа счетчиков, группа коммутаторов, группа элементов И, группа блоков элеменгов И, блок элементов ИЛИ, rpyitia регистров, группа умножителей, таймер, элемент ИЛИ, элемент И, элемент НЕ, причем выходы коммутаторов первой группы через соответствующие элементы за,прета группы соединены с входами соответствующих элементов ИЖ группы, выходы которых через соответствующие умножители группы соединены с входами соответствующих блоков элементов И группы, выходы которых через блок элементов ИЛИ соединены с входами первых коммутатора и вычитателя, выход которого через второй вычитатель соединен с входами элемента НЕ и пятого элемента И, выход которого через третий элемент ИЛИ соединен с входом блока регистрации, другие входы которого (П соединены соответственно с первьм управляющим входом системы,и выходами первой памяти и блока сравнения, второй управляющий вход системы соединен с входом четвертого элемента И, третий управляющий вход системы сое.динен с первым входом первого регистра адреса, второй вход которого и вход второго регистра адреса через счетчик соединены с выходами второго элемента ИЛИ и третьего элемента И, четвертый управляющий вход системы соединен с входами первого и второго триггеров, выход таймера соединен с входами четвертого и пятого элементов И, выход первого триггера соединен с входом первого элемента И, третьим входом первого регистра сдвига и через соединенные последовательно первый регистр и второй коммутатор с входом первой памяти, выход второго триггера соединен с входами элементов запрета группы, второго элемента И и третьего коммутатора.

Изобретение отг осится к области вычислительной техники и может быть использовано для связи блока обработки информации (ЭВМ) с периферийным оборудованием наблюдением состояния выбранных 1рупп датчиков, в частности- с оборудованием контроля состояния тепловых сетей.

Известно устройство для ввода информации, содержащее регистр сдвига, группу регистров, два элемента ШЖ, два регистра, два элемента И, два элемента задержки ull.

Недостатком данного устройства является отсутствие возможности работы с группой различ}1ых датчиков, используемых при контроле состояния тепловых сетей, формирования и предварительной обработки указанной информации.

Система сбора и обработки информации, содержа цая генератор, выход которого через первый и второй элементы И соединены с входами первого элемента ИЛИ, регистр сдвига, выходы которого -соединены с входами второго элемента ИЛИ и третьего элемента И, выход которого соединен с входом первого элеме1гга задержки, входы устройства соединь-ны с входами коммутаторо перпой труппы, первый регистр адреса, выход которого соединен с входом первой памяти, четвертый элемент И, выход которого соединен с входом третьего элемента ИЛР1, счет-1ик позволяет проводить избирательный опрос датчиков 121.

Одьако система ие учитывает специфику информап.ии от отдельных дат iHKOB (oтдeJJЬJ ыx групп датчиков),

не производит разделение существенной информации, что значительно влияет на объем требуемой памяти или достоверность собранной информации, не позволяет обеспечить постоянно.е наблюдение за состоянием выбранных групп датчиков. Кроме того, известная система не может обеспечить контроль оператора за сс)стоянием всей совокупности датчиков и оперативный вывод данрН)1х на индикацию и печать,, зафиксировать аварийную ситуацию и обеспечить наделчность за счет самоконтроля системы.

Цель изобретения - новьпление коэ(}зфициента использования оборудова1-н5я, достоверности и оперативности контроля.

Г1оставле1И1ая це;И) достигается тем,

что в систему сбора и обработки и1-1формации, содержащую генератор.

выход которого через первый и второй элементы И соединены с входами первого элемента ИЛИ, регистр сдвига, выходы которого соединены с входами второго элемента ИЛИ и третьего элемента И, выход которого соединен с входом первого элемента задержки, входы устройства соединены с входами коммутаторогз первой группы, первый регистр адреса, выход которого соединен с входом первой памяти, четверты элемент И, выход которого соединен с входом третьего элемента ИЛИ, счетчик, введены две памяти, блок сравнения, регистр адреса, блок регистрации, два триггера, схема сравнения три вычитателя, шесть регистров, четыре коммутатора, элемент задержки, группа элементов запрета, группа элементов ИЛ11, группа счетчиков, группа коммутаторов, группа элементов И, группа блоков элементов И, блок элементов ИЛИ, группа регистров, группа умножителей, таймер, элемент ИЛИ, элемент И, элемент ЛЕ, причем выходы коммутаторов первой группы через соответствующие элементы запрета групы соединены с входами соответствующих элементов ИЛИ группы, выходы которых через соответствующие умножители группы соединены с входами соответствующих блоков элементов И группы, выходы которых через бло1с элементов ИЛИ соединены с входами певых коммутаторов и вычитателя, выход которого через второй вычитатель соединен с входами элемента НЕ и пятого элемента И, выход которого через третий элемент ИЛИ соединен с входом блока регистрации, другие входы которого соединены соответственно с первым управляющим входом системы, и выходами первой памяти и блока сравнения, второй управляющий вход системы соединен с входом четвертого И, третий управляющий вход системы соединен с первым входом первого регистра адреса, второй вход которого и вход второго регистра адреса через счетчик соединены с выходами второго элемента ИЛИ и третьего элемента И, четвертый управляющий вход системы соединен с входами первого и второго триггеров, выход таймера соединен с входами четвертого и пятого элементов И, выход первого триггера соединен с входом первого элем4жта И, третьим входом первого регистра сдвига и через соединенные последовательно первый регистр и второй коммутатор с входом первой памяти, выход второго триггера соединен с входами элементов-запрета группы, второго элемента И и третьего коммутатора, вьгеод второго регистра адреса через вторую и третью памяти соединен соответственно с входами блока сравнения и элементов ИЛИ группы, выходы регистров группы соединены с входами соответствующих умножителей группы, выходы регистра сдвига соединены с входами соответствующих блоков элементов И группы и элементов И группы, выходы которых через соответствующие счетчики группы соединены с входами соответствующих коммутаторов второй груп- пы, выходы которых соединены с группой входов первого регистра адреса, выходы второго и третьего регистров соединены соответственно с входами первого и второго вычитателей, выход элемента НЕ через соединенные последовательно первый коммутатор и четвертый регистр - с входами третьего вычитателя и четвертого коммутатора, выходы пятого регистра и третьего вычитателя соединены с входами схемы

0 сравнения, первый выход, которого соединен с входами второго элемента задержки, четвертого элемента ИШ, элементов И группы, и через четвертый коммутатор с входами первого и шестого регистров, второй выход схе5мы сравнения через соединенные последовательно четвертый элемент ИЛИ и третий коммутатор соединен с входом блока сравнения, выход второго

0 элемента задержки соединен с входами второго коммутатора и коммутаторов группы, выход шестого регистра соединен с входом третьего вычитателя, выходы первого элемента ИЛИ и перво5го элемента задержки соединены с входами регистра сдвига.

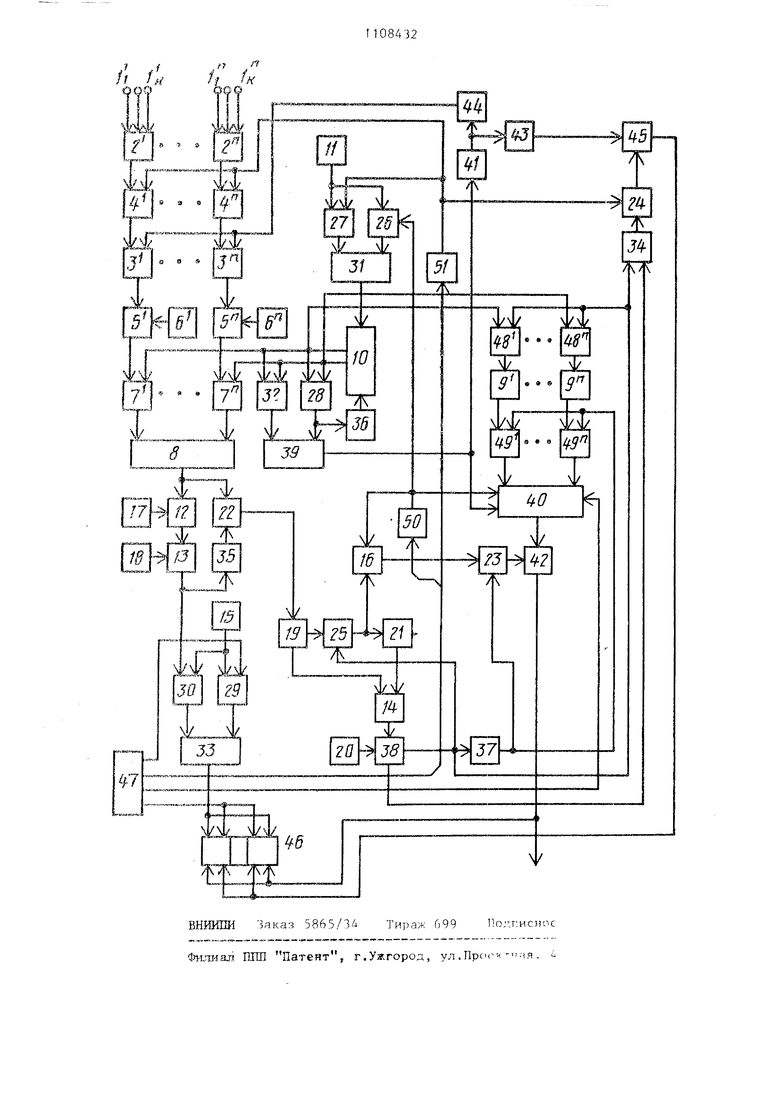

На чертеже приведена структурная схема предложенной системы.

указаны выходы датчиi

1 k , коммутаторы 2

. 2 , элементы ИЛИ 3 ... 3 группы, элементы запрета 4 . 4 группы, умножите- ли 5... 5 группы, регистры коэффициентов 6 ... 6 группы, блоки элементов И 7... 7 группы, блок элементов ИЛИ 8, счетчики 9 ...9 группы, регистр сдвига 10, генератор тактовых 1мпульсов 1 1 , вычитател 1 12--14, таймер 15, регистр 16 данных, регистр 17 порога, регистр 1 порога, регистр 19 текущего значения, регистр 20 допустимых отклонений, oyipepFibiH регистр 21, коммутаторы 22-25, элементы И 26-30, элемепть ИЛИ 31-34, элемент НЕ 35, элементы 36-37 задер7кки, схема 38 сравнения, счетчик 39 номера зоны, регистры 40,41 адреса, намять 42 данных, память 43 отклонений, память 44 эталонных сигналов, блок 45 сравнения, блок 46 регистрации, пульт 47 элементы И 48 управления, группы, ком.мутаторгл 49 ... 49 группы, триггер 50 управления, триггер 5 контроля (блок синхронизации, тактирующий работу отдел1 11Ь Х узлов, входы установки триггеров, peri-icTpoB, счет чиков и т.д. не показаны). Система работает следующим образ fo сиг ;а;гу onepaTojia с 47 выбирается режим работь системы. Пре полагаетс;я два режима работы: рабочи и с ам ок о и т р ОЛЯ . В рабочем режиме TjiHrrep управления 50 устанавливается в единичное состояние, а т|1иггер коьгтроля 51 остается в исходном. Сигиалы от датчиKOF3 1 ... I r/ocTynaioT через комму таторы 2 ... 2, элементы запрета 4 ... 4 (открытые, поскольку сигнал с триггера 51 отсутствует) и элементы ИЛИ 3 ... 3 на ВХОД)) масштабиру мых умножрггелей 5 ... 5 . Весь масс датчиков разби на п вьщеле -И1Ь х групп. В каждой групгге объединены датчики ОДН01Ч) (11ун1с ;иоиальногю назн , чения (тб мперат а Ь, дав.неиия и т.д. Для ) Г1)уг( .1и::ается свой масштабн1)й коэффициент, записа ный в регистрах 6 ... 6 После мас,- П штабирова И1я в y нгoжитeляx j ... з сигналы ляются си налаг-- И от ретистра 10. В регистре сдвига едшинда упра)эления сдвигается импульсами от генератора 1 1 , П(,)д, через элемент ИЛИ 31. Таким образом, ироизводится подключение сигналов ;1атчико выбранной рунпы к блоку элементов И.ГО-f 8. С выхода блока 8 сигнал поступает в коммутатор 22 и вычитатель 12, 1Д1; сравнивается со значе1;лем регие/рл порпга 17. Полученная разница поступает в вычитатель 13, где сравнивается со значением регистра порога 18. В случае нревьЕцения поступившим сигналом значения комбинированного порога выдается сигнал аварийной сигнализации, и время поступления аварийной ситуации фиксируется таймером 15 через элемент И 30 и элеме гг ИЛИ 33 в блоке 46. В этом случае анализ поступившей информации но рабочему алгоритму не производится, так как коммутатор 22 закрыт сигналом от единичного плеса знакового разряда вычитателя 13 через элемент НЕ 35. Элемент НЕ 35 включен в схему для отражения логического взаимодействия узлов при обработке информации. В нринципе может быть использован сигнал е нулевого плеча знакового разряда вычитателя 13. По сигналу аварийной ситуации оператор выдает сигнал сброса триггера 50 и производится ряд мероприятий по локализации и устранению аварий . IlcjiH значение поступите го сигнала не превьпиает значения установленного порога, то производится дальнейший анализ поступившей информации. При этом информация через комму1атор 22 но разрешающему сигналу от элемента НЕ 35 подается в регистр 19 и далее в вычитатель 14, где производится ее сравнение с содержимлм регистра 21. Результат, полученньй от вычитателя 14, поступает в схему сравнения 38, которая определяет суiiiecTBeiiHOcTb поступившей информации. Это осуществляется следующим образом. Если разность, нолуче1 ная ё вьпштателе 14, нревьпиает значение допустимого отклонения, занисашюго в регистре 20, то данная информация считается существенной и из регистра 19 через коммутатор 25 переписывается регистр 21. Вновь ноступающая инфорация сравнивается уже с этим новым начением. Таким образом, проводится ыборка и фиксация только существеной Ршформации, которая записывается регистр данных - 16 памяти 42. Адрес ячейки , куда следует зап11сывать информацию, формируется следующим образом. Сигналы от регистра сдвига 1 (J через элемент ИЛИ 32 поступают в счетчик 39, где формируется номер , отведенной .(ля каж/кио каназга (вь еленной группы датчиков). Иомео ячелгки р зои(. формируется с помощью счетчиков 9 ... 9, куда поступает единичная информация каждый раз при поступлении существенной выборки по данному каналу. Это осуществляется при поступлении сигналоп на один элемент И . . . 48 от соответствующего выхода регистра сдвига 10 и схемы сравнения 38.

Код от выбранного счетчика 9... 9 поступает в регистр адреса 40 через коммутаторы 49 . . . 49 одновременно с поступлением содержимого регистра 16 на информационный вход памяти 42 через коммутатор 23, но после некоторой задержки, осуществляемо элементом задержки 37. Это необходимо для того, чтобы устранить влияние переходных процессов и исключить запись неверной или старой информации.

После прохождения сигнала по всему регистру сдвига 10, т.е. после формирования номеров всех зон счетчиком 39, срабатывает элемент И 28 и устанавлицает счетчик 39 в нулевое состояние. После некоторой паузы, формируемой элементом задержки 36, достаточной для срабатывания всех предусмотрер1Н1)1х в данном uiare операции средств, в единичном разряде регистра 10 вновь устанавливается единица и цикл работы повторяется. Для считывания информации из любой выбранной ячейки памяти 42 оператор может набрать код адреса этой ячейки и выдать ее содержимое на выход системы, на блок 46.

Периодически или но специальному сигналу оператора на блоке через элементы И 29 и ИЛИ 3 может фиксироваться выбранная информация и время.

При работе во втором режиме включается трнггер 51, а триггсф 50 сбрасывается. Кди}п-1чное состояние триггера 51 разрешает работу регистра адреса 41, элемента И 27 и запрещает работу элементов запрета 4 ... 4 .

Импульсы с генератора 11 через элемент И 27 и элемент ИЛИ 31 поступают в регистр сдвига 10 и управляют сдвигом единицы в нем. Одновременно сигналы с выходом регистра 10 через элемент ИЛИ 32 поступают на вход счетчика 39, который черсз регистр 41 упраппяет пьщачей эталонных сигналов И- памяти na.nonniiix сигнанхолы iieMfHTOB ИЛИ 3 ...

л ОБ 44 на

С выхода вычитателя 14 значение отклонения поступает в коммутатор 24, на который поступают разрещающие сигналы от триггера 51 и через элемент ИЛИ 34 с выходов схемы сравнения 38. Элемент ИЛИ 34 введен для соблюдения общей логики работы системы. Таким образом, коммутатор 24 передает значение полученного отклонения на блок сравнения 45, куда также поступают значения заранее известных расчетных отклонений из памяти отклонения 43. Результаты сравнения поступают в блок 46 и контролируются оператором. При появлении существенного расхождения рассчитанного и полученного отклонений о;, может остановить (и повторить) работу системы, осуществить оперативный контроль работоспособности системы. При возникновении сбойных ситуаций оператор может повторить работу в режиме самоконтроля запланированное количество раз и в случае повторения ошибки несколько раз (устанавливается по согласованию) зафиксировать ошибку.

TaKPtM образом, изобретение позволяет обеспечить контроль оператора

5 за состоянием всей совокупности датчиков (контроль параметров теплоносителей и состояния технологического оборудования тепловых сетей) , оперативный вывод данных на индика0цию и печать, а также зафиксировать аварийную ситуацию и обеспечить надежность работы системы за счет организации самоконтроля системы. Кроме того, система производит выделение существенной информации, чт снижает

5 объем требуемой памяти без гмижения информативности и достоверности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для ввода информации от контактных датчиков | 1981 |

|

SU972498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сбора и предварительной обработки информации | 1981 |

|

SU1012230A1 |

Авторы

Даты

1984-08-15—Публикация

1983-10-17—Подача