Изобретение относится к вычислительной технике, в частности к системам навигации летательных аппаратов (ЛА), используемым для управления полетом ЛА на основе результатов совместной обработки информации инерциальной навигационной системы и сравнения карт местности.

Целью изобретения является повышение точности определения координат ЛА.

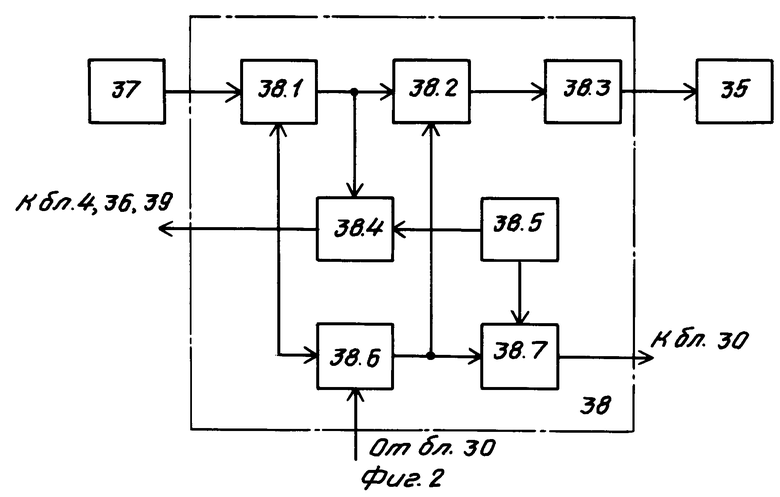

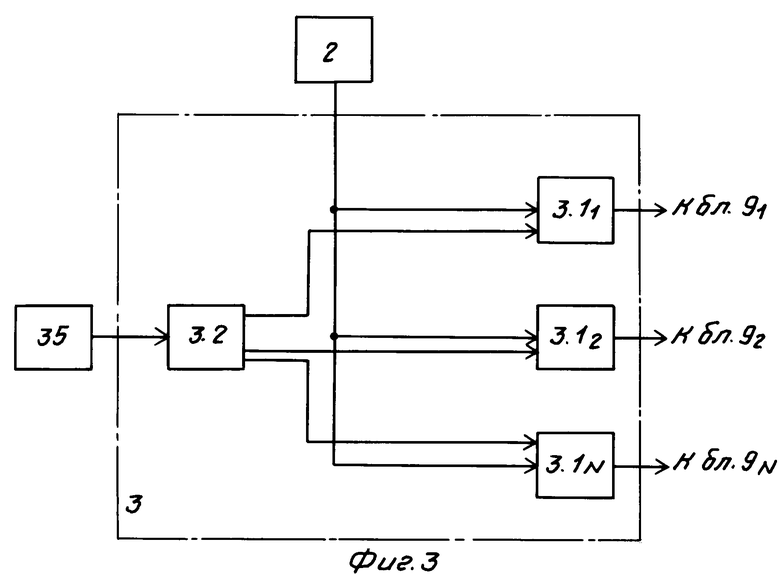

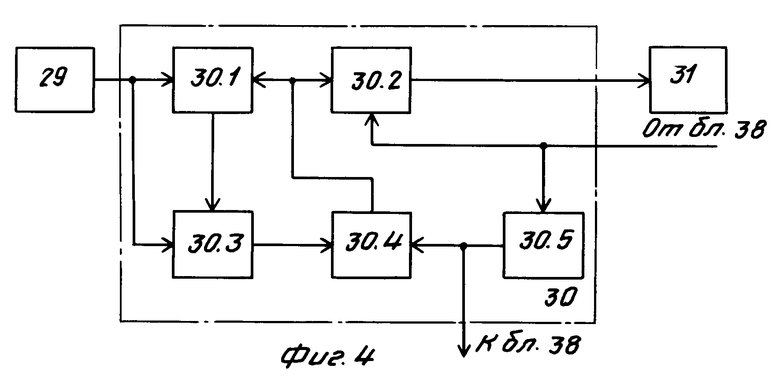

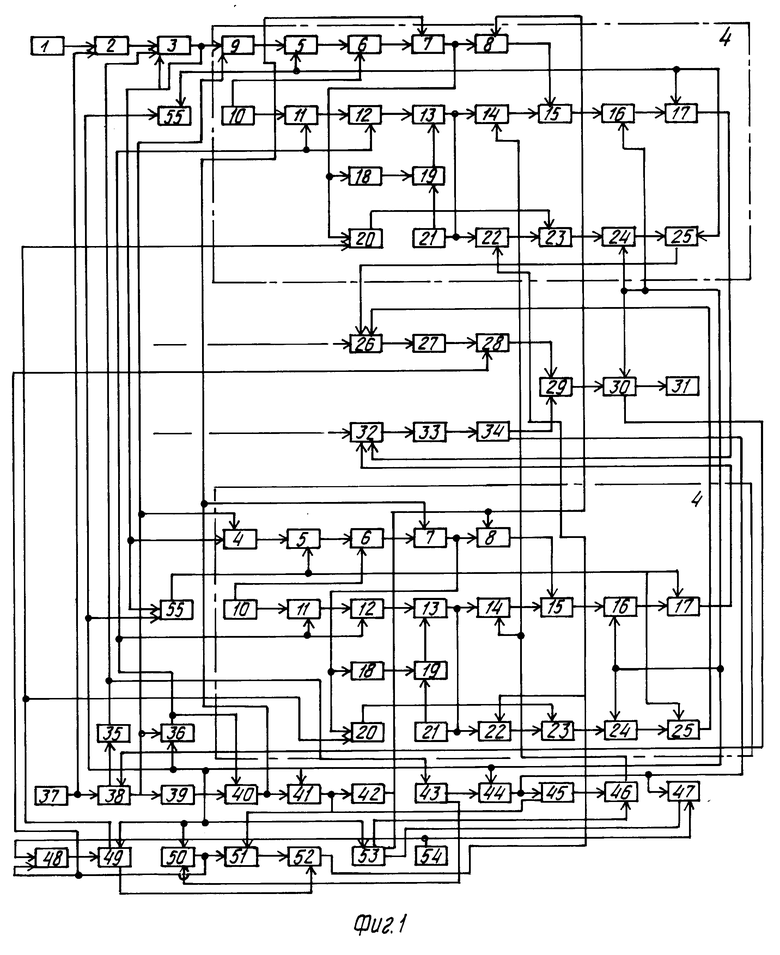

На фиг. 1 представлена блок-схема заявляемой системы; на фиг. 2 - формирователя адреса; на фиг. 3 - распределителя информации; на фиг. 4 - формирователя координат.

Система содержит радиолокационный блок 1, память 2 текущих данных, распределитель 3 информации, формирователи 4 оценки средней интенсивности сигналов группы, содержащие делитель 5, блок 6 элементов ИЛИ, регистр 7, коммутатор 8, сумматор 9, блок 10 элементов задержки, коммутаторы 11 и 12, умножитель 13, коммутатор 14, блок 15 элементов ИЛИ, регистр 16, умножитель 17, коммутатор 18, блок 19 элементов ИЛИ, коммутатор 20, блок 21 элементов задержки, коммутатор 22, блок 23 элементов ИЛИ, регистр 24 и умножитель 25, а также сумматор 26, логарифмический преобразователь 27, делитель 28, вычитатель 29, формирователь 30 координат, инерциальный навигационный блок 31, сумматор 32, логарифмический преобразователь 33, делитель 34, память 35 эталонов, триггер 36, блок 37 синхронизации, формирователь 38 адреса, формирователь 39 импульсов, элемент И 40, счетчик 41, дешифраторы 42 и 43, регистр 44, коммутаторы 45 и 46, блоки 47 и 48 сравнения, триггер 49, регистр 50, коммутаторы 51 и 52, триггер 53, регистр 54, счетчики 55 группы.

В расчетный момент времени блок 1 формирует детальное цифровое РЛИ опорного участка местности, которое записывается в память 2. Через интервал времени, достаточный для записи в память 2 всех отсчетов наблюдаемого РЛИ, на выходе блока 37 синхронизации начинают формироваться тактовые импульсы, поступающие на адресный вход памяти 2 и на первый вход формирователя 38, формирующего адрес соответствующего элемента эталонного РЛИ для считывания его из памяти 35.

Управление считыванием эталонной информации из памяти 35 и перебором гипотез осуществляется с формирователем 38 адреса, схема которого представлена на фиг. 2, где 38.1, 38,6 - счетчики, 38.2 - сумматор, 38.3 - дешифратор, 38.4, 38.7 - блоки совпадений, 38.5 - блок памяти.

В заданный момент времени блок 37 синхронизации начинает формировать тактовые импульсы, поступающие на адресный вход памяти 2 и в счетчик 38.1, выход которого подключен к блоку 38.4 совпадений и к сумматору 38.2. С первого выхода блока 38.5 памяти на второй вход блока 38.4 совпадений подается код, пропорциональный числу элементов наблюдаемого РЛИ, подлежащего сравнению с эталонным РЛИ. При совпадении текущего числа в счетчике 38.1, пропорционального числу элементов эталонного РЛИ, считанных из памяти 35 для данной j-й гипотезы, с кодом, поступающим из блока 38.5 памяти, блок 38.4 совпадений вырабатывает сигнал, обнуляющий счетчик 38.1. Одновременно с этим выходным сигналом блока 38.4 обнуляется информация в формирователе 41 (4N) каждого канала, опрокидывается триггер 36 и запускается формирователь 39 импульсов.

Счетчик 38.6 формирует текущий код номера обрабатываемой гипотезы j путем подсчета выходных импульсов блока 38.4 совпадений. Выходной сигнал счетчика 38.6 складывается в сумматоре 38.2 с выходным сигналом счетчика 38.1, формируя код текущего номера отсчета эталонного РЛИ для сравнения с наблюдаемым РЛИ, записанным в память 2. При этом выходной сигнал сумматора 38.2 пропорционален сумме номера обрабатываемой гипотезы j и номера элемента эталонного РЛИ в пределах данной гипотезы. С выхода сумматора 38.2 сигнал подается на вход дешифратора 38.3, преобразующего код текущего номера элемента эталонного РЛИ в его адрес в памяти 35. Выходной сигнал дешифратора 38.3 поступает на адресный вход памяти 35 для считывания из нее очередного элемента эталонного РЛИ. Код этого элемента, содержащий информацию о его принадлежности к определенной зоне эталона, подается на вход дешифратора 3.2 в блоке 3 (фиг. 3), преобразующего выходной сигнал памяти 35 в номер канала, в котором накапливаются элементы данной зоны наблюдаемого РЛИ, считываемого из памяти 2.

В результате описанного взаимодействия блоков при обработке каждой j-й гипотезы о взаимном положении наблюдаемого и эталонного РЛИ из памяти 35 считывается столько элементов эталонного РЛИ, сколько их содержится в наблюдаемом РЛИ. При переходе к следующей гипотезе (сдвиг на один элемент) к коду адреса элемента эталонного РЛИ добавляется единица. Число обрабатываемых гипотез формируется в счетчике 38.6, подсчитывая выходные импульсы блока 38.4. В блоке 38.5 хранится априорно заданный код номера последней гипотезы, поступающий на второй вход блока 38.7 совпадений, на первый вход которого подается текущий код номера обрабатываемой гипотезы j. При совпадении указанных кодов блок 38.7 вырабатывает сигнал, поступающий на управляющий вход коммутатора 30.2 (фиг. 4) и на вход блока 30.5 задержки в формирователе 30 координат.

Элементы эталонного РЛИ, считываемые из памяти 35, поступают на управляющий вход распределителя 3 информации и на вход дешифратора 43. Код элемента эталонного РЛИ содержит информацию о его яркости, принадлежности к одной из N однородных зон и о параметрах Т, t, определяющих конкретную реализацию решающей функции для данных условий визирования.

Распределитель 3 информации может быть реализован, например, с помощью блок-схемы, представленной на фиг. 3, где 3.11, 3.12, ..., 3.1N- коммутаторы, 3.2 - дешифратор.

Считывание сигналов из памяти 2 в каждый канал осуществляется через соответствующий коммутатор 3.11, ..., 3.1N, мгновенное состояние которого соответствует распределению элементов по областям эталонного РЛИ. Управление состоянием коммутаторов распределителя 3 осуществляется выходным сигналом дешифратора 3.2, вход которого подключен к информационному выходу памяти 35. Код очередного элемента эталонного РЛИ, содержащий информацию о номере однородной зоны, к которой относится данный элемент, считывается из памяти 35 на вход дешифратора 3.2 по сигналам формирователя 38 адреса, поступающим на адресный вход памяти 35. В соответствии с принятым кодом дешифратор 3.2 формирует на одном из своих выходов сигнал, открывающий входной коммутатор 3.11, ..., 3.1Nсоответствующего канала для прохождения очередного элемента наблюдаемого РЛИ из памяти 2 в сумматор 91 (9N). Одновременно число элементов наблюдаемого РЛИ, обрабатываемых в данном канале, подсчитывается счетчиком 551 (55N).

Для очередной гипотезы о взаимном расположении наблюдаемого и эталонного РЛИ, задаваемой с помощью формирователя 38, в сумматоре 91(9N) соответствующего канала суммируются значения яркостей наблюдаемого РЛИ в пределах очертаний каждой из N областей. В делителе 51 (5N) делится накопленная в сумматоре 91 (9N) яркость на число элементов РЛИ в пределах каждой области, поступающее из счетчика 551 (55N). На выходе делителя 51 (5N) формируется при этом сигнал  , пропорциональный среднему значению яркости наблюдаемого РЛИ для данной области эталона.

, пропорциональный среднему значению яркости наблюдаемого РЛИ для данной области эталона.

Выходной сигнал делителя 51 (5N) проходит через блок 61 (6N) элементов ИЛИ в регистр 71 (7N), выход которого подключен к сигнальным входам коммутаторов 81 (8N), 111 (11N), 121 (12N), 181 (18N), 201 (20N).

По окончании обработки очередной гипотезы на втором выходе формирователя 38 адреса формируется сигнал, запускающий формирователь 39 импульсов, опрокидывающий триггер 36 и пересылающий информацию из сумматоров-накопителей 91 (9N) в делители 51 (5N).

Дальнейшая обработка сигналов производится в соответствии со значениями параметров Т, t для данного эталонного РЛИ. На первом выходе дешифратора 43, вход которого подключен к выходу памяти 35, выделяются разряды, содержащие код параметра Т, который записывается в регистр 44, а на втором его выходе формируется код параметра t, который записывается в регистр 50.

Выходной сигнал триггера 36 отпирает элемент И 40 и коммутаторы 111(11N), 121 (12N). Тактовые импульсы формирователя 39 через открытый элемент И 40 поступают на счетный вход счетчика 41 и на установочный вход регистра 71 (7N). Код средней яркости  с выхода регистра 71 (7N) поступает на информационные входы коммутаторов 81 (8N), 111 (11N), 121(12N), 181 (18N), 201 (20N).

с выхода регистра 71 (7N) поступает на информационные входы коммутаторов 81 (8N), 111 (11N), 121(12N), 181 (18N), 201 (20N).

Текущий код номера тактового импульса с выхода счетчика 41 поступает на вход дешифратора 42 и на входы коммутаторов 45, 51. После прихода первого тактового импульса на выходе дешифратора 42, подключенном к управляющему входу коммутатора 181 (18N), формируется разрешающий сигнал. При этом выходной сигнал регистра 71 (7N) проходит через открытый коммутатор 181 (18N) и блок 191 (19N) элементов ИЛИ на второй вход умножителя 131 (13N), на первый вход которого через открытый коммутатор 121 (12N) также проходит выходной сигнал регистра 71 (7N). На выходе умножителя 131 (13N) формируется значение ( )2 , поступающее на блоки 141 (14N), 211 (21N), 221 (22N). В блоке 211 (21N) выходной сигнал умножителя 131 (13N) задерживается на один период следования тактовых импульсов и через блок 191 (19N) элементов ИЛИ подается на второй вход умножителя 131 (13N).

)2 , поступающее на блоки 141 (14N), 211 (21N), 221 (22N). В блоке 211 (21N) выходной сигнал умножителя 131 (13N) задерживается на один период следования тактовых импульсов и через блок 191 (19N) элементов ИЛИ подается на второй вход умножителя 131 (13N).

В блоке 101 (10N) выходной сигнал регистра 71 (7N), прошедший через открытый коммутатор 111 (11N), также задерживается на один период следования тактовых импульсов и через блок 61 (6N) элементов ИЛИ снова записывается в регистр 71 (7N), сохраняя тем самым код  на все время формирования решающей функции для данной гипотезы. После прихода второго тактового импульса выходной сигнал дешифратора 42 запирает коммутатор 181 (18N).

на все время формирования решающей функции для данной гипотезы. После прихода второго тактового импульса выходной сигнал дешифратора 42 запирает коммутатор 181 (18N).

В регистре 54 записан единичный код, постоянно поступающий в блоки 47, 48. На вход блока 47 с выхода регистра 44 подается код параметра Т для данного эталона. В случае равенства кода Т единице на выходе блока 47 формируется сигнал, опрокидывающий триггер 53, подающий при этом разрешающий сигнал на коммутатор 81 (8N) и запрещающий сигнал на вход коммутатора 46. Выходное напряжение последнего запрещает прохождение через коммутатор 141 (14N) выходных сигналов умножителя 131 (13N). Значение  с выхода регистра 71 (7N) через открытый коммутатор 81 (8N) и блок 151 (15N) элементов ИЛИ проходит в регистр 161 (16N). Если значение параметра Т больше единицы, триггер 53 остается в исходном состоянии, при котором его выходными напряжениями коммутатор 81 (8N) закрыт, а на коммутатор 46 подается разрешающий сигнал.

с выхода регистра 71 (7N) через открытый коммутатор 81 (8N) и блок 151 (15N) элементов ИЛИ проходит в регистр 161 (16N). Если значение параметра Т больше единицы, триггер 53 остается в исходном состоянии, при котором его выходными напряжениями коммутатор 81 (8N) закрыт, а на коммутатор 46 подается разрешающий сигнал.

Код параметра Т с выхода регистра 44 поступает на вход коммутатора 45, на другой вход которого с выхода счетчика 41 подается текущий код номера тактового импульса. При совпадении входных кодов, на выходе коммутатора 45 формируется сигнал, который через открытый коммутатор 46 отпирает коммутатор 141 (14N) для прохождения через него с выхода умножителя 131 (13N) через блок 151 (15N) элементов ИЛИ в регистр 161(16N) значения ( )T.

)T.

На один вход блока 48 с выхода регистра 50 подается код параметра t для данного эталона. В случае равенства единице кода t на выходе блока 48 формируется сигнал, опрокидывающий триггер 49, подающий при этом разрешающий сигнал на коммутатор 201 (20N) и запрещающий сигнал на коммутатор 52. Выходное напряжение коммутатора 52 запрещает прохождение через коммутатор 221 (22N) выходных сигналов умножителя 131 (13N). Значение  с выхода регистра 71 (7N) через открытый коммутатор 201(20N) и блок 231 (23N) элементов ИЛИ проходит в регистр 241 (24N). Если значение параметра t больше единицы, триггер 49 остается в исходном состоянии, при котором его выходными напряжениями коммутатор 201 (20N) закрыт, а на коммутатор 52 подается разрешающий сигнал.

с выхода регистра 71 (7N) через открытый коммутатор 201(20N) и блок 231 (23N) элементов ИЛИ проходит в регистр 241 (24N). Если значение параметра t больше единицы, триггер 49 остается в исходном состоянии, при котором его выходными напряжениями коммутатор 201 (20N) закрыт, а на коммутатор 52 подается разрешающий сигнал.

Код параметра t с выхода регистра 50 поступает на вход коммутатора 51, на другой вход которого с выхода счетчика 41 подается текущий код номера тактового импульса. При совпадении входных кодов на выходе коммутатора 51 формируется сигнал, который через открытый коммутатор 52 отпирает коммутатор 221 (22N) для прохождения через него с выхода умножителя 131 (13N) через блок 231 (23N) элементов ИЛИ в регистр 241(24N) значения ( )t.

)t.

По окончании формирования значений ( )T, (

)T, ( )t на первом выходе дешифратора 42 формируется сигнал, опрокидывающий триггер 36, обнуляющий код в счетчиках 41, 551 (55N), в регистрах 44, 50, 161 (16N), 241 (24N), опрокидывающий триггеры 49, 53, а также поступающий в формирователь 30. Триггер 36 запрещает прохождение сигналов через коммутаторы 111 (11N), 121 (12N) и элементы И 40. Выходной код регистра 161 (16N) поступает на первый вход умножителя 171 (17N), на второй вход которого с выхода счетчика 551 (55N) подается код Nк. На выходе умножителя 171 (17N) формируется значение (

)t на первом выходе дешифратора 42 формируется сигнал, опрокидывающий триггер 36, обнуляющий код в счетчиках 41, 551 (55N), в регистрах 44, 50, 161 (16N), 241 (24N), опрокидывающий триггеры 49, 53, а также поступающий в формирователь 30. Триггер 36 запрещает прохождение сигналов через коммутаторы 111 (11N), 121 (12N) и элементы И 40. Выходной код регистра 161 (16N) поступает на первый вход умножителя 171 (17N), на второй вход которого с выхода счетчика 551 (55N) подается код Nк. На выходе умножителя 171 (17N) формируется значение ( )TNk, поступающее в сумматор 32. С выхода сумматора 32 величина

)TNk, поступающее в сумматор 32. С выхода сумматора 32 величина  (

( )TNk поступает в преобразователь 33, который осуществляет формирование логарифма входного сигнала с использованием разложения в ряд функции

)TNk поступает в преобразователь 33, который осуществляет формирование логарифма входного сигнала с использованием разложения в ряд функции

lnx = 2 1+

1+

Выходной сигнал преобразователя 33 поступает на первый вход делителя 34, на второй вход которого с выхода регистра 44 подается код параметра Т. На выходе делителя 34 формируется значение 1/T ln  (

( )TNk, поступающее в вычитатель 29.

)TNk, поступающее в вычитатель 29.

Выходной код регистра 241 (24N) поступает на первый вход умножителя 251 (25N), на второй вход которого с выхода счетчика 551 (55N) подается код Nк. На выходе умножителя 251 (25N) формируется значение ( )t, поступающее в сумматор 26. С выхода сумматора 26 величина

)t, поступающее в сумматор 26. С выхода сумматора 26 величина  (

( )tNk поступает в логарифмический преобразователь 27.

)tNk поступает в логарифмический преобразователь 27.

Выходной сигнал преобразователя 27 поступает на первый вход делителя 28, на второй вход которого с выхода регистра 50 подается код параметра t. На выходе делителя 28 формируется значение 1/t ln  (

( )tNk , поступающее в вычитатель 29.

)tNk , поступающее в вычитатель 29.

Значения решающей функции

ФT,t=1/T ln  (

( )TNk-1/t ln

)TNk-1/t ln  (

( )tNk с выхода вычитателя 29 поступают в формирователь 30 координат, реализация которого представлена на фиг. 4, где 30.1 - блок сравнения, 30.2, 30.3 - коммутаторы, 30.4 - память, 30.5 - блок задержки.

)tNk с выхода вычитателя 29 поступают в формирователь 30 координат, реализация которого представлена на фиг. 4, где 30.1 - блок сравнения, 30.2, 30.3 - коммутаторы, 30.4 - память, 30.5 - блок задержки.

Блок 30.1 осуществляет сравнение значения решающей функции Фjочередной гипотезы, поступающего с коммутатора 8, с величиной, записанной в памяти 30.4. При этом при обработке первой гипотезы в память 30.4 заносится значение Ф1. Для последующих гипотез блок 30.1 при условии, что значение Фj очередной гипотезы меньше значения решающей функции, записанного в памяти 30.4, вырабатывает сигнал, открывающий коммутатор 30.3 для прохождения через него в память 30.4 значения Фj с вычитателя 29. В противном случае коммутатор 30.3 закрыт и в памяти 30.4 сохраняется код предшествующего значения решающей функции и ее координат. Таким образом, после перебора всех заданных гипотез в памяти 30.4 оказывается записанным код наименьшего значения решающей функции и ее координаты (так как номер гипотезы однозначно соответствует сдвигу наблюдаемого РЛИ относительно эталона).

После обработки последней гипотезы по сигналу блока 38.7 совпадений открывается коммутатор 30.2 для прохождения в блок 31 координат наименьшего значения решающей функции из памяти 30.4. Эти координаты соответствуют отклонению ЛА от расчетной траектории и служат для коррекции полета ЛА к цели. Выходной сигнал блока 30.5 задержки обнуляет код памяти 30.4 после его выдачи в блок 31 и код счетчика 38.6, подготовляя тем самым систему к следующему сеансу радиолокационных измерений.

Заявляемая система обеспечивает оптимальное решение навигационной задачи при произвольных распределениях флюктуаций отраженного сигнала, поскольку параметры Т, t решающей функции определяют экспериментально в процессе формирования эталона на основе анализа условий достижения максимальной вероятности правильного определения координат ЛА в данных условиях. В процессе полета ЛА адаптивно реализуют оптимальную решающую функцию для каждого конкретного опорного участка местности, используя записанные в памяти значения параметров Т, t.

Использование заявляемой системы позволяет практически на порядок повысить точность определения координат ЛА по сравнению с прототипом при полетах над участками местности с произвольным характером флюктуаций отраженного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

| Система для распознавания дактилоскопических отпечатков | 1991 |

|

SU1836696A3 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЗАДАННОГО ЧИСЛА ИМПУЛЬСОВ | 1993 |

|

RU2066921C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| СПОСОБ И УСТРОЙСТВО РАДИОАКТИВНОГО КАРОТАЖА | 1996 |

|

RU2092876C1 |

Изобретение относится к вычислительной технике и может быть использовано для управления полетом летательного аппарата (ЛА) на основе результатов совместной обработки информации инерциальной навигационной системы и сравнения карт местности. Устройство содержит радиолокационный блок 1, память 2 текущих данных, распределитель 3 информации, формирователи 4 оценки средней интенивности сигналов, группы содержащие делитель 5, блок 6 элементов ИЛИ, регистр 7, коммутатор 8, сумматор 9, блок 10 элементов задержки, коммутаторы 11 и 12, умножитель 13, коммутатор 14, блок 15 элементов ИЛИ, регистр 16, умножитель 17, коммутатор 18, блок 19 элементов ИЛИ, коммутатор 20, блок 21 элементов задержки, коммутатор 22, блок 23 элементов ИЛИ, регистр 24 и умножитель 25, а также сумматор 26, логарифмический преобразователь 27, делитель 28, вычитатель 29, формирователь 30 координат, инерциальный навигационный блок 31, сумматор 32, логарифмический преобразователь 33, делитель 34, память 35 эталонов, триггер 36, блок 37 синхронизации, формирователь 38 адреса, формирователь 39 импульсов, элемент И 40, счетчик 41, дешифраторы 42 и 43, регитр 44, коммутаторы 45 и 46, блоки 47 и 48 сравнения, триггер 49, регистр 50, коммутаторы 51 и 52, триггер 53, регистр 54, счетчики 55 группы. Устройство позволяет повысить точность определения местоположения ЛА. 4 ил.

СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА, содержащая блок синхронизации, выход которого соединен с входом памяти текущих данных, группу формирователей оценки средней интенсивности сигналов, формирователь координат, выход которого соединен с входом инерциального навигационного блока, радиолокационный блок, выход которого соединен с входом памяти текущих данных, память эталонов, отличающаяся тем, что в нее введены группа счетчиков, распределитель информации, формирователь адреса, формирователь импульсов, три регистра, два блока сравнения, счетчик, два сумматора, два логарифмических преобразователя, два делителя, два дешифратора, три триггера, вычитатель, четыре коммутатора, элемент И, причем выход блока синхронизации через формирователь адреса соединен с входами памяти эталонов, формирователей оценки средней интенсивности сигналов группы, формирователя импульсов, выход которого через элемент И соединен с входами формирователей оценки средней интенсивности сигналов группы и счетчика, выход которого соединен с входами первого и второго коммутаторов и через первый дешифратор с входами формирователей оценки средней интенсивности сигналов группы, счетчика, первого и второго регистров, первого, второго и третьего триггеров, счетчиков группы, выходы которых соединены с входами формирователей оценки средней интенсивности сигналов группы, выходы которых соединены с входами первого и второго сумматоров, выходы которых соединены с входами соответственно первого и второго логарифмических преобразователей, выходы которых через соответственно первый и второй делители соединены с входами, вычитателя, выходы которого и первого дешифратора соединены с входами формирователя координат, выход которого соединен с входом формирователя адреса, выходы памяти текущих данных и памяти эталонов соединены с входами распределителя информации, выход которого соединен с входами счетчиков группы и формирователей оценки средней интенсивности сигналов группы, выход памяти эталонов соединен с входом второго дешифратора, выходы которого соединены с входами первого и второго регистров, выход первого регистра соединен с входами первых коммутатора, делителя и блока сравнения, выход второго регистра - с входами вторых коммутатора, делителя и блока сравнения, выход третьего регистра - с входами первого и второго блоков сравнения, выходы которых соединены с входами соответственно второго и третьего триггеров, выходы которых соединены с входами формирователей оценки средней интенсивности сигналов группы и входами соответственно третьего и четвертого коммутаторов, выходы первого и второго коммутаторов через соответственно третий и четвертый коммутаторы соединены с входами формирователей оценки средней интенсивности сигналов группы.

| Патент США N 5072396, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

Авторы

Даты

1994-10-30—Публикация

1992-09-18—Подача