I

-CI

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1978 |

|

SU748439A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегратор с автоматической коррекцией нулевого уровня | 1982 |

|

SU1108471A1 |

| Интегратор с автоматической коррекцией нулевого уровня | 1983 |

|

SU1104539A1 |

| Интегратор | 1980 |

|

SU928369A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Интегратор с запоминанием | 1984 |

|

SU1228122A1 |

| Интегрирующее устройство | 1983 |

|

SU1105903A1 |

Изобретение относится к вычислительной и измерительной технике. С целью увеличения времени и повышения точности интегрирования устройство имеет два операционных усилителя 1 и 2 и третий операционный усилитель 3, осуществляющий коррекцию дрейфа операционных усилителей 1 и 2, которые поочередно подключаются к интегрирующему конденсатору 4. В результате этого осуществляется непрерывный процесс интегрирования в течение длительных интервалов времени. 2 ил.

ю/ъ

12/13/

П

15

/

/

а

/

V

СП

ЗЭ ND

со

т

Изобретение относится к вычислительной и измерительной технике и может быть использовано для интегрирования электрических сигналов в системах автоматического регулирования.

Цель изобретения - увеличение времени и повышение точности интегрирования.

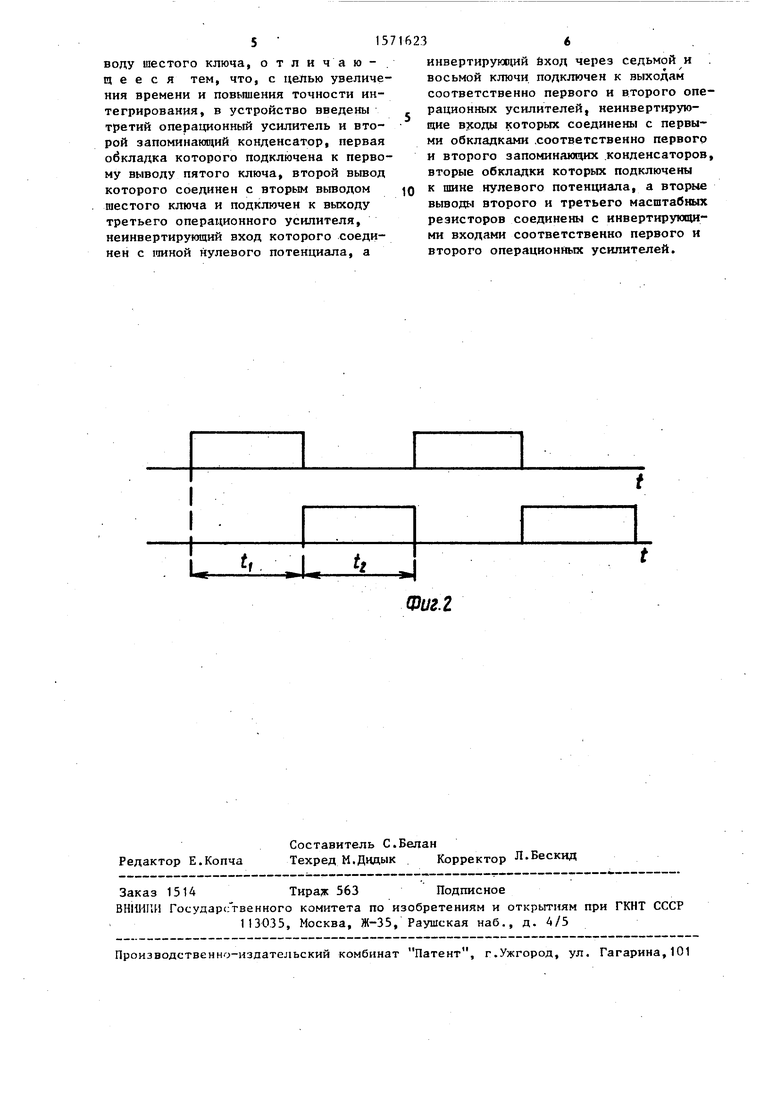

На фиг. 1 приведена схема устройст ва для интегрирования сигнала; на фиг. 2 - импульсные последовательности для управления ключами.

Устройство содержит первый 1, второй 2 и третий 3 операционные усили- тели (ОУ), интегрирующий конденсатор 4, первый 5 и второй 6 запоминающие конденсаторы, масштабные резисторы 7- 9 и ключи 10-17. Первая обкладка интегрирующего конденсатора 4 соединена 2Q усилителей поддерживать непрерыв25

через резистор 8 с входом устройства, через ключ 11 с интегрирующим входом ОУ 1 и ключ 10 с инвертирующим входом ОУ 2. Неинвертирующие входы ОУ 1 и ОУ 2 подключены соответственно через запоминающие конденсаторы 5 и 6 к шине нулевого потенциала и через ключ 14 и 15 к выходу 03 3. Выходы ОУ 1 и ОУ 2 подключены соответственно через ключи 16 и 17 к инвертирующему JQ входу ОУ 3 и через ключи 12 и 13 к второй обкладке интегрирующего конденсатора 4.

Устройство для интегрирования сигнала работает следующим образом.

В процессе интегрирования ОУ 1 и 2 поочередно подключаются к интегрирующему конденсатору 4 на равные интервалы времени. Ключи управляются двумя импульсными последовательностями, сдвинутыми друг относительно друга на полпериода (фиг.2).

В течение первого полупериода t1 замкнуты ключи 11,12,15 и 17, а ключи 10,13,14 и 16 разомкнуты. Ключи 11 и 12 подключают к интегрирующему конденсатору 4 вход и выход ОУ 1, который обеспечивает интегрирование входного сигнала. Ключи 15 и 17 включают ОУ 3 коррекции дрейфа в обратную $Q связь ОУ 2. При этом на запоминающем конденсаторе 6 устанавливается компенсирующее напряжение, равное по значению и противоположное по знаку дрейфу ОУ 2.

В течение второго полупериода t2 замыкаются ключи 10,13,14 и 16, а . ключи 11,12,15 и 17 размыкаются. Ключи 10 и 13 подключаются к ннтегрирую40

45

55

ный процесс интегрирования и полностью устранить погрешности, связанные с цепями коррекции дрейфа. Кроме того, отсутствие в контуре интегрирования дополнительных инерционных звеньев повышает точность и снимает связанные с этим ограничения на форму входного сигнала.

Таким образом, в предлагаемом устройстве за счет устранения влияния коррекции дрейфа повышается точность интегрирования п течение длительных интервалов времени.

Предлагаемое устройство может бить использовано в интегрирующих, пропорционально-интегрирующих, дифЛеренцн- рующих и других звеньях различных систем с высокими требованиями к точности измерений и качеству регулирования. Формула изобретения

Устройство для интегрирования сигнала, содержащее последовательно соединенные первый масштабный резистор, первый вывод которого является входом устройства, и интегрирующий конденсатор, обкладки которого через первый и второй ключи соединены соответственно с инвертирующим входом и выходом первого операционного усилителя и через третий и четвертый ключи соответственно с инвертирующим входом и выходом второго операционного усилителя, с пятого по восьмой ключи, второй и третий масштабные резисторы, первые выводы которых соединены с шиной нулевого потенциала, первый запоминающий конденсатор, первая обкладка которого подкпючеча к первому выщему конденсатору 4 вход и выход ОУ 2 который продолжает обеспечивать процесс интегрирования. При этом ключи

15и 17 разомкнуты и запомненное напряжение на конденсаторе. 6 компенсирует дрейф ОУ 2. При размыкании ключей 11 и 12 и замыкании ключей 14 и

16происходит отключение ОУ 1 от интегрирующего конденсатора 4 и подключение его к ОУ 3. При этом на запоминающем конденсаторе 5 устанавливается напряжение, компенсирующее дрейф ОУ 1 В следующем интервале времени снова подключается ОУ 1 к интегрирующему конденсатору 4, а ОУ 2 отключается

и т.д.

Предлагаемое устройство позволяет за счет поочередной работы операционQ усилителей поддерживать непрерыв5

Q

$Q 40

45

55

ный процесс интегрирования и полностью устранить погрешности, связанные с цепями коррекции дрейфа. Кроме того, отсутствие в контуре интегрирования дополнительных инерционных звеньев повышает точность и снимает связанные с этим ограничения на форму входного сигнала.

Таким образом, в предлагаемом устройстве за счет устранения влияния коррекции дрейфа повышается точность интегрирования п течение длительных интервалов времени.

Предлагаемое устройство может бить использовано в интегрирующих, пропорционально-интегрирующих, дифЛеренцн- рующих и других звеньях различных систем с высокими требованиями к точности измерений и качеству регулирования. Формула изобретения

Устройство для интегрирования сигнала, содержащее последовательно соединенные первый масштабный резистор, первый вывод которого является входом устройства, и интегрирующий конденсатор, обкладки которого через первый и второй ключи соединены соответственно с инвертирующим входом и выходом первого операционного усилителя и через третий и четвертый ключи соответственно с инвертирующим входом и выходом второго операционного усилителя, с пятого по восьмой ключи, второй и третий масштабные резисторы, первые выводы которых соединены с шиной нулевого потенциала, первый запоминающий конденсатор, первая обкладка которого подкпючеча к первому вы5 157

воду шестого ключа, отличающееся тем, что, с целью увеличения времени и повышения точности интегрирования, в устройство введены третий операционный усилитель и второй запоминающий конденсатор, первая обкладка которого подключена к первому выводу пятого ключа, второй вывод которого соединен с вторым выводом шестого ключа и подключен к выходу третьего операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала, а

L. «f

6236

инвертирующий йход через седьмой и восьмой ключи подключен к выходам соответственно первого и второго операционных усилителей, неинвертирующие входы которых соединены с первыми обкладками соответственно первого и второго запоминающих конденсаторов, вторые обкладки которых подключены g к шине нулевого потенциала, а вторые выводы второго и третьего масштабных резисторов соединены с инвертирующими входами соответственно первого и второго операционных усилителей.

t

Фиг. 2

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для интегрирования сигнала | 1984 |

|

SU1201853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-02-29—Подача