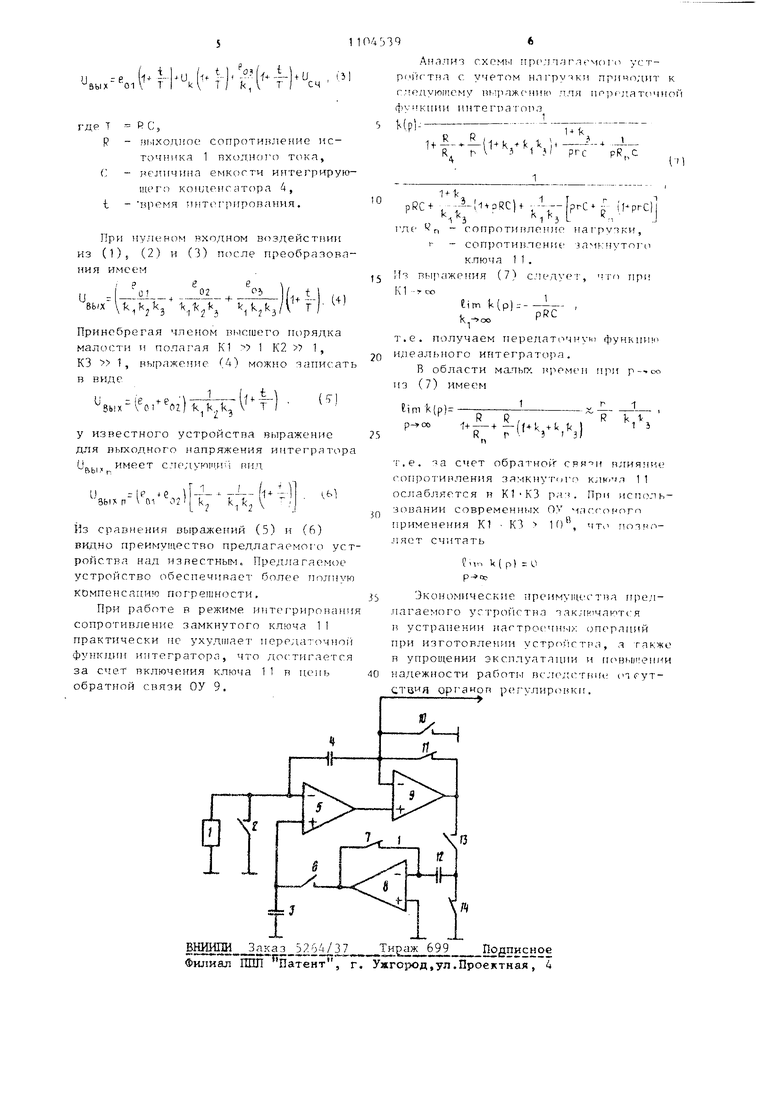

Изобретение относите, к элек.тр1)ни ке и радиотехнике н быть ислюл зовано ы различных устроит/п ах автоматики и измерительной техники. ИзиесПы интегратс,р1,1, построенные на основе усилителе с аитоматической коррекцией нулевого уровня и состг Л|Дие оснонного операционного усилителя (ОУ) , охт аченного емкостной обратной связью, дополнительного усилителя, вход которого подсоединен к выходу основного ОУ, запоминающего конденсатора и ключа, подключенного к неинвертирующему входу основного ОУ. К инвертирующему входу основного ОУ под.ключены источник входного тока интегрирующий конденсатор и входной ключ, второй; вывод-которого подключен к общей (нулевой) шине интегратора. Такие интеграторы позволяют повысить точность интегрирования входного воздействия за счет компенсации напряжения смещения (и его дрейфа) основного ОУ . Однако напряжение смещения компен сируется неполностью, что обусловлен запоминанием напряжения смещения и на интегрирующем конденсаторе. Кроме того, на интетрирующем конденсаторе запоминается напряжение смещения дополнительного усилителя, что также снижает точность интегрирования. Наиболее близким по технической сущности к предлагаемому изобретению является интегратор с автоматической коррекцией нулевого уровня, содержащий первый и второй ОУ, замыкающие и размыкающие ключи, интегрируюш 1й конденсатор, первый и второй запоминающие конденсаторы, причем инвертирующий вход первого ОУ подключен к источнику входного тока, через первый замыкающий ключ соединен с шиной нулевого потенциала и через интегрирующий конде)1сатор - с выходом ОУ, выход второго ОУ через второй замыкающий ключ подключен к неинвертирую щему входу первого ОУ, соединенному через первый запоминаюш 1Й конденса тор с 1)иной нулевого потенциала, инвертирующий вход второго ОУ через третий замыкающий ключ соединен с его вьг ;одом и через второй запоминаю щий конденсатор подключен к общему выводу последовательно соединенных четрертс го и пятого замьжающих ключей, BKJiHi4t:}iHbK между выхо.л,ом первого ОУ и шиной нулевого лотеущиала, выход первого ОУ является ныходсж устройства 12. Недостатком известного устройства является неполная комп(нсг;ция погрешности, обусловленная запоминанием напряжения погреилюсти на интегриу)у1ощем конденсаторе. Целью изобретения является поньпиение точности интегрирования путем устранения напряжения погрешности на интегрирующем конденсаторе. Поставленная цель достигается тем, что в интегратор с автоматической коррекцией нулевого уровня, содержащий первый операционный усилитель, инвертирующий вход которого подключен к источнику входного тока, первой обкладке интегрирующего конденсатора и через первый замьгкаю1чий ключ соединен с. шиной нулевого потенциала, второй операционный усилитель, выход которого через второй замыкающий ключ подключен к неинпертирутащему входу первого операционного усилителя, соединенному через первый запоминающий конденсатор с шиной нулевого потенциала, инвертирующий вход второго операционного усилителя соединен с первой обкладкой второго запоминающего конденсатора и через первьвд размъ кающий ключ - с его выходом, вторая обкладка второго запоминающего конденсатора соединена с первым выходом третьего замыкающего ключа и через второй размыкающий КЛУ1Ч подключе1 а к шине нулевого потенциала, и четвертый замыкающий ключ, введены третий операционный усилитель и третий размыкающий ключ, причем выход первого операционного усилителя подключен к неинвертирующему входу третьего операционного усилителя, инвертирующий вход котоporQ соединен с второй обкладкой интегрирующего конденсатора и через четвертый замыкающий ключ подключен к шине нулевого потенциала, третий размыкающий ключ включен между инвертирующим входом и выходом третьего операционного усилителя, соединенным с вторым выводом третьего замыкающего ключа, а неинвертнрующий вход второго операционного усилителя соединен с тиной нулевого потенциала. Сущность изобретения заключается в том, что в режиме запоминания напряжения компеисапии обе обкладки интегрирусмого конденсатора оказываются соединенными с шиной нулевого потенциала, что устраняет запоминание напряжения погрешности на интегрирующем конденсаторе, На чертеже приведена функциональная схема интегратора с автоматической коррекцией нулевого уровня. Интегратор содержит источник 1 входного тока, первый замыкающий ключ 2, первый запоминающий конденсатор 3, интегрируюп1Ий конденсатор 4, первый операционный усилитель 5, второй замыкающий ключ 6, первый размыкающий ключ 7, второй операцион ный усилитель 8, третий операционный усилитель 9, четвертый замыкающий 10 и третий размпкающий 11 ключи, второ запоминающий конденсатор 12, третий замыкающий 13 и второй размыкающий 14 ключи. Между инвертирующим входом ОУ 5 и шиной нулевого потенциала включены источник .1 входного тока и замыкающий ключ 2, а между неинверти ругощим входом ОУ 5 и шиной нулевого потенциала - первый запоминающий конденсатор 3, интегрирующий конденсатор 4 включен между инвертирующими входами ОУ 5 и ОУ 9, замыкающий ключ 6 включен между выходом ОУ 8 и не инвертирующим входом ОУ 5, размыкающий ключ 7 включен между вькодом ОУ 8 и его инвертирующим входом, неинвертирующий вход ОУ 8 соединен с шиной нулевого потенциала, инвертиру щий вход ОУ 8 через второй запомикаюш н конденсатор 12 соединен с общим выводом последовательно соединенных замыкающего 13 и размыкающего 14 ключей, включенных между выходом ОУ 9 и шиной нулевого потенциала, размыкающий ключ 11 включен между выходом ОУ 9 и его инвертирующим вхо дом, замыкающий ключ 10 включен между инвертирующим входом ОУ 8 и шиной нулевого потенциала. Инвертирующий вход ОУ 9 является выходом устройства. В качестве ОУ 5 и 8 могут быть использованы ОУ широкого применения с полевыми транзисторами во входном каскаде, имеющие малую величину входного тока и большое значение коэффициента подавления инфазного сигнала. Таким требованиям удовлетво ряет ОУ типа 140УД8А. В качестве ОУ 8 может быть использован любой ОУ широкого применения, например 153УД2 В качестве ключей 2, 6, 7, 10, 11, 13 и 14 могут быть использованы две микросхемы K590KR5, каждая из которых содержит четыре независимых КМОП ключа. Конденсаторы 3, 4 и 12 должны иметь минимальньш ток уте:,чки и малую постоянную времени поля. Интегратор с автоматической коррекцией нулевого уровня работает в двух режимах: режиме запоминания компенсирующего напряжения и п режиме интегрирования. В режиме запоминания компенсирующего напряжения ключи 2, 6, 10 и 13 замкнуты, а ключи 7, 11 и 14 разомкнуты. Замкнутый ключ 2 отключает источник входного тока и совместно с замкнутым ключом 10 обеспечивает обнуление конденсатора 4. Замкнутый в этом режиме ключ 6 обеспечивает подключение выхода ОУ 8 к конденсатору 3, а замкнутый ключ 13 - подключение выхода ОУ 9 к конденсатору 12, В результате на конденсаторе 3 устанавливается компенсирующее напряжение и равное / и -е -fe -и к 01 1+1. К 1. C1Z/ 1+k, 03 ,з напряжение смещения нуля 5, 8 и 9 ОУ соответственно, коэффициенты передачи 5, 8 и 9 ОУ соответственно. напряжение на конденсаторе 12. Напряжение на интегрирующем конденсаторе 4 в этом режиме равно нулю (Uc4 0). в режиме интегрирования ключи 2, 6, 10 и 13 разомкнуты, а ключи 7, 11 и 14 замкнуты. В этом режиме, помимо интегрирования входного воздействия, осуществляется запоминанир t., 8 ОУ напряжения смещения нуля на конденсаторе 12 Ucu «- При отсутствий входного возлейгтпия выходное напряжение интегратора U,, в режиме интегрирования опрсдр:;я тся следующим выражением

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с автоматической коррекцией нулевого уровня | 1982 |

|

SU1108471A1 |

| Интегратор с автоматической кор-РЕКциЕй НулЕВОгО уРОВНя | 1978 |

|

SU811285A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Устройство для извлечения корня | 1978 |

|

SU811292A1 |

| Интегратор | 1980 |

|

SU920756A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| Устройство для интегрирования сигнала | 1988 |

|

SU1571623A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841056A1 |

| Интегратор с запоминанием | 1984 |

|

SU1228122A1 |

ИНТЕГРАТОР С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ НУЛЕВОГО УРОВНЯ, содержащий первый операционный усилитель, инвертирующий пко; к(торого подклю4eit к ист

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3667055, кл | |||

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Интегратор с автоматической кор-РЕКциЕй НулЕВОгО уРОВНя | 1978 |

|

SU811285A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-25—Подача