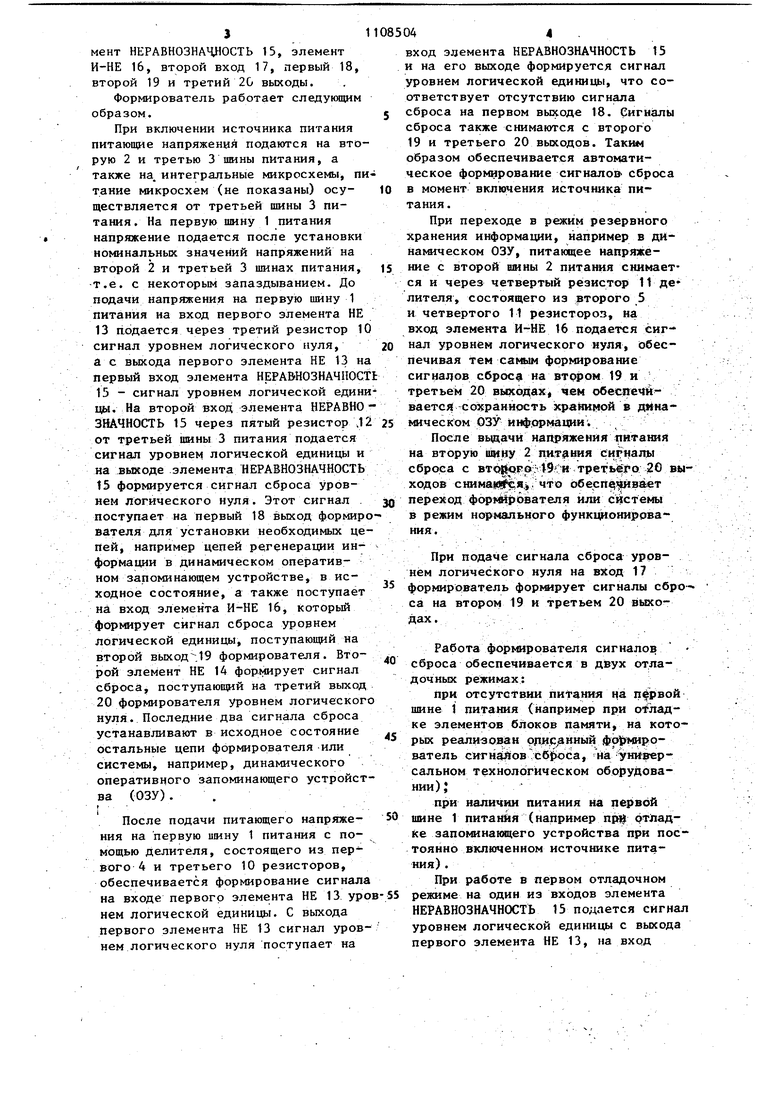

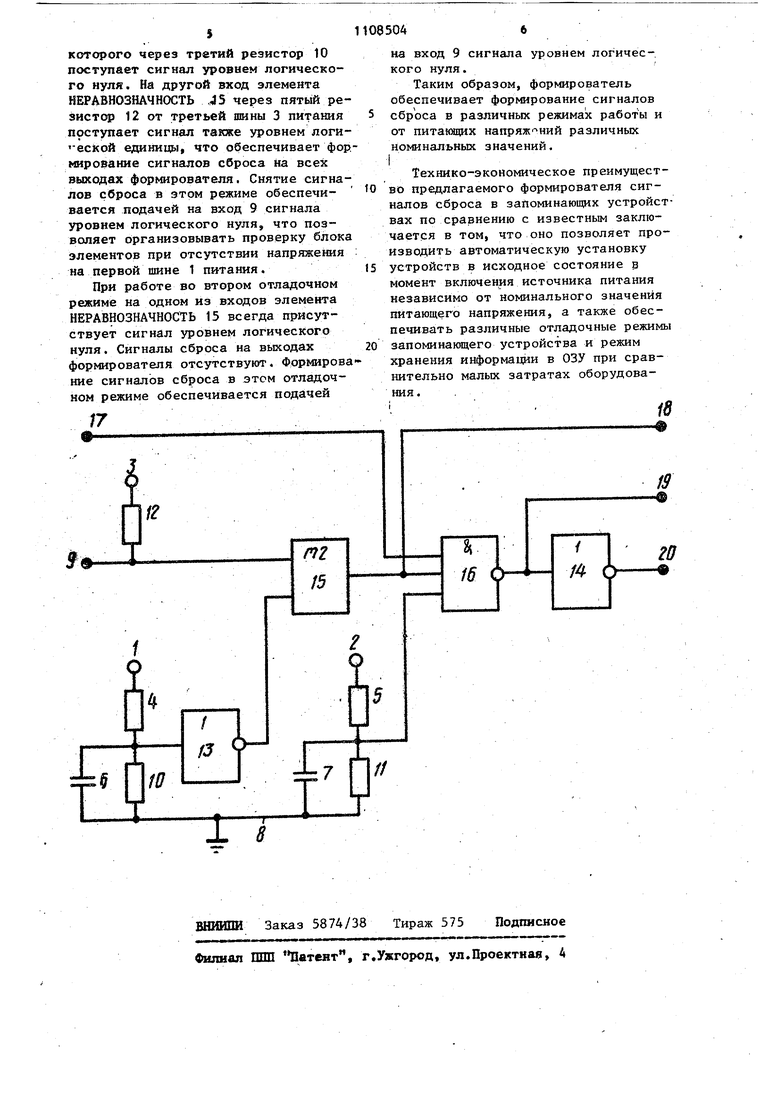

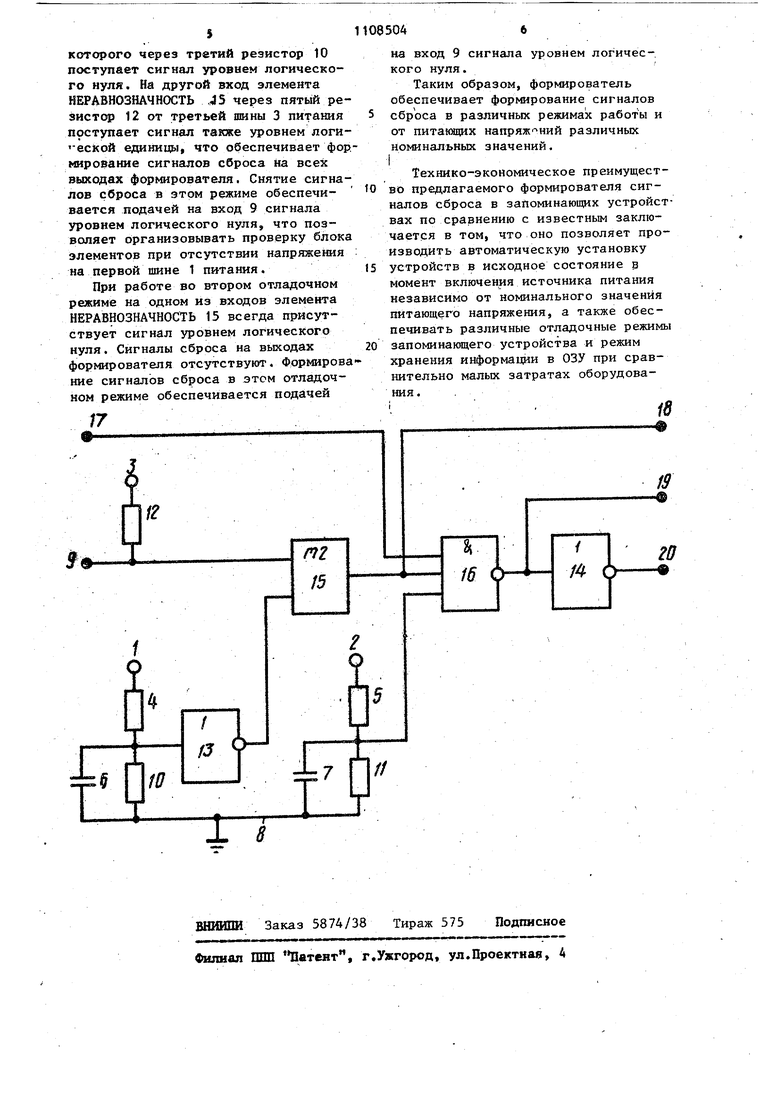

Изобретение относится к вычислительной технике и может быть исполь зовано в запоминающих устройствах, в которых требуется автоматическая установка в исходное состояние в момент включения источника питания Известен формирователь сигналов. в котором для автоматической установки блока в исходное состояние ис пользуется разделительный элемент, подключенный к источнику питания и сннхровходам триггеров, информацион ные входы которых подключены к шине нулевого потенциала, а в качестве разделительного элемента использует ся резистор ЦПНедостатками этого устройства являнугся ограниченные функциональны возможности, обусловленные отсутствием организации отладочных- режимов и невозможностью формирования сигналов сброса по включению источника питания с напряжением, превышающим .напряжение питания микросхем, а так же недостаточно высокая надежность функционирования устройства. Наиболее близким техническим решением к изобретению является фор мирователь сигналов установки в исходное состояние при включении пита ния устройства задержки импульсов, содержащий резистор, конденсатор, одновибратор, шину питания и шину нулевого потенциала, причем первый вывод резистора соединен с тиной питания, а второй вывод - с входом одновибратора и первым выводом конд сатора, второй вывод которого соеди нен с шиной нулевого потенциала 21 Однако этот формирователь не поз воляет формировать,сигналы сброса по включению источника питания с напряжением, превышающим напряжение питания микросхемы, а также организовывать отладочные режимы, что ограничивает его область применения. Цель изобретения - расширение об ласти применения формирователя за счет обеспечения формирования сигналов сброса в различных режимах работы блоков памяти и при различных напряжениях питания. Поставленная цель достигается тем, что в формирователь сигналов сброса для блоков памяти, содержащий ограничительные и накопительные элементы, причем первый вывод первого ограничительного элемента сое-: динен с первой шиной питания, а второй вывод - с первым выводом первого накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, первый вывод второго ограничительного элемента соединен со второй шиной питания, а второй вывод - с первым выводом . второго накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, введены третий, четвертый и пятый ограничительные элементы, элементы НЕ, элементы НЕРАВНОЗНАЧНОСТЬ и элементы И-НЕ, причем вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с выходом первого элемента НЕ, вход которого соединен с вторым выводом первого ограничительного элемента: и первым выводом третьего ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, второй вход элемента НЕРАВНОЗНАЧНОСТЬ и первый вывод пятого ограничительного элемента являются первым входом формирователя, второй бывод пятого ограничительного элемента соединен с третьей шиной питания, выход элемента НЕРАВНОЗНАЧНОСТЬ и первый вход элемента И-НЕ являются первым выходом устройства, второй вход,элемента И-НЕ является вторым входом устройства, а третий вход соединен с вторым выводом второго ограничительного элемента и первь№1 выводом четвертого ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, выход элемента И-НЕ и вход второго элемента НЕ являются вторым выходом устройства, третьим выходом которого является выход второго элемента НЕ. - . На чертеже представлена принципильная схема формирователя сигналов сброса для блоков памяти. Формирователь сигналов сброса одержит первую 1, вторую 2 и третью 3 шины питания, первый 4 и второй 5 ограничительные элементы, например резисторы, первый 6 и второй 7 на- i копительные элементы, например коненсаторы, шину 8 нулевого потенциала, первый вход 9, третий 10, четвертый 11 и пятый 12 ограничительные элементы, например резисторы, первый 13 и второй 14 элементы НЕ, элемент НЕРАВНОЗНАЧНОСТЬ 15, элемент И-НЕ 16, второй вход 17, первый 18, второй 19 и третий 20 выходы. Формирователь работает следующим образом. При включении источника питания питающие напряжения подаются на вторую 2 и третью 3 имны питания, а также на, интегральные микросхемы, пи тание микросхем (не показаны) осуществляется от третьей шины 3 питания. На первую шину 1 питания напряжение подается после установки номинальных значений напряжений на второй 2 и третьей 3 шинах питания, т.е. с некоторым запаздыванием. До подачи напряжения на первую шину 1 питания на вход первого элемента НЕ 13 аодается через третий резистор 1 сигнал уровнем логического нуля, ас выхода первого элемента НЕ 13 н первый вход элемента НЕРАВНОЗНАЧНОСТ 15 - сигнал уровнем логической един цы. На второй вход элемента НЕРАВНО ЗНАЧНОСТЬ 15 через пятый резистор ,1 от третьей шины 3 питания подается сигнал уровнем логической единицы и на выходе элемента НЕРАВНОЗНАЧНОСТЬ 15 формируется сигнал сброса уровнем логического нуля. Этот сигнал поступает на первый 18 выход формир вателя для установки необходимых це Пей, например цепей регенерации информации в динамическом оперативном запоминающем устройстве, в исходное состояние, а также поступает на вход элемента И-НЕ 16, который формирует сигнал сброса уровнем логической единицы, поступающий на второй выход.19 формирователя. Второй элемент НЕ 14 формирует сигнал сброса, поступающий на третий выход 20 формирователя уровнем логическог нуля. Последние два сигнала сброса устанавливают в исходное состояние остальные цепи формирователя или системы, например, динамического оперативного запоминающего устройст ва (ОЗУ). . t . После подачи питающего напряжения на первую шину 1 питания с помощью делителя, состоящего из первого 4 и третьего 10 резисторов, обеспечивается формирование сигнала на входе первого элемента НЕ 13 уро нем логической единицы. С выхода первого элемента НЕ 13 сигнал уровнем логического нуля поступает на 44 вход элемента НЕРАВНОЗНАЧНОСТЬ 15 и на его выходе формируется сигнал уровнем логической единицы, что соответствует отсутствию сигнала сброса на первом выходе 18. Сигналы сброса также снимаются с второго 19 и третьего 20 выходов. Таким образом обеспечивается автоматическое формирование сигналов- сброса в момент вклтения источника питания. При переходе в режим резервного хранения информации, например в дИнаьмческом ОЗУ, питающее напряжение с второй вшны 2 питания снимается и через четвертый резистор 11 де лителя, состоящего из второго 5 и четвертого 11 резисторов, на вход элемента И-НЁ 16 подается сигнал уровнем логического нуля, обеспечивая тем самым формирование сигналов сбросу на втрром 19 и третьем 20 выходах чем обеспечивается сохранность хранимой в динамическом ОЗУ йнф.ормации. После вьщачй напряжения питани на вторую иф1ну 2 питания . сброса с BTQ Fpvi9 H третьёго 2б выходов снима в я., что обесп вавт переход фор14 рователя или системы в режим нормального функционирования. При подаче сигнала сброса уровнем логического нуля на вХод 17 формирователь формирует сигналы сброса на втором 19 и третьем 20 выходах., .: Работа формирователя сигналов сброса обеспечивается в дВух отладочных режимах: при отсутствии питания на первой шине 1 питания (например при отладке элементов блоков памяти, на которых реализован фp 4иpoватель сигна|йовсброса, на универсальном технологическом оборудовании) J при наличии питания на первой шине 1 питания (например П1 отладке запоминанщего устройства при постоянно Включенном источнике питания) . При работе в первом отладочном режиме на один из входов элемента НЕРАВНОЗНАЧНОСТЬ 15 подается сигнал уровнем логической единицы с выхода первого элемента НЕ 13, на вход

которого через третий резистор 10 поступает сигнал уровнем логического нуля. На другой вход элемента НЕРАВНОЗНАЧНОСТЬ .45 через пятый резистор 12 от третьей шины 3 питания поступает сигнал также уровнем логиеской единицы, что обеспечивает фор мирование сигналов сброса На всех выходах формирователя. Снятие сигналов сброса в этом режиме обеспечивается подачей на вход 9 сигнала уровнем логического нуля, что позволяет организовывать проверку блока элементов при отсутствии напряжения на первой шине 1 питания.

При работе во втором отладочном режиме на одном из входов элемента НЕРАВНОЗНАЧНОСТЬ 15 всегда присутствует сигнал уровнем логического нуля. Сигналы сброса на выходах формирователя отсутствуют. Формирование сигналов сброса в этом отладочном режиме обеспечивается подачей

17

---;11085046

на вход 9 сигнала уровнем логического нуля.

Таким образом, формирователь обеспечивает формирование сигналов 5 сброса в различных режимах работы и от питающих напряж ний различных номинальных значений.

Технико-экономическое преимущество предлагаемого формирователя сигналов сброса в запоминающих устройствах по сравнению с известным заключается в том, что оно позволяет производить автоматическую установку устройств в исходное состояние в момент включения источника питания независимо от номинального значения питающего напряжения, а также обеспечивать различные отладочные режимы запоминающего устройства и режим хранения информации в ОЗУ при сравнительно малых затратах оборудования . .

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Устройство для сохранения информации в полупроводниковой памяти при аварийном отключении питания | 1988 |

|

SU1599901A1 |

| Формирователь биполярных импульсов | 1989 |

|

SU1662003A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Устройство контроля технологического процесса сельскохозяйственного агрегата | 1991 |

|

SU1782393A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU746740A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1991 |

|

RU2023310C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Канал связи для одновременной передачи напряжения питания, синхроимпульсов и информации | 1987 |

|

SU1529233A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

.ФОРМИРОВАТЕЛЬ СИГНАЛОВ СБРОСА ДЛЯ БЛОКОВ ПАМЯТИ, содержащий ограничительные и накопительные элементы, причем первый вывод первого ограничительного элемента соединен с первой шиной питания, а второй: вывод - с первым выводом первого накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, первый вывод второго ограничительного элемента соединен с второй шиной питания, а второй 1ЧЫВОД - с первым выводом второго накопительного элемента, второй вывод которого соединен с шиной нулевого потенциала, о т л и. ч а ю щ и йс я тем, что, с целью расширения области применения формирователя за счет обеспечения формирования сигналов сброса в различных режимах работы блоков памяти и при различных напряжениях питания, в него введены третий, четвертый и пятый ограничительные элементы, элементы НЕ, элементы НЕРАВНОЗНАЧНОСТЬ и элементы И-НЕ, причем вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с выходом первого элемента НЕ, вход которого соединен с вторьм выводом первого ограничительного элемента и первым выводом третьего ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, второй вход элемента НЕРАВНОЗНАЧНОСТЬ и первьш вывод пятого ограничительного элемента являются первым входом формирователя, второй вывод пятого (Л ограничительного элемента соединен с третьей шиной питания, выход элес мента НЕРАВНОЗНАЧНОСТЬ и первый вход элемента И-НЕ являются первым выходом устройства, второй вход элемента И-НЕ является вторым входом устройства, а третий вход соединен с вторым выводом второго ограничиЭ6 тельного элемента и первым выводом :л четвертого ограничительного элемента, второй вывод которого соединен с шиной нулевого потенциала, выход элемента- И-НЕ и . вход второго элемента НЕ являются вторым выходом устройства третьим выходом которого является выход второго элемента НЕ.

т

15

V

9 fO

Т

16

20

т

%

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Блок управления запоминающим устройством | 1979 |

|

SU773722A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Радио, 1980, 1, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1984-08-15—Публикация

1983-05-26—Подача