54) БЛОК ДЛЯ УПРАВЛЕНИЯ ЗАПОМИНАЮЩИМ

t

Изобретение относится к запоминающим устройствам и может быть испсльзовано в любых устройствах вычислительной техники, где требуется автоматическая установка триггеров в исходное состояние в момент включения.

Известен блок для управления запоминанядим устройством, который состоит из элемента задержки и триггера обращения, установочный вход которого соединен с шиной обращения, а сбросовый вход соединен с отводом элемента задержки {l .

Недостатком этого блока является необходимость автоматической установки триггера обращения в исходное состояние после включения питания, что требует дополнительного оборудования.

Наиболее близким по технической сущности к предлагаемому изобретению является блок, состоящий из элемента задержки, и триггера полуцикла, установочный вход которого соединен через элемент И с выходом элемента задержки и шиной строба записи, а сбросовый вход соединен с нулевым выходом триггера запроса 2. УСТРОЙСТВОМ

Недостатком этого блока также является необходимость автоматической установки триггеров запроса и полуцикла в исходное состояние после включения питания, что требует затрат оборудования и, следовательно, усложняет блок.

Цель изобретения - упрощение блока. -.

ТО

Поставленная цель достигается тем, что в блок для управления запоминающим устройством, содер;:;ащий элемент задержки, триггеры, блок питания, шину нулевого потенциала, 15 причем входы установ:си и сброса

триггеров подключены к выходам элемента задержки, введен разделительный элемент, причем информационные входы триггеров подключены к шине нулевого потенциала, а входы синхро20низации триггеров соединены через разделительный элемент с выходом источника питания. При этом разделительный . элемент целесообразно

25 выполнить в виде резистора.

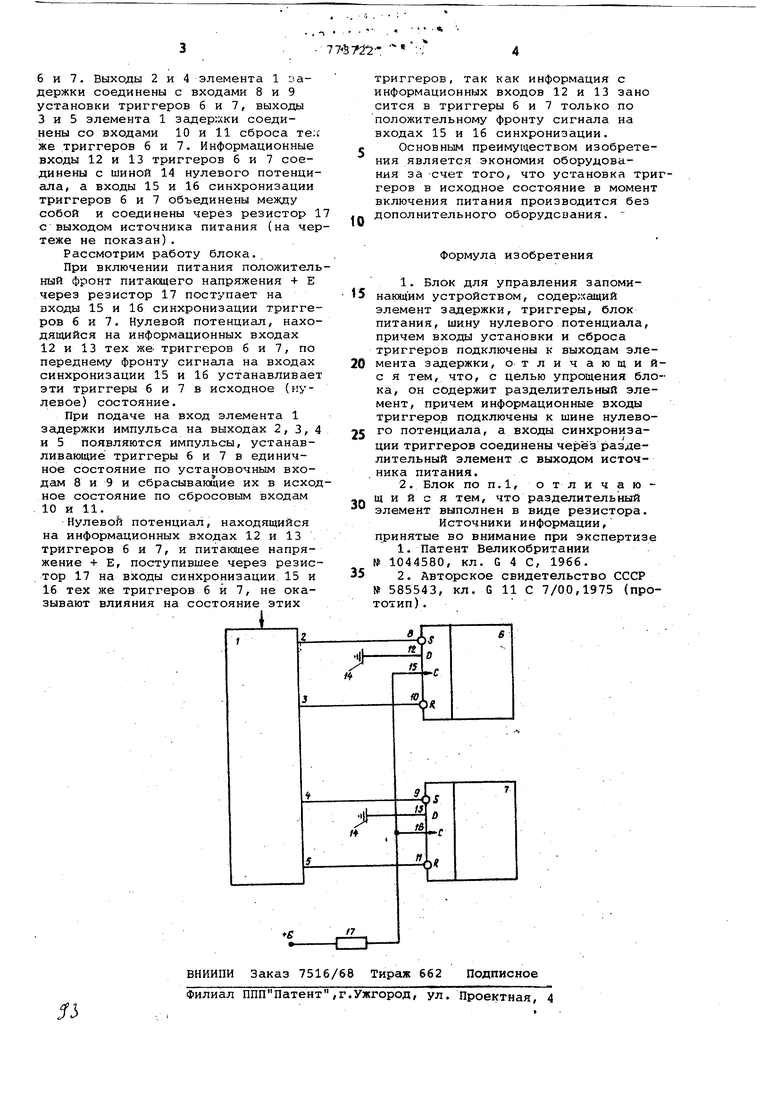

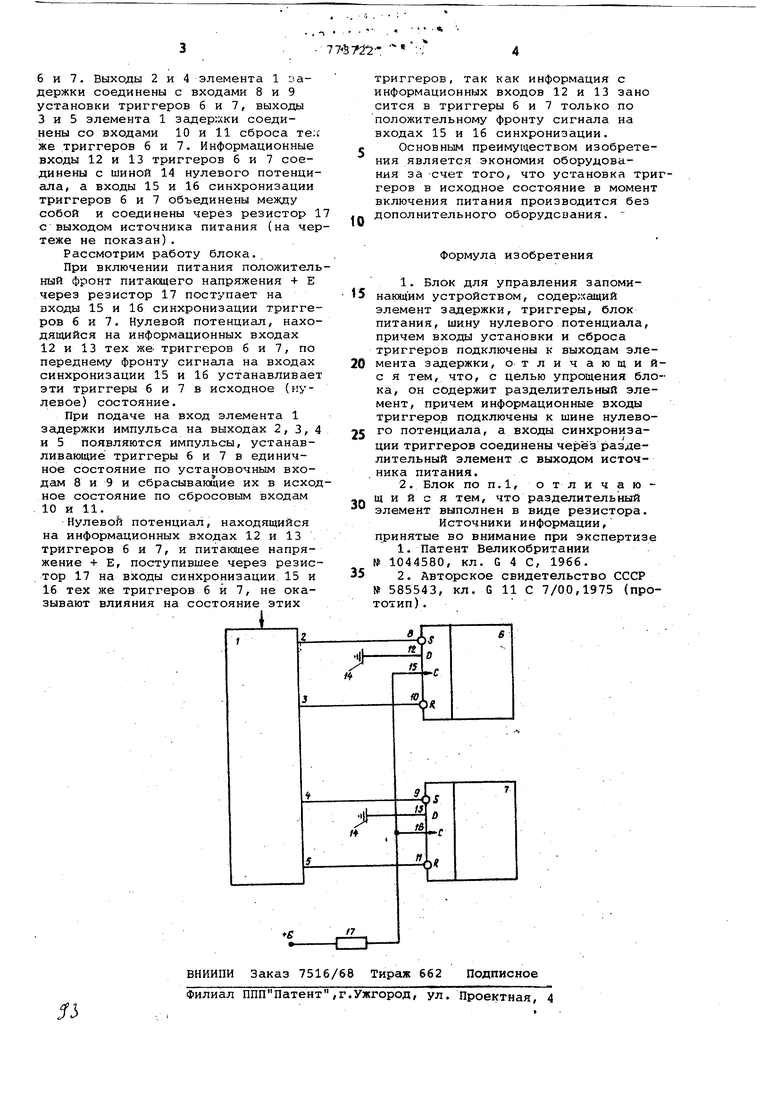

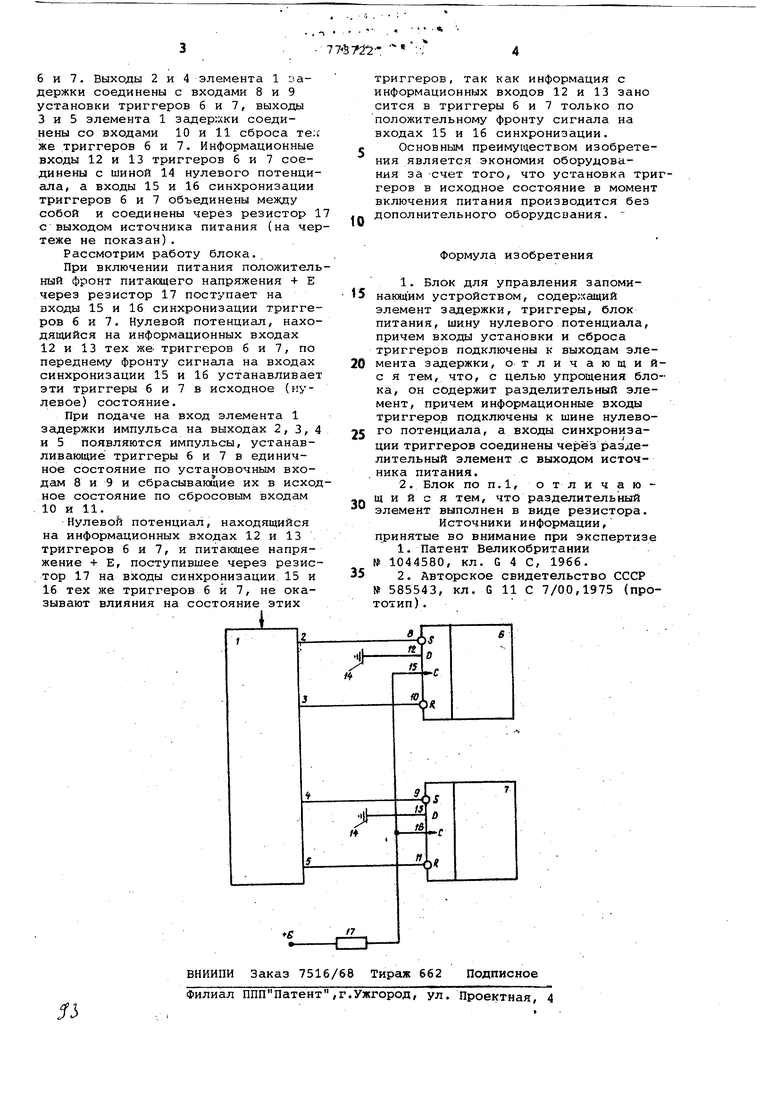

На чертеже представлена структурная схема блока для управления запоминающим устройством.

Блок содержит элемент 1 задержки с выходами 2, 3, 4 и 5, триггеры

30

yz 6 и 7. Выходы 2 и 4 элемента 1 задержки соединены с входами 8 и 9 установки триггеров б и 7, выходы 3 и 5 элемента 1 задер;хки соединены со входами 10 и 11 сброса те; же триггеров 6 и 7. Информационные входы 12 и 13 триггеров б и 7 соединены с шиной 14 нулевого потенци ала, а входы 15 и 16 синхронизации триггеров 6 и 7 объединены между собой и соединены через резистор с выходом источника питания (на че теже не показан). Рассмотрим работу блока. При включении питания положител ный фронт питающего напряжения + Е через резистор 17 поступает на входы 15 и 16 синхронизации тригге ров 6 и 7. Нулевой потенциал, нахо дящийся на информационных входах 12 и 13 тех же триггеров 6 и 7, по переднему фронту сигнала на входах синхронизации 15 и 16 устанавливае эти триггеры б и 7 в исходное (нулевое) состояние. При подаче на вход элемента 1 задержки импульса на выходах 2, 3, и 5 появляются импульсы, устанавливающие триггеры 6 и 7 в единичное состояние по установочным входам 8 и 9 и сбрасывающие их в исхо ное состояние по сбросовым входам . 10 и 11. Нулевой потенциал, находящийся на информационных входах 12 и 13 триггеров б и 7, и питакдцее напряжение + Е, поступившее через резис тор 17 на входы синхронизации 15 и 16 тех же триггеров б и 7, не оказывают влияния на состояние этих триггеров, так как информация с информационных входов 12 и 13 зано сится в триггеры б и 7 только по положительному фронту сигнала на входах 15 и 16 синхронизации. Основным преимуществом изобретения является экономия оборудования за счет того, что установка триггеров в исходное состояние в момент включения питания производится без дополнительного оборудсыания. Формула изобретения 1.Блок для управления запоминакадим устройством, содержащий элемент задержки, триггеры, блок питания, шину нулевого потенциала, причем входы установки и сброса триггеров подключены к выходам элемента задержки, отличающийс я тем, что, с целью упрощения блока, он содержит разделительный элемент, причем информационные входы триггеров подключены к шине нулевого потенциала, а входы синхронизации триггеров соединены через разделительный элемент .с выходом источника питания. 2.Блок ПОП.1, отличающийся тем, что разделительный элемент выполнен в виде резистора. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1044580, кл. G 4 С, 1966. 2.Авторское свидетельство СССР № 585543, кл. G 11 С 7/00,1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для формирования серий импульсов | 1991 |

|

SU1803965A1 |

| Устройство для акустического каротажа скважин | 1982 |

|

SU1040447A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-06—Подача