Изобретение относится к области электроники и микропроцессорной техники и может найти обширное применение при отладке, ремонте и эксплуатации широкого спектра микропроцессорных систем и устройств, как уже существующих, так и вновь разрабатываемых, а также при изучении и исследовании принципов работы подобных систем и устройств в практических разделах дисциплин учебных заведений, имеющих соответствующую направленность подготовки специалистов.

Целью изобретения является повышение производительности и снижение трудоемкости процесса отладки цифровых микропроцессорных систем (МПС) и устройств, а также снижение материальных затрат на этот процесс при сохранении многофункциональности отладочного устройства за счет использования уже имеющегося компьютерного оборудования и программного обеспечения в специфических операциях и процедурах, характерных для отладки.

К области применения изобретения относятся цифровые МПС шинной организации, представляющие собой в общем случае функционально законченные изделия, предназначенные для получения, обработки, передачи, преобразования информации, а также задач управления, состоящие из нескольких микросхем, в состав которых обычно входит микропроцессор (МП), оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ) и устройства ввода-вывода (УВВ) – интерфейсы сопряжения МПС с блоками ввода и вывода информации.

Спецификой МПС шинной организации является такое её построение, при котором основные составляющие системы взаимодействуют между собой посредством трех шин: адреса, данных и управления. Вследствие чего минимальный объем информации, которой микропроцессор может обмениваться с запоминающим устройством (ЗУ) и УВВ ограничивается размером его шины данных в битах (8, 16, 32, 64 бит), а максимальный объём памяти (количество ячеек ЗУ), к которой микропроцессор может обратиться непосредственно, определяется размером его адресной шины. Обращение микропроцессора к памяти для операции чтения сопровождается сигналом низкого уровня — /RD (ReaD) по шине управления, во время которого данные с выходов ЗУ на шине данных должны быть истинными, а запись в память сопровождается сигналом низкого уровня — /WR (WRite), по которому данные фиксируются запоминающим устройством. (Здесь и далее символом "/" обозначен низкий активный уровень сигнала.) В том случае, когда микропроцессор допускает разделение пространств памяти и УВВ, сигналы /WR и /RD с помощью простой схемы разделяют на две пары: /MEMWR, /MEMRD — сигналы обращения к ЗУ и /IOWR, /IORD — сигналы обращения к УВВ.

В том случае, когда микросхемы ЗУ или УВВ обладают меньшим быстродействием, чем сам микропроцессор, при обращении к ним в процедурах записи или чтения специальная схема вырабатывает активный сигнал, который по шине управления подается на вход микропроцессора /RDY (READY — готовность, иногда этот сигнал обозначают также WAIT — ожидание), в результате чего микропроцессор приостанавливает свою работу, удерживая активные сигналы на шинах и выполняя внутренние такты ожидания до тех пор, пока этот сигнал не будет деактивирован, что позволяет согласовать работу микропроцессора с любыми устройствами более низкого быстродействия.

Для разделения пространства памяти на области ПЗУ и ОЗУ в таких МПС обычно применяют дешифратор адресного пространства, подключаемый к старшим разрядам адресной шины и активирующий отдельные микросхемы ПЗУ и ОЗУ сигналами /CS0…/CSn (CS — Cheap Select — выбор микросхемы).

ПЗУ обычно занимает часть памяти МПС, физически выполняется на основе микросхем энергонезависимого ЗУ, содержит управляющую служебную, тест–мониторную программу или базовую систему ввода–вывода и располагается в диапазоне адресов пространства памяти, откуда микропроцессор начинает свою работу после начального пуска системы или по включению питания.

Одной из распространенных проблем, возникающих при разработке аппаратуры на основе микропроцессоров, является отладка записываемой в ПЗУ программы. Обычно для этой цели используют так называемые репрограммируемые ПЗУ (РПЗУ) со стиранием информации ультрафиолетовым облучением. Поскольку любое изменение программы приводит к необходимости стирать РПЗУ и заново записывать в него информацию, отладка отнимает много времени, так как процесс стирания довольно длителен. К тому же уже после 10—25 циклов записи и стирания надежность хранения данных в РПЗУ уменьшается. Таким образом, нудный и длительный механический процесс перезаписи, снижает производительность и повышает трудоемкость отладки, не говоря уже о финансовой стороне вопроса: РПЗУ при большом количестве циклов перезаписи могут выйти из строя, а микросхемы памяти с ультрафиолетовым стиранием недешевы.

Существуют инструментальные средства, ускоряющие процесс разработки системного программного обеспечения и отладки для МПС: эмуляторы ПЗУ, встроенные мониторы–отладчики и наиболее удобное средство — внутрисхемные эмуляторы (ВЭ).

Для профессиональных разработчиков внутрисхемный эмулятор является основным отладочным средством, которое позволяет быстро и качественно провести отладку микропроцессорной системы, но стоимость этих устройств может в ряде случаев превышать стоимость партии отлаживаемых изделий в мелкосерийном производстве, а с учетом того, что ВЭ представляют собой устройства жестко ориентированные на конкретный тип микропроцессоров, их применение в условиях средних и мелких фирм, ремонтных предприятий, а также учебного процесса становится экономически нерентабельным.

В этой связи представляет интерес использование в процессе отладки бюджетных отладочных устройств, которые, тем не менее, при наличии развитой функциональности, вполне способны повысить производительность и снизить трудоемкость процесса отладки микропроцессорных систем без значительных материальных затрат.

Известен ‘Имитатор ПЗУ’ (Радиолюбитель № 5, 1997 с.18-19), включающий в свой состав статическое ОЗУ соответствующей ёмкости с опцией сохранения записанной информации при пониженном напряжении питания в режиме микропотребления, регистры для фиксации адреса запрашиваемого байта, буферный шинный формирователь, осуществляющий согласование выходов микросхемы ОЗУ с шиной данных микропроцессорной системы, низковольтный элемент питания с безынерционным переключателем и схему управления с узлом контроля напряжения питания, в функции которой входит слежение за величиной питающего напряжения устройства и корректное отключение микросхемы ОЗУ от шин адреса, данных и управления отлаживаемой микропроцессорной системы в случае снижения питающего напряжения с переводом БИС ОЗУ в режим хранения с питанием от автономного низковольтного гальванического элемента.

С точки зрения отлаживаемой микропроцессорной системы такое устройство полностью имитирует функции замещаемого им ПЗУ, может быть запрограммировано имеющимися аппаратными средствами (программатором), а упрощение процесса отладки, повышение его производительности и снижение трудоёмкости при использовании подобного устройства происходит за счет исключения длительной по времени процедуры стирания микросхем ПЗУ ультрафиолетовым излучением, поскольку микросхема статического ОЗУ в любой момент готова к перезаписи сохраняемой ею информации.

Недостатком подобного решения является то, что, несмотря на исключение из процесса отладки процедуры стирания микросхем ПЗУ, остаётся необходимость извлечения устройства из контактной панели ПЗУ отлаживаемой микропроцессорной системы, размещения его в программаторе, программирования посредством внешней ЭВМ и последующей установки в контактную панель эмулируемого ПЗУ. Трудоёмкость процесса и стоимость устройства многократно возрастают в случае отладки микропроцессорной системы с большей разрядностью шины данных микропроцессора (16, 32, 64 бита). В этом случае сложность и себестоимость устройства (или совокупности устройств) отладки может быть сравнима со сложностью и себестоимостью самой отлаживаемой системы. Так для 32-разрядной системы потребуется уже 4 микросхемы статического ОЗУ, 8 адресных регистров, 4 шинных формирователя, пропорционально увеличится и число остальных элементов, а сама процедура программирования устройств и их установки в контактные панели ПЗУ отлаживаемой микропроцессорной системы существенно усложнится.

Недостатком является также то, что, будучи установленным в отлаживаемую микропроцессорную систему, имитатор ПЗУ никаких дополнительных функций отладки, как, например, пошаговое прохождение программы с остановом в контрольных точках, не обеспечивает.

Известен ‘Эмулятор ПЗУ’ (Радио № 6, 2000, с.27-29). Устройство использует часть памяти внешней управляющей ЭВМ (или, иначе говоря, инструментального компьютера) для хранения программы для целевой системы, а порт принтера (LPT–порт) инструментального компьютера выполняет здесь функцию интерфейса связи с отлаживаемой системой (её обычно принято называть целевой). Эмулятор ПЗУ состоит из следующих функциональных блоков: тактового генератора, синхронизатора тактовых импульсов, устройства запуска, счетчика импульсов, формирователя импульсов записи блоков адреса, регистра данных и мультиплексора адреса. Он соединяется многоштырьковой вилкой с панелькой ПЗУ целевого отлаживаемого устройства, через которую эмулятор получает доступ к шине данных и шине адреса целевой системы, а также к сигналам выбора ПЗУ — /CS (Cheap Select) и разрешения выходных данных ПЗУ — /OE (Output Enable).

С приходом от целевого микропроцессорного устройства низкого уровня сигнала /CS на вход устройства запуска, оно своим активным выходным уровнем разрешает прохождение сигналов тактового генератора на двоичный счетчик, имеющий коэффициент пересчета 5. Поскольку LPT–порт инструментального компьютера сильно асимметричен, и имеет 12 выходных и всего пять входных линий, в схеме эмулятор ПЗУ приходится мультиплексировать принимаемый инструментальным компьютером 16-разрядный адрес байта эмулируемого ПЗУ, поэтому выходы двоичного счетчика через формирователь импульсов записи блоков адреса управляют мультиплексором адреса, который за четыре импульса тактового генератора передает в инструментальный компьютер весь 16-разрядный адрес блоками по 4 бита через 4 входных линии LPT–порта. По пятой входной линии инструментальный компьютер получает информацию о подсчете двоичным счетчиком эмулятора тактовых импульсов посредство специального сигнала, создаваемого формирователем импульсов. В момент прихода пятого сигнала инструментальный компьютер через 8 разрядов данных LPT–порта выдает из своей внутренней памяти байт, соответствующий принятому ранее адресу, на входы регистра данных эмулятора.

После прихода от целевого микропроцессорного устройства сигнала /CS низкого уровня, согласно логике работы, поступает и сигнал /OE разрешения выходных данных ПЗУ, который поступает на вход синхронизатора тактовых импульсов и на одноименный вход регистра данных, после чего на выходах последнего появляются логические уровни отдельных битов байта данных, выданные инструментальным компьютером на линии данных LPT–порта. Эти данные считываются микропроцессором целевой системы, и процесс получения байта данных от целевой ЭВМ завершается снятием активных уровней сигналов /CS и /OE.

Понятно, что в силу особенностей приема инструментальным компьютером 16-разрядного адреса байта четырьмя блоками и управления им выдачей байта данных через LPT–порт программным способом, эмулятор ПЗУ не может работать с той же скоростью, с какой целевое микропроцессорное устройство запрашивает байты, поэтому в составе устройства имеется синхронизатор тактовых импульсов, в задачу которого входит перевод микропроцессора целевой системы в режим ожидания по входу /READY своим выходным сигналом, сформированным по поступлению от микропроцессора активного уровня сигнала /OE (сигнал /RD, выдаваемый микропроцессором). По завершению двоичным счетчиком эмулятора ПЗУ процесса подсчета 5 импульсов тактового генератора синхронизатор тактовых импульсов снимает со входа /READY микропроцессора целевой системы активный уровень сигнал, микропроцессор выходит из режима ожидания и продолжает свою работу на полной скорости.

Таким образом, принцип работы эмулятора ПЗУ заключается в следующем: по активному уровню сигнала /CS, поступившему от целевой микропроцессорной системы, эмулятор начинает передавать в инструментальный компьютер через LPT–порт адрес запрашиваемого целевой системой байта. По поступлению от микропроцессора активного уровня сигнала /OE эмулятор ПЗУ через синхронизатор тактовых импульсов приостанавливает микропроцессор целевой системы до тех пор, пока инструментальный компьютер не получит полностью адрес запрашиваемого целевой системой байта и не выдаст этот байт через LPT–порт на входы регистра данных эмулятора, после чего микропроцессору целевой системы разрешается считать запрашиваемый байт и продолжить свою работу.

Существенным недостатком такого решения является неспособность устройства выполнять свои функции уже при необходимости обслуживания целевой микропроцессорной системы даже с 16-разрядным микропроцессором, не говоря уже о системах с более высокой разрядностью. То есть, несмотря на свою относительную сложность, устройство не обладает универсальностью в плане практического применения, поскольку при работе всего лишь с 16-разрядным микропроцессором таких устройств необходимо два, а наличие двух LPT–портов у современных компьютеров явление достаточно редкое, не говоря уже о том, что этот интерфейс может отсутствовать совсем, поскольку он, как устаревший, был практически вытеснен современным компактным и высокопроизводительным интерфейсом USB. Для обслуживания же целевой системы с 32-разрядным микропроцессором этот эмулятор ПЗУ в оригинальном виде практически неприменим, поскольку для его функционирования потребуется уже четыре независимых LPT–порта.

Недостатком устройства является также и то, что в протоколе обмена с инструментальным компьютером через LPT–порт управляющие линии порта не задействованы. То есть, весь протокол обмена рассчитан на то, что инструментальный компьютер при подобранной частоте тактового генератора эмулятора ПЗУ должен успевать программно принять четыре полубайта адреса и выдать соответствующий байт в LPT–порт. Такое решение помимо того, что само по себе является недостаточно надежным, поскольку инструментальный компьютер и целевая отлаживаемая система являются асинхронными друг относительно друга, и в этом случае обмен между ними предпочтительно вести по принципу "рукопожатия" ("handshake"), сопровождая передаваемые адреса и возвращаемые данные сигналами квитирования, но и обладает существенным недостатком, состоящем в том, что инструментальный компьютер практически лишен возможности оперативно влиять на процесс исполнения программы эмулируемого ПЗУ, поскольку он не использует сигнал подтверждения истинности выданных им в LPT–порт данных. То есть, в устройстве отсутствует возможность отладки даже в таких ограниченных вариантах, как пошаговое прохождение и останов в контрольных точках.

Недостаткам устройства является и используемое в процессе его работы побитное программное управление LPT–портом инструментального компьютера специальной программой. Кроме того, что такая программа в силу рассмотренных уже выше конструктивных особенностей эмулятора должна работать под управлением операционной системы (ОС) реального времени (в авторском варианте это MS DOS), так и выбранный протокол обмена с эмулятором является совершенно уникальным, что требует написания собственного программного обеспечения и драйверов, и серьезно затрудняет применение эмулятора ПЗУ с современными многозадачными операционными системам, как, например, распространенная ныне ОС MS Windows.

Отметим так же, как недостаток, тот факт, что уникальный протокол обмена с LPT–портом не позволит использовать с данным эмулятором ПЗУ современный высокопроизводительный интерфейс USB через специальные кабели-переходники USB–LPT, имеющие в своем составе специальный микроконтроллер, осуществляющий преобразование интерфейса. Побитного управления LPT–портом, подобные адаптеры, к сожалению, не допускают, а поддерживают лишь характерный для LPT–порта протокол обмена с принтером по стандарту ‘Centronics’, который предполагает строго определенную последовательность подачи сигналов на внешнее печатающее устройство и опрос сигналов его готовности.

Наиболее близким по технической сущности к заявляемому изобретению, принятым за прототип, является ‘Система без ПЗУ, загружаемая через порт принтера’ (Sistema senza ROM. Caricabile dalla porta stampante. http://stor.altervista.org/z80/ schema_2.htm). В этой конструкции было найдено элегантное, хотя и несколько необычное решение: для частичной эмуляции функций физически отсутствующего в системе ПЗУ, с целью начальной загрузки в ОЗУ целевой системы исполняемой программы, также используется часть памяти внешнего инструментального компьютера, из которой под управлением специальной программы-загрузчика в ОЗУ целевой системы без ПЗУ через LPT–порт инструментального компьютера выдаются коды команд, которые немедленно исполняются микропроцессором целевой системы. С этой целью в систему без ПЗУ, загружаемую через порт принтера, введен механический переключатель, который перенаправляет сигнал чтения микропроцессором ОЗУ низкого уровня — /RD — на вход разрешения сигнала выходных линий — /OE (Output Enable) — тристабильного восьмиразрядного буферного шинного формирователя, подключающего выходные линии данных LPT–порта к шине данных целевой системы. Поскольку программно-управляемый порт принтера инструментальной ЭВМ физически не способен выдавать коды команд с той скоростью, с которой их может исполнять микропроцессор целевой системы, в систему без ПЗУ также введено простейшее устройство синхронизации, представляющее собой бистабильный RS-триггер, на один из входов которого через формирователь короткого импульса поступает сигнал чтения /RD, а на второй вход, также через формирователь короткого импульса — сигнал стробирования данных портом принтера /STROBE. Выход RS-триггера через вторую пару контактов механического переключателя соединяется со входом /WAIT микропроцессора целевой системы. Таким образом, при выполнении им операции чтения из ОЗУ, происходит чтение кода с выходов LPT–порта инструментального компьютера, а при выполнении операции записи — происходит запись байта непосредственно в ОЗУ самой целевой системы, при этом устройство синхронизации приостанавливает микропроцессор целевой системы активным уровнем сигнала по входу /WAIT в операции чтения, и в этот момент активный сигнал /RD низкого уровня позволяет поступить на шину данных сигналам данных с выходов LPT–порта, а программа-загрузчик, опрашивающая выход RS-триггера через линию BUSY этого порта, определяет состояние чтения из LPT–порта и выдаёт на линии данных LPT–порта очередной код загружаемой программы, сопровождая его сигналом стробирования данных принтера /STROBE. Этот сигнал через формирователь короткого импульса сбрасывает RS-триггер устройства синхронизации, который своим выходом деактивирует сигнал на входе /WAIT микропроцессора, после чего последний считывает поступивший на шину данных код и исполняет его. При следующем обращении микропроцессора к ОЗУ операцией чтения весь описанный выше процесс повторяется. Согласно этому алгоритму, микропроцессору после сброса обычно передают короткую программу начального циклического загрузчика, которая в дальнейшем считывает байты кодов из LPT–порта и записывает их в ОЗУ. По завершению процесса передачи кодов загружаемой программы в ОЗУ целевой системы следует нажать кнопку начального сброса микропроцессора, и, удерживая её, осуществить переключение механического переключателя, осуществляющее отключение выхода RS-триггера от входа /WAIT микропроцессора и подключение его выхода /RD к соответствующему входу микросхемы ОЗУ. После отпускания кнопки начального сброса микропроцессора, он по сигналу чтения низкого уровня /RD считывает первый код операции уже из собственного ОЗУ и начинает выполнять загруженную в ОЗУ программу.

Таким образом, существует возможность оперативно и довольно просто загружать в ОЗУ микропроцессорной системы без ПЗУ отлаживаемые программы, которые могут быть в дальнейшем размещены в системном ПЗУ после их тестирования и выявления ошибок, причем само устройство загрузки, частично имитирующее функции ПЗУ, отличается простотой схемотехнического решения и низкой себестоимостью.

Основным недостатком конструкции, выбранной в качестве прототипа, несмотря на явную простоту и оригинальность, является её ненадежность и неудобство, связанные с относительно сложным процессом изменения режима целевого устройства с загрузки программы на её исполнение с помощью механического переключателя при удержании микропроцессора отдельной кнопкой в состоянии начального сброса. Некорректное выполнение такого переключения может привести к сбою исполнения загруженного кода, потере управления микропроцесором и разрушению программы в ОЗУ. Подобное решение также не может быть применимо к законченной отлаживаемой конструкции, поскольку потребует вмешательства в её схемотехнику, связанного с необходимостью коммутации сигнала /RD шины управления.

Другим существенным недостатком является то, что устройство неспособно выполнять свои функции уже при необходимости обслуживания микропроцессорной системы даже с 16-разрядным микропроцессором, не говоря уже о системах более высокой разрядности.

И, наконец, к недостаткам устройства следует отнести используемое в процессе его работы побитное программное управление LPT–портом инструментального компьютера программой-загрузчиком. Этот весьма существенный недостаток заключается в том, что LPT–порт является устаревшим интерфейсом персональных ЭВМ, и в современных компьютерах, особенно в лэптопах и ноутбуках, столь удобных для использования в качестве инструментальных компьютеров, этот интерфейс отсутствует совсем, поскольку он был вытеснен современным компактным и высокопроизводительным интерфейсом USB. Для управления оборудованием, имеющим интерфейс, совместимый с LPT–портом, в настоящее время используются специальные кабели-переходники USB–LPT, имеющие в своем составе специальный микроконтроллер, осуществляющий преобразование интерфейса, но, к сожалению, подобные адаптеры не допускают побитное управление LPT–портом, а поддерживают лишь характерный для этого порта протокол обмена с принтером по стандарту ‘Centronics’, который предполагает строго определенную последовательность подачи сигналов на внешнее печатающее устройство и опрос сигналов его готовности, что в данном простом устройстве аппаратно не соблюдается.

Следует также отметить, что возможности отладки программы данным устройством практически ограничены. Если сам процесс загрузки еще можно рассматривать как разновидность пошагового прохождения программы с возможностью останова, то после загрузки программы в ОЗУ и механического отключения устройства во время начального сброса целевой системы, возможность инструментального компьютера как-то влиять в дальнейшем на процесс выполнения загруженной программы в ОЗУ целевой системы практически отсутствует.

Задачей заявляемого технического решения является создание конструкции отладочного устройства для широкого круга целевых микропроцессорных систем, обладающего функциями отладчика, загрузчика программ и эмулятора ПЗУ, при сохранении схемотехнической простоты и бюджетной доступности устройства.

Технический результат заключается в повышении производительности и снижении трудоемкости процесса отладки микропроцессорных систем и устройств, а также снижении материальных затрат на этот процесс.

Указанный технический результат достигается тем, что в конструкцию отладочного устройства, использующего часть памяти внешнего инструментального компьютера для хранения программы целевой отлаживаемой микропроцессорной системы, и имеющего в своем составе интерфейс LPT–порта принтера для передачи программ и данных в отлаживаемую микропроцессорную систему через тристабильный восьмиразрядный буферный шинный формирователь, а также простейшее устройство синхронизации, представляющее собой бистабильный RS-триггер с подключенными к его входам формирователями коротких импульсов, согласно решению, в зависимости от разрядности N микропроцессора отлаживаемой системы, вводятся дополнительно N/8 восьмиразрядных регистров-защелок с тристабильным выходом, входы которых объединяются поразрядно и подключаются через тристабильный восьмиразрядный буферный шинный формирователь соответственно к линиям данных интерфейса принтера, а выходы посредством многоштырьковых вилок соединяются через панельки ПЗУ отлаживаемого устройства с его шиной данных.

Со входами записи восьмиразрядных регистров-защелок соединены выходы введенного в устройство дешифратора типа “код-позиция”, к входным линиям которого подключены выходы двоичного счетчика, на счетный вход которого через буферный элемент в необходимой полярности поступает сигнал подтверждения истинности выданных инструментальным компьютером в LPT–порт данных — /STROBE, в нужной полярности подаваемый через буферный элемент также на входы разрешения работы дешифратора. Двоичный счетчик и дешифратор в таком включении образуют демультиплексор–распределитель сигнала /STROBE, направляющий каждый следующий сигнал подтверждения истинности выданных инструментальным компьютером данных на вход записи соответствующего регистра-защелки.

В зависимости от разрядности микропроцессора отлаживаемой целевой системы к одному из выходов демультиплексора–распределителя сигнала /STROBE (нулевому, первому, третьему или седьмому) через соответствующий переключатель подсоединен формирователь короткого импульса, выходной сигнал которого поступает через вентиль, выполняющий логическую функцию ИЛИ, на вход сброса RS-триггера устройства синхронизации, а также — на входы сброса двоичного счетчика, что позволяет осуществлять подсчет количества байт, необходимых конкретному типу процессора за одно обращение к ПЗУ.

Через второй вход этого вентиля на вход сброса двоичного счетчика подается сигнал начальной установки /INIT с вывода LPT–порт инструментального компьютера, а через третий вход — сигнал начальной установки по включению питания, формируемый интегрирующей RC-цепью, что инициализирует двоичный счетчик начальным нулевым значением, а также устанавливает по входу сброса в исходное состояние RS-триггер устройства синхронизации.

На вход установки RS-триггера устройства синхронизации через формирователь короткого импульса, подключенный к выходу двухвходовой схемы совпадения, выполняющей логическую функцию "И", с панельки ПЗУ отлаживаемого устройства через контакты многоштырьковой вилки поступают сигналы выборки ПЗУ и строба чтения ЗУ отлаживаемой микропроцессорной системы, таким образом, что выходной сигнал схемы совпадения активен, когда активны оба сигнала. Этот выходной сигнал поступает на все входы разрешения выдачи данных восьмиразрядных регистров-защелок, позволяя им выдать записанные в них байты на шину данных отлаживаемого устройства.

С выхода RS-триггера устройства синхронизации сигнал необходимой полярности через буферные элементы подается на вход готовности /READY микропроцессора целевой системы. К одному из выходов RS-триггера также подключается светодиодный индикатор, в задачу которого входит визуальное отображение фазы процесса загрузки или отладки, а также индикация включения и начальной инициализации отладочного устройства.

Со счетным входом двоичного счетчика, на который в необходимой полярности через буферный элемент поступает сигнал подтверждения истинности выданных инструментальным компьютером в LPT–порт данных — /STROBE, соединен вход схемы задержки импульса, на выходе которой логическим вентилем формируется сигнал занятости устройства BUSY, поступающий на вход LPT–порта. С выхода схемы задержки импульса через подсоединенную к нему дополнительную схему задержки и формирователь импульса на соответствующий вход LPT–порта подается сформированный таким образом сигнал /ACK — подтверждения принятия данных и готовности устройства принять следующие данные.

Таким образом, при выдаче инструментальным компьютером в LPT–порт байта данных и подтверждения его истинности сигналом /STROBE устройство отладки имитирует сигналы интерфейса обмена с принтером по стандарту ‘Centronics’, что позволяет использовать для обмена с ним стандартные низкоуровневые подпрограммы вывода байта на принтер, имеющиеся в большинстве распространенных операционных систем. С точки зрения же инструментального компьютера работа с устройством отладки программно и аппаратно выглядит как вывод последовательности байт на печать принтеру, поддерживающему стандартный интерфейс обмена, поэтому для работы с устройством подходит большинство программ, имеющих опцию печати бинарного файла. Для более сложных манипуляций с устройством вполне подойдут простые программы, содержащие операторы вывода байта на печать, опроса клавиатуры, работы с файлом и написанные на распространенных языках высокого уровня, поскольку всю низкоуровневую часть поддерживает непосредственно операционная система. При этом достигается максимальная скорость обмена через стандартный LPT–порт — до 100…200 Кбайт/с и более, поскольку само устройство отладки, в отличие от принтера, является чисто электронным прибором и потому не вносит в процедуру обмена задержек, характерных для принтера, имеющего механическую часть.

Заявляемое отладочное устройство подключается кабелем к разъему LPT–порта инструментального компьютера и шлейфами с многоштырьковыми вилками — ко входу готовности микропроцессора отлаживаемого устройства и его панелькам ПЗУ, через которые из отлаживаемой системы поступает также и питающее напряжение.

При включении питания отлаживаемой системы интегрирующая RC-цепь формирует сигнал начальной установки длительностью пропорциональной постоянной времени этой цепи. Этот сигнал инициализирует двоичный счетчик начальным нулевым значением и устанавливает RS-триггер устройства синхронизации по его второму входу в положение, при котором микропроцессор отлаживаемой системы остановлен активным уровнем сигнала по входу готовности, выполняя при этом такты ожидания, а на вход контроля занятости разъема LPT–порта инструментального компьютера подаётся логический уровень, сообщающий о том, что отладочное устройство не занято и готово принять байт данных отлаживаемой программы. Эта ситуация отображается горящим светодиодным индикатором, после чего на инструментальном компьютере запускается программа вывода на принтер (“печати”) бинарного файла отлаживаемой программы, при этом через LPT–порт выдается сигнал начальной инициализации принтера, в функции которого входит произвести все те предустановки, которые были сделаны сигналом начальной установки, формируемым интегрирующей RC-цепью при включении питания. Такую начальную инициализацию программа вывода на принтер осуществляет каждый раз при начале печати, приводя в исходное состояние двоичный счетчик и устройство синхронизации в том случае, если они остались в некорректном состоянии после предыдущего сеанса работы.

Программа вывода на принтер далее проверяет состояние линии занятости устройства, и в том случае, если устройство не занято, выводит на линии данных LPT–порта первый байт программы, сопровождая его, согласно стандартному протоколу обмена с принтером, сигналом стробирования — подтверждения истинности выданных в порт данных. Двоичный счетчик по сигналу начальной установки инициализирован нулевым значением, поэтому дешифратор, получив разрешение низким уровнем сигнала стробирования, распределяет этот сигнал на вход записи первого из восьмиразрядных регистров-защелок, в который и записывается байт с линий данных LPT–порта по спаду стробирующего сигнала.

В этот же момент из сигнала стробирования формируется сдвинутый по времени сигнал занятости отладочного устройства, который выдается на соответствующую линию порта принтера инструментального компьютера, чтобы программа печати не могла послать следующий байт, пока не закончены процессы в отладочном устройстве.

По заднему фронту сигнала стробирования двоичный счетчик подсчитывает этот сигнал, а дешифратор отключается от входов записи восьмиразрядных регистров-защелок. В этот момент сигнал занятости на соответствующей линий LPT–порта становится неактивным, сообщая инструментальному компьютеру, согласно стандартному протоколу обмена, что отладочное устройство не занято, а сформированный сигнал подтверждения принятия данных и готовности устройства принять следующие данные через соответствующую линию LPT–порта сигнализирует инструментальному компьютеру, что можно выдать в порт следующий байт отлаживаемой программы.

Программа печати снова проверяет состояние линии занятости устройства, и в том случае, если устройство не занято, выводит на линии данных LPT–порта следующий байт программы, опять сопровождая его, согласно стандартному протоколу обмена с принтером, сигналом стробирования. Весь процесс, изложенный выше, повторяется с той лишь разницей, что байт записывается во второй восьмиразрядный регистр-защелку. Далее вся процедура выдачи байта повторяется вновь и так происходит до тех пор, пока сигнал стробирования не будет подан на вход записи того регистра-защелки, к которому через переключатель подсоединен формирователь короткого импульса, сигнал с выхода которого подается на первый вход сброса RS-триггера устройства синхронизации и через вентиль, выполняющий логическую функцию "ИЛИ", — на входы сброса двоичного счетчика.

Положение переключателя зависит от разрядности микропроцессора отлаживаемой системы и устанавливается до начала процесса отладки. В зависимости от положения этого переключателя, байты отлаживаемой программы будут записаны через LPT–порт в один регистр-защелку — для 8-битного микропроцессора, в два регистра-защелки — для 16-битного микропроцессора, в четыре регистра-защелки — для 32-битного и в восемь регистров — для 64-битного прибора.

Как только сигнал стробирования появляется на входе формирователя короткого импульса, он формирует короткий импульс сброса, которым переводит двоичный счетчик в исходное состояние с нулевым значением на выходах, а RS-триггер устройства синхронизации сбрасывается в состояние, при котором на соответствующую линию LPT–порта выдается активный сигнал занятости, а сигнал готовности микропроцессора отлаживаемой системы деактивируется. Микропроцессор прекращает такты ожидания и, в зависимости от своей разрядности, считывает при активизированных им сигналах выбора и чтения ПЗУ соответственно 8, 16, 32 или 64 бита данных с выходов регистров-защелок, которые в этот момент активным сигналом чтения подключены к шине данных отлаживаемой системы.

Микропроцессор отлаживаемой системы выполняет полученный код в реальном масштабе времени и вновь обращается к отладочному устройству, как к ПЗУ сигналами выбора ПЗУ и чтения. В этот момент через формирователь короткого импульса происходит установка RS-триггера устройства синхронизации в состояние, при котором микропроцессор отлаживаемой системы останавливается активным уровнем сигнала по входу готовности, выполняя при этом такты ожидания, а на вход контроля занятости разъема LPT–порта инструментального компьютера подаётся логический уровень, сообщающий о том, что отладочное устройство не занято и готово принять байт данных отлаживаемой программы.

Инструментальный компьютер вновь “выдает на печать” через свой LPT–порт требуемое количество байт, отладочное устройство вновь разрешает микропроцессору отлаживаемой системы выполнить полученный код, приостановив инструментальный компьютер сигналом занятости. Таким образом весь процесс выполняется циклически до тех пор, пока не закончится файл исполняемого кода, или микропроцессор не получит код останова, или же произойдет нештатная ситуация в отлаживаемой системе и отладочное устройство потеряет управление микропроцессором.

Описанный процесс характерен для эмуляции отладочным устройством функций ПЗУ отлаживаемой системы. Таким же может быть алгоритм загрузки исполняемой программы в ОЗУ отлаживаемой микропроцессорной системы, когда микропроцессору отлаживаемой системы после сброса передаётся короткая программа начального циклического загрузчика, согласно которой он в дальнейшем считывает данные из регистров отладочного устройства и записывает их в ОЗУ. По завершению процесса передачи кодов загружаемой программы в ОЗУ целевой системы микропроцессору выдается команда условного перехода на начало загруженной в ОЗУ программы, и он начинает её исполнение в режиме реального времени. При этом заявляемое отладочное устройство может быть использовано для организации контрольных точек, поскольку любое обращение микропроцессора к нему, как к ПЗУ, вызывает переход микропроцессора в режим ожидания, а необходимые данные о состоянии могут быть выведены в младших разрядах адресной шины и протестированы любым простым логическим пробником, в том числе и многоканальным. Такие бюджетные логические анализаторы в настоящее время выполняются в виде внешних устройств, подключаемых к компьютеру через порты USB, они доступны по цене, и в связи с этим индикация состояния адресных шин не была реализована в заявляемом отладочном устройстве, хотя оно и способно удерживать микропроцессор отлаживаемой системы в режиме ожидания, когда выставленные на его шинах сигналы истинны и доступны для анализа.

Это свойство заявляемого отладочного устройства удобно для организации режима пошагового прохождения отлаживаемой программы, для реализации которого данные в отлаживаемую систему передаются короткими блоками, равными разрядности её микропроцессора, что позволяет проверить прохождение сигналов по шинам отлаживаемого устройства и корректность исполнения практически всего набора кодов, хотя и может потребовать составления довольно специфической последовательности машинного кода, учитывающего специфику обмена с отладочным устройством.

И, наконец, заявляемое отладочное устройство может исполнять для целевой системы функции устройства ввода, аналогичного, к примеру, клавиатуре или клавишному пульту, что имеет особую практическую ценность для вновь разрабатываемых устройств, отладка которых осуществляется на макетной плате, а их собственные аппаратные интерфейсные средства еще не реализованы на макете.

Действительно, поскольку любое обращение микропроцессора отлаживаемой системы к ней, как к собственному ПЗУ во всем его диапазоне адресов, вызывает переход микропроцессора в режим ожидания до того момента, пока инструментальный компьютер не “выдаст на печать” через свой LPT–порт необходимое количество байт данных. Такой режим можно рассматривать как ожидание кода с клавиатуры или клавишного пульта, и необходимый код может быть введен с клавиатуры инструментального компьютера и “выдан на печать”, что позволяет организовать в отлаживаемой программе условные ветвления, контролируемые разработчиком.

Таким образом, заявляемое отладочное устройство при схемотехнической простоте и невысокой стоимости способно выполнять функции эмулятора ПЗУ, загрузчика программ в ОЗУ целевой системы, отладчика с возможностью пошагового прохождения программы и останова в контрольных точках, а также простого устройства ввода, аналогичного клавиатуре, клавишной панели или набору датчиков, что, несомненно, позиционирует его как многофункциональное. В то же время способность к настройке на работу с конкретным типом процессора придает заявляемому устройству свойство универсальности.

Оно имеет ограничения, обусловленные простотой конструкции, и не способно предоставить весь спектр функции и удобств, присущих внутрисхемному эмулятору, но по соотношению цена/функциональность вполне может составить ему достойную конкуренцию в сфере малого бизнеса и профильных учебных заведений.

Заявляемое техническое решение отличается от прототипа наличием новых блоков — N/8 идентичных восьмиразрядных регистров-защелок с тристабильным выходом (где N — разрядность микропроцессора отлаживаемой системы), дешифратора типа “код-позиция”, формирователей сигналов занятости устройства и подтверждения принятия данных, логическими вентилями и формирователями сигналов управления устройства синхронизации, их связями с остальными элементами схемы. Эти отличия позволяют сделать вывод о соответствии заявляемого решения критерию "новизна".

Требуемый результат достигается всей вновь введенной совокупностью существенных признаков, которые в известной патентной и научной литературе не обнаружены на дату подачи заявки. Следовательно, техническое решение соответствует критерию "изобретательский уровень".

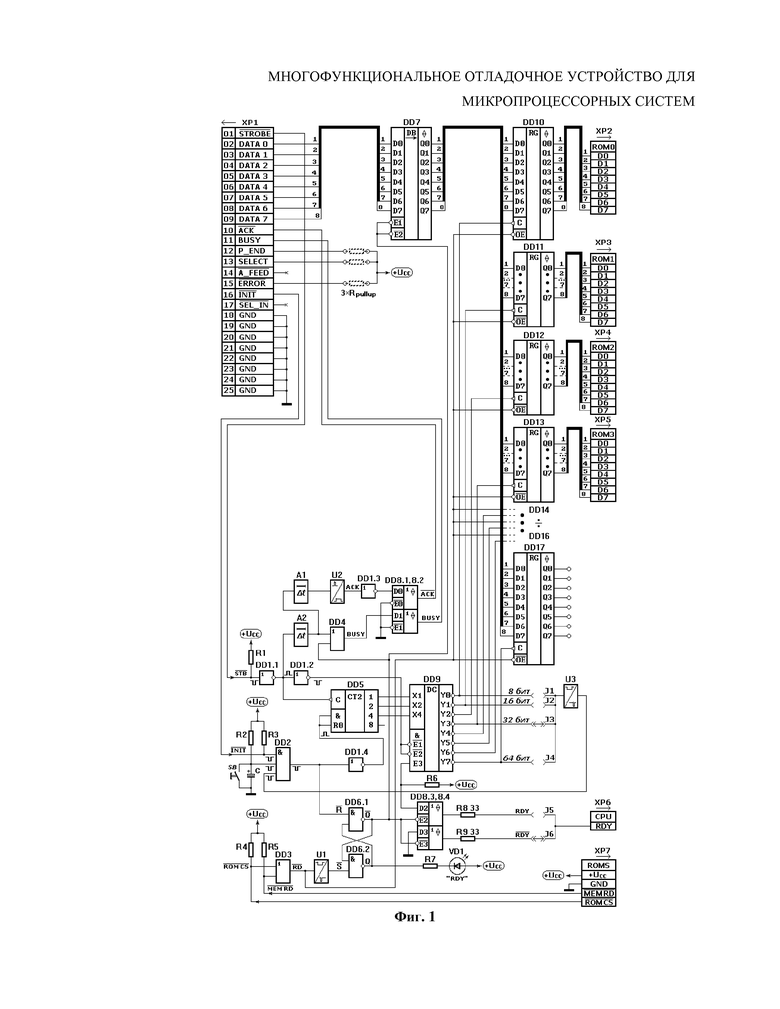

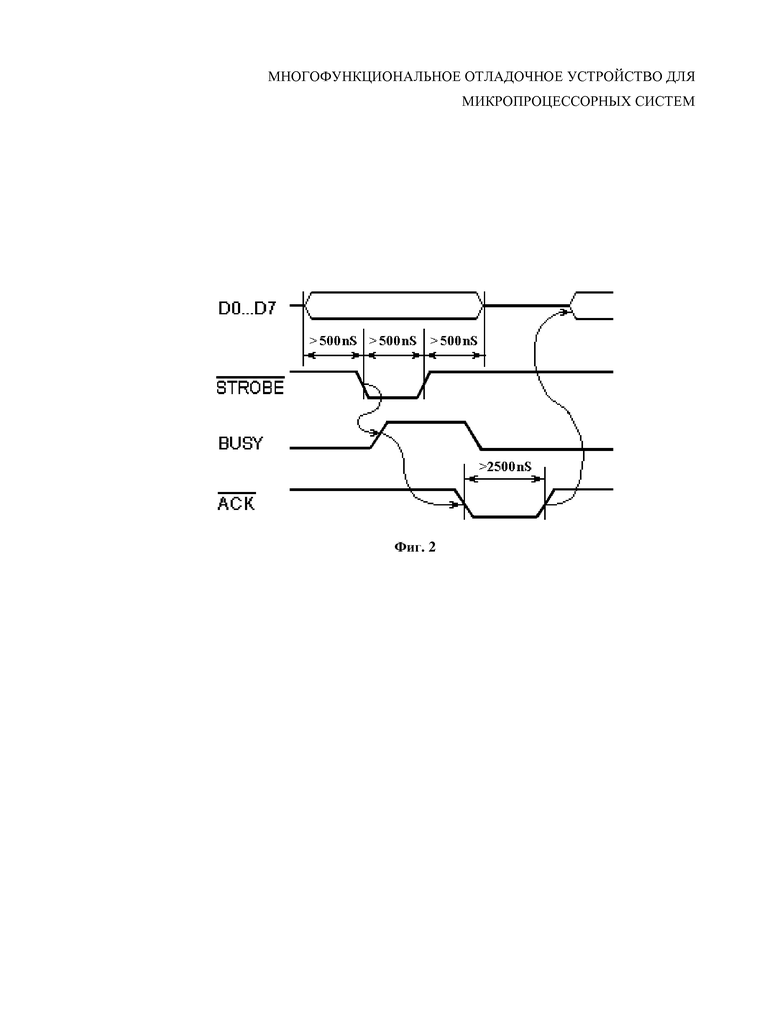

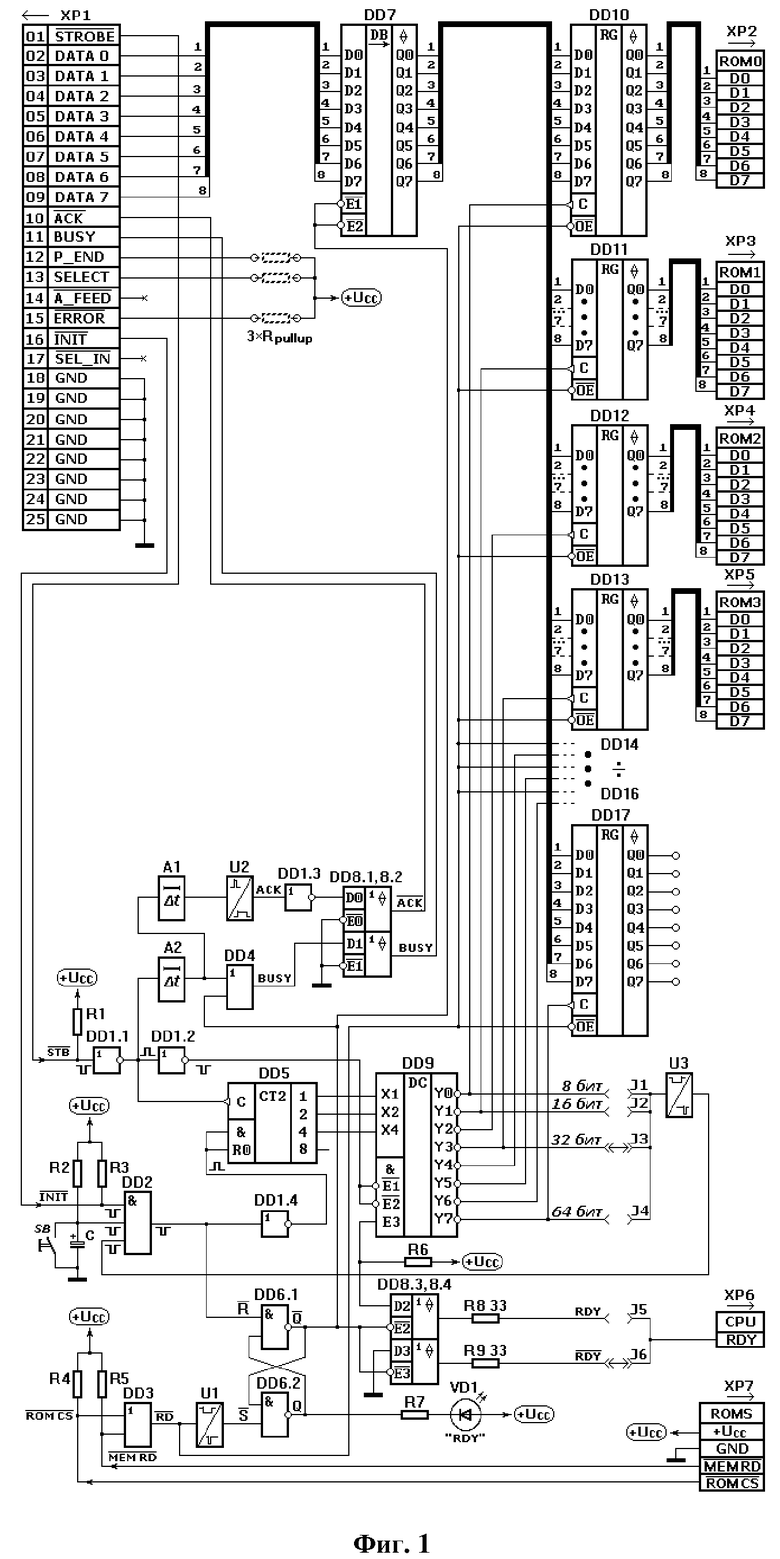

Заявляемое решение поясняется чертежами, где на фиг. 1 приведена принципиальная электрическая схема предлагаемого устройства, а на фиг. 2 — представлены эпюры сигналов, иллюстрирующие принцип работы устройства в пределах выдачи одного байта через порт принтера инструментального компьютера.

На чертеже фиг. 1 приняты следующие обозначения: XP1 - коннектор интерфейса LPT–порта принтера; XP2, XP3, XP4, XP5 - коннекторы к шине данных розеток микросхем ПЗУ; XP6 - коннектор к контакту готовности микропроцессора целевой отлаживаемой системы, XP7 - коннектор к линиям выбора ПЗУ и чтения ПЗУ одной из розеток микросхем ПЗУ, к соответствующим контактам которой также подсоединяется шина питания и общий провод; DD1.1 - формирователь стробирующего сигнала байта данных положительной полярности; DD1.2 - формирователь стробирующего сигнала байта данных отрицательной полярности; DD2 - трехвходовый логический элемент, выполняющий функцию "ИЛИ" для сигналов низкого логического уровня; A1 - формирователь сдвига сигнала ACK относительно сигнала BUSY; A2 - формирователь сдвига сигнала BUSY относительно сигнала STB; U2 - формирователь длительности сигнала ACK; DD1.3 - инвертор сигнала ACK; DD4 - логический вентиль, пропускающий активный сигнал BUSY; DD5 - восьмиразрядный счетчик импульсов STB; DD1.4 - инвертор сигнала сброса для восьмиразрядного счетчика импульсов STB; DD3 - двухвходовый логический элемент, выполняющий функцию "И" для сигналов низкого логического уровня, выделяющий совпадение сигналов выборки ПЗУ и обращения к нему операцией чтения; DD6.1, DD6.2 - асинхронный RS-триггер — синхронизатор процедуры передачи данных целевой отлаживаемой системе; U1 - формирователь короткого импульса установки асинхронного RS-триггера при обращении микропроцессора целевой отлаживаемой системы к устройству отладки как к ПЗУ операцией чтения; DD7 - тристабильный восьмиразрядный буферный шинный формирователь сигналов данных LPT–порта принтера; DD8.1, DD8.2 - мощные шинные формирователи сигналов ACK и BUSY интерфейса LPT–порта принтера; DD9 - дешифратор типа “код-позиция”, образующий в совокупности со счетчиком DD5 демультиплексор–распределитель сигнала STB; DD8.3, DD8.4 - мощные шинные формирователи с тристабильным выходом, обеспечивающие формирование сигналов готовности RDY противоположной полярности, так что сигнал необходимого типа полярности для конкретного микропроцессора целевой отлаживаемой системы может быть выбран установкой джампера J5 или J6; DD10…DD17 - восьмиразрядные регистры-защелки с тристабильным выходом, обеспечивающие выдачу информации на шину данных микропроцессора целевой отлаживаемой системы; J1…J4 - джамперы выбора разрядности микропроцессора целевой отлаживаемой системы; U3 - формирователь короткого импульса сброса асинхронного RS-триггера, фиксирующий окончание процесса передачи необходимого числа байт через LPT–порта принтера; R1…R6 - "притягивающие" резисторы, обеспечивающие согласование с линией передачи или подачу логической "1" на соответствующий вход; R8, R9 - резисторы, обеспечивающие согласование с цепью сигнала готовности RDY микропроцессора целевой отлаживаемой системы; R7 - токоограничивающий резистор в цепи питания светоизлучающего диода VD1, индицирующего включение устройства и фазу процедуры передачи данных целевой отлаживаемой системе. C - конденсатор, образующий вместе с резистором R2 времязадающую цепь начальной инициализации отладочного устройства при подаче питания; SB - кнопка принудительной инициализации отладочного устройства. Резисторы, обозначенные на чертеже как 3хRpullup, являются факультативными, поскольку дублируют резисторы, устанавливаемые на выходе LPT–порта принтера, их наличие необходимо в том случае, если соответствующие резисторы на выходе LPT–порта принтера по какой-либо причине установлены не были; назначение этих резисторов — обеспечивать подачу логической "1" на соответствующие линии интерфейса LPT–порта принтера.

Согласно представленной на фиг.1 схеме, тристабильный восьмиразрядный буферный шинный формирователь DD7 своими входами D0…D7 подключен к линиям DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера, по которым в отладочное устройство поступает байт данных из инструментального компьютера, выходы же Q0…Q7 тристабильного восьмиразрядного буферного шинного формирователя DD7 присоединены соответственно к объединенным поразрядно входам D0…D7 восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17, выводы Q0…Q7 которых, соответственно, посредством многоштырьковых вилок коннекторов XP2…XP5 соединяются с его шиной данных целевого отлаживаемого устройства через его панельки микросхем ПЗУ; входы записи C восьмиразрядных регистров-защелок DD10…DD17 с тристабильным выходом соединены с выходами Y0…Y7 дешифратора типа “код-позиция” DD9, ко входным линиям X1, X2, X4 которого подключены выходы 1, 2, 4 двоичного счетчика DD5, на счетный вход C которого через буферный элемент DD1.1 в необходимой полярности поступает сигнал подтверждения истинности выданных инструментальным компьютером в LPT–порт данных — STB (инвертированный сигнал /STROBE, поступающий с одноименной линии коннектора XP1 интерфейса LPT–порта принтера). Через буферный элемент DD1.2 инвертированный сигнал STB поступает также на входы разрешения работы /E1, /E2 дешифратора DD9, на третий вход E3 которого через резистор R6 подан разрешающий сигнал логической "1". Выходы Y0, Y1, Y3 или Y7 дешифратора типа “код-позиция” DD9 через джамперы J1…J4 выбора разрядности микропроцессора целевой отлаживаемой системы соединяются со входом формирователя короткого импульса U3, выход которого подключен к одному из входов трехвходового логического элемента DD2, выполняющего функцию "ИЛИ" для сигналов низкого логического уровня, выход которого через инвертор DD1.4 подключен ко входам начальной установки в нулевое состояние R0 двоичного счетчика DD5, а также непосредственно ко входу сброса /R асинхронного бистабильного RS–триггера, образованного элементами DD6.1, DD6.2. Инверсный выход /Q асинхронного RS–триггера подключен ко входам разрешения работы выхода /E2 и /E3 мощных шинных формирователей с тристабильным выходом DD8.3 и DD8.4, обеспечивающие на своих выходах формирование сигналов готовности RDY и /RDY противоположной полярности, один из которых, в зависимости от полярности, необходимой микропроцессору целевой отлаживаемой системы, через джамперы J5 или J6 поступает через выходной коннектор XP6 на контакт готовности этого микропроцессора. Прямой выход Q асинхронного RS–триггера через вентиль DD4 подключен ко входу мощного шинного формирователя DD8.3, на выходе которого формируется сигнал занятости BUSY, поступающий на одноименную линию коннектора XP1 интерфейса LPT–порта принтера; к прямому выходу Q асинхронного RS–триггера через токоограничивающий резистор R7 подключен также светоизлучающий диода VD1, индицирующий своим свечением включение устройства и фазу процедуры передачи данных целевой отлаживаемой системе. Вход установки /S асинхронного бистабильного RS–триггера через формирователь короткого импульса U1 соединен с выходом двухвходового логического элемента DD3, выполняющий функцию "И" для сигналов низкого логического уровня, на входы которого через коннектор XP7 подключаются линии выбора ПЗУ (/ROM CS) и чтения ПЗУ (/MEMRD) микропроцессора целевой отлаживаемой системы. Выход двухвходового логического элемента DD3 соединен также со всеми входами разрешения выходного сигнала /OE восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17, разрешая выдачу их содержимого на шину данных целевой отлаживаемой системы. К одному из входов трехвходового логического элемента DD2, выполняющего функцию "ИЛИ" для сигналов низкого логического уровня, подсоединяется также времязадающая RC-цепь, состоящая из конденсатора C и резистора R2, инициализирующая начальную установку асинхронного RS–триггера и двоичного счетчика DD5, при подаче напряжения питания на устройство отладки, причем кнопка SB, подключенная параллельно емкости C, позволяет в нештатной ситуации осуществить инициализацию принудительно. На один из входов трехвходового логического элемента DD2 подается также сигнал /INIT с одноименной линии коннектора XP1 интерфейса LPT–порта принтера, позволяющий осуществить инициализацию устройства отладки со стороны инструментального компьютера программным способом.

Выход буферного элемента DD1.1, на котором формируется инвертированный сигнал /STROBE, поступающий с одноименной линии коннектора XP1 интерфейса LPT–порта принтера, соединен со входом формирователя импульса A2, формирующего сигнал BUSY необходимой длительности, который с его выхода через вентиль DD4 подается на вход мощного шинного формирователя DD8.3, с выхода которого сигнал BUSY поступает на одноименную линию коннектора XP1 интерфейса LPT–порта принтера. С выхода формирователя импульса A2, сигнал поступает также на вход формирователя короткого импульса A1, выход которого управляет одновибратором U2, формирующим длительности сигнала ACK, поступающего через инвертор DD1.3 и мощный шинный формирователь DD8.1 на линию /ACK коннектора XP1 интерфейса LPT–порта принтера. Элементы DD1.1, A2, A1, U2, DD1.3, DD8.1 и DD8.2 формируют из поступающего от LPT–порта принтера сигнала /STROBE, приходящего в схему устройства отладки с одноименной линии коннектора XP1, сигналы /ACK и BUSY, длительность и последовательность выдачи которых устройством отладки соответствуют стандартному протоколу интерфейса ‘Centronics’ (фиг. 2), что позволяет инструментальному компьютеру работать с заявляемым устройством отладки как с принтером, используя имеющиеся программные средства операционной системы.

При описании принципа работы заявляемого устройства отладки предположим для определенности, что целевая отлаживаемая система является 32-разрядной, а необходимая микропроцессору целевой отлаживаемой системы полярность сигнала готовности /RDY является инверсной, что позволяет считать установленными коммутирующие джамперы J3 и J6, как это изображено на схеме фиг. 1.

С учетом сделанных выше допущений, заявляемое устройство отладки работает следующим образом. При отключенном питании целевой отлаживаемой системы, отладочного устройства и инструментального компьютера специальным кабелем соединяют LPT–порт принтера инструментального компьютера с коннектором XP1 устройства отладки (или же USB–порт инструментального компьютера — с коннектором XP1 устройства отладки кабелем типа USB–TO–LPT); коннекторы XP2, XP3, XP4, XP5 устройства отладки подсоединяют к шине данных целевой отлаживаемой системы через розетки микросхем ПЗУ; коннектор XP6 соединяют с контактом готовности микропроцессора целевой отлаживаемой системы, а коннектор XP7 — с линиями выбора ПЗУ и чтения ПЗУ одной из розеток микросхем ПЗУ. После чего включают инструментальный компьютер, который в процессе начальной инициализации и загрузки операционной системы может подавать в LPT–порт принтера нештатные сигналы, обусловленные определением LPT–порта в системе и его инициализацией.

После того как инструментальный компьютер готов к работе, напряжение питания подается на отлаживаемую систему, к шинам питания которой подключено и само отладочное устройство. В этот момент происходит сброс микропроцессора целевой отлаживаемой системы и начальная инициализация отладочного устройства: конденсатор C заряжается от нулевого потенциала через резистор R2, тем самым формируя на входе трехвходового логического элемента DD2 сигнал начальной инициализации длительностью примерно равной τ = R2⋅C. С выхода трехвходового логического элемента DD2 на вход сброса /R асинхронного бистабильного RS–триггера, образованного элементами DD6.1, DD6.2, вызывая его сброс, а также через инвертор DD1.4 этот сигнал поступает на входы начальной установки в нулевое состояние R0 двоичного счетчика DD5, инициируя его установку в начальное нулевое состояние. По сбросу асинхронного бистабильного RS–триггера, его выход Q устанавливается в состояние логического "0", о чем свидетельствует свечение светоизлучающего диода VD1, подключенного к выходу Q асинхронного RS–триггера через токоограничивающий резистор R7. При этом логическая "1" с инверсного выхода /Q асинхронного RS–триггера через вентиль DD4 и мощный шинный формирователя DD8.3 поступает на линию BUSY коннектора XP1 интерфейса LPT–порта принтера, свидетельствуя о том, что в данный момент разрешена работа микропроцессора целевой отлаживаемой системы, и устройство отладки принимать данные от инструментального компьютера не готово. При этом уровнем логической "1" с выхода /Q асинхронного RS–триггера выходы Q0…Q7 тристабильного восьмиразрядного буферного шинного формирователь DD7 переведены в высокоимпедансное состояние по входам разрешения выхода /E1 и /E2, следовательно, сигналы с линий DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера на объединенные поразрядно входы D0…D7 восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17 не поступают. Выходы Q0…Q7 этих регистров-защелок, подключенные посредством многоштырьковых вилок коннекторов XP2…XP5 к шине данных целевого отлаживаемого устройства также находятся в высокоимпедансном состоянии, поскольку обращения микропроцессора отлаживаемого устройства по адресам своего ПЗУ еще не происходило и двухвходовый логический элемент DD3, выделяющий совпадение сигналов выборки ПЗУ и обращения к нему операцией чтения удерживает на всех выводах /OE разрешения выхода регистров-защелок DD10…DD17 запрещающий сигнал с уровнем логической "1".

Логическая "1" с инверсного выхода /Q асинхронного RS–триггера по входам /E2 и /E3 удерживает в высокоимпедансном состоянии выходы мощных шинных формирователей DD8.3 и DD8.4, в результате чего на вход готовности /RDY микропроцессора отлаживаемого устройства через джампер J6 и выходной коннектор XP6 активный уровень сигнала не поступает, и микропроцессор может начать работу.

Микропроцессор отлаживаемого устройства после начального сброса выставляет по своей шине адреса начальный адрес системного ПЗУ, функции которого в данный момент выполняет устройство отладки, что приводит к появлению уровня логического "0" на одном из входов двухвходового логического элемента DD3 через линии выбора ПЗУ (/ROM CS) коннектора XP7, после чего микропроцессор обращается к системному ПЗУ сигналом чтения ПЗУ (/MEMRD) низкого уровня, который через коннектор XP7, поступает на второй вход двухвходового логического элемента DD3, в результате чего на выходе последнего формируется уровень логического "0", который через формирователь короткого импульса U1 воздействует на вход установки /S асинхронного бистабильного RS–триггера. На выходе Q асинхронного RS–триггера при этом устанавливается уровень логической "1", светоизлучающий диод VD1 гаснет, свидетельствуя о том, что микропроцессор отлаживаемого устройства перешел в режим ожидания, поскольку в этот же момент установившийся на инверсном выходе /Q асинхронного RS–триггера уровень логического "0" по входам /E2 и /E3 разрешает выдачу с выходов мощных шинных формирователей DD8.3 и DD8.4 активных уровней сигнала готовности, один из которых — /RDY — через резистор R9 и джампер J6 достигает через коннектор XP6 входа готовности микропроцессора, тем самым, останавливая его работу и переводя его в режим ожидания.

Уровень логического "0" с инверсного выхода /Q асинхронного RS–триггера по входам разрешения выхода /E1 и /E2 разрешает прохождение сигналов через тристабильный восьмиразрядный буферный шинный формирователь DD7 с линий DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера на объединенные поразрядно входы D0…D7 восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17; этот же уровень логического "0" через вентиль DD4 и мощный шинный формирователя DD8.3 поступает на линию BUSY коннектора XP1 интерфейса LPT–порта принтера, свидетельствуя о том, что в данный момент микропроцессор находится в режиме ожидания, и отладочное устройство готово к принятию байтов кода от инструментального компьютера. Удерживаемый на выходе двухвходового логического элемента DD3 находящимся в режиме ожидания микропроцессором отлаживаемого устройства сигнал логического "0" поступает на все выводы /OE разрешения выхода регистров-защелок DD10…DD17, разрешая выдачу их содержимого на шину данных отлаживаемого устройства.

В этом состоянии возможна передача инструментальным компьютером через LPT–порта принтера управляющих кодов или данных на шину данных отлаживаемого устройства через отладочное устройство. Подготовленный в инструментальном компьютере бинарный файл кодов (пусть для определенности он носит название code.bin) можно выдать "на печать" самым простым штатным способом, системной командой copy /b code.bin PRN, что в операционных системах DOS и MS Windows вызывает выдачу на печать в бинарном виде файла code.bin. Можно воспользоваться также системной командой print, задав ей необходимые параметры, или выдать файл code.bin на печать из любой программы, поддерживающей печать двоичных файлов.

При выдаче кодов на принтер через LPT–порт системными командами инструментальный компьютер соблюдает стандартный протокол обмена, диаграмма которого представлена на фиг. 2. Проверив, что устройство не занято по линии BUSY, инструментальный компьютер выставляет по линиям DATA 0…DATA 7 текущий байт, выводимый "на печать" из файла code.bin, сопровождая его сигналом сигнала /STROBE низкого уровня. Поскольку работа тристабильного восьмиразрядного буферного шинного формирователь DD7 в этот момент разрешена активным уровнем на его входах /E1 и /E2, сигналы с линий DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера поступают на объединенные поразрядно входы D0…D7 восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17. Инвертированный элементом DD1.1 сигнал STROBE поступает на вход двоичного счетчика DD5, работа которого в данный момент разрешена, а сам счетчик инициализирован начальным значением "0". Сигнал /STROBE через элемент DD1.2 поступает также на входы разрешения работы /E1, /E2 дешифратора DD9, который преобразует входной код на своих входных линиям X1, X2, X4, поступивший с выходов счетчика DD5, в активное состояние своего выхода Y0, по сути, распределив пришедший импульс /STROBE на вход записи C регистра-защелки DD10, который и зафиксирует байт, переданный с линий DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера через восьмиразрядный буферный шинный формирователь DD7. По окончанию импульса /STROBE состояние счетчика DD5 увеличится на единицу. Элементы DD1.1, A2, A1, U2, DD1.3, DD8.1 и DD8.2 чисто формально сформируют из поступающего от LPT–порта принтера сигнала /STROBE, сигналы /ACK и BUSY, необходимые для соблюдения стандартного протокола передачи байта принтеру по интерфейсу ‘Centronics’ (фиг. 2).

Поскольку сигнал BUSY по окончанию передачи одного байта сообщает инструментальному компьютеру, что отладочное устройство вновь готово принять от него байт данных, инструментальный компьютер выставляет по линиям DATA 0…DATA 7 следующий байт, выводимый "на печать" из файла code.bin, вновь сопровождая его сигналом сигнала /STROBE низкого уровня. Весь цикл работы устройства отладки повторяется с той лишь разницей, что передаваемый байт будет записан в регистр-защелку DD11, а двоичный счетчика DD5 по окончанию этого цикла будет содержать значение "2". Следовательно, вновь передаваемый инструментальным компьютером "на печать" очередной байт из файла code.bin будет зафиксирован в регистре-защелке DD12, а двоичный счетчика DD5 по окончанию этого цикла будет содержать значение "3". Четвертый байт, передаваемый инструментальным компьютером из файла code.bin запишется в регистр-защелку DD13, после чего на шинах отлаживаемого устройства полностью появится переданное инструментальным компьютером 32-битное слово, а сигнал с выхода Y3 дешифратора DD9 своим задним фронтом через джампер J3 запустит формирователь короткого импульса U3, с выхода которого через один из входов трехвходового логического элемента DD2, выполняющего функцию "ИЛИ" для сигналов низкого уровня, сформированный короткий импульс попадет непосредственно на вход сброса /R асинхронного бистабильного RS–триггера, а через инвертор DD1.4 — на входы начальной установки в нулевое состояние R0 двоичного счетчика DD5. Воздействие этого короткого импульса приведет к тому, что двоичный счетчик DD5 будет инициализирован значением "0", а асинхронный бистабильный RS–триггер вернется в то же состояние, в котором он находился после начальной инициализации. Логическая "1" с инверсного выхода /Q асинхронного RS–триггера по входам /E2 и /E3 переведет в высокоимпедансное состоянии выходы мощных шинных формирователей DD8.3 и DD8.4, в результате чего сигнал на входе готовности /RDY микропроцессора отлаживаемого устройства станет неактивным и микропроцессор, выйдя из состояния ожидания, сразу же считает запрошенные им 32-битные данные с выходов регистров-защелок DD10…DD13, после чего активный сигналом чтения (/MEMRD) низкого уровня, будет им снят, что приведет к появлению уровня логической "1" на выходе двухвходового логического элемента DD3, которая поступает на все выводы /OE разрешения выхода регистров-защелок DD10…DD17, отключая их выходы Q0…Q7 от шины данных отлаживаемого устройства и переводя их в высокоимпедансное состояние. Уровнем логической "1" с выхода /Q асинхронного RS–триггера выходы Q0…Q7 тристабильного восьмиразрядного буферного шинного формирователь DD7 также переводятся в высокоимпедансное состояние по входам разрешения выхода /E1 и /E2, и следовательно, сигналы с линий DATA 0…DATA 7 коннектора XP1 интерфейса LPT–порта принтера на объединенные поразрядно входы D0…D7 восьмиразрядных регистров-защелок с тристабильным выходом DD10…DD17 более не поступают. Логическая "1" с инверсного выхода /Q асинхронного RS–триггера через вентиль DD4 и мощный шинный формирователя DD8.3 поступает также на линию BUSY коннектора XP1 интерфейса LPT–порта принтера, свидетельствуя о том, что в данный момент разрешена работа микропроцессора целевой отлаживаемой системы, и устройство отладки принимать данные от инструментального компьютера не готово.

Микропроцессор целевой отлаживаемой системы сразу же выполняет полученный от устройства отладки код, и снова обращается к нему, как к системному ПЗУ, снова попадает в режим ожидания, а инструментальный компьютер опять передаёт ему через LPT–порт принтера очередные 4 байта из файла code.bin. Процесс повторяется циклически, до тех пор, пока не будут переданы все необходимые байты и управление не будет передано на адрес памяти, не входящий в диапазон адресов выборки отладочного устройства. Заметим, что любое обращение микропроцессора целевой отлаживаемой системы в диапазон адресов выборки отладочного устройства приводит к переводу микропроцессора в режим ожидания. Это свойство позволяет использовать заявляемое отладочное устройство в качестве отладчика с возможностью пошагового прохождения программы и останова в контрольных точках, а также простого устройства ввода, аналогичного клавиатуре, клавишной панели или набору датчиков, что существенно расширяет функциональность устройства без дополнительных аппаратных затрат.

Заявляемое простое многофункциональное отладочное устройство для микропроцессорных систем позволяет повысить производительности процесса отладки микропроцессорных систем и устройств, а также снизить его трудоемкость и уменьшить материальные затраты на этот процесс благодаря своей сравнительно несложной конструкции и универсальности при довольно развитых функциональных возможностях.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1999 |

|

RU2214621C2 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для отладки программ | 1987 |

|

SU1425685A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

Изобретение относится к области электроники и микропроцессорной техники и может найти обширное применение при отладке, ремонте и эксплуатации широкого спектра микропроцессорных систем и устройств, как уже существующих, так и вновь разрабатываемых, а также при изучении и исследовании принципов работы подобных систем и устройств в практических разделах дисциплин учебных заведений, имеющих соответствующую направленность подготовки специалистов. Технический результат – повышение производительности и снижение трудоемкости процесса отладки цифровых микропроцессорных систем и устройств. В конструкцию отладочного устройства, использующего часть памяти внешнего инструментального компьютера для хранения программы целевой отлаживаемой микропроцессорной системы и имеющего в своем составе интерфейс LPT–порта принтера для передачи программ и данных в отлаживаемую микропроцессорную систему через тристабильный восьмиразрядный буферный шинный формирователь, а также устройство синхронизации, представляющее собой бистабильный RS-триггер с подключенными к его входам формирователями коротких импульсов, согласно изобретению, в зависимости от разрядности N микропроцессора отлаживаемой системы, введены дополнительно N/8 восьмиразрядных регистров-защелок с тристабильным выходом, входы которых объединяются поразрядно и подключаются через тристабильный восьмиразрядный буферный шинный формирователь соответственно к линиям данных интерфейса принтера, а выходы посредством многоштырьковых вилок соединяются через панельки ПЗУ отлаживаемого устройства с его шиной данных, а также двоичный счетчик и дешифратор, образующие демультиплексор–распределитель сигнала стробирования, направляющий каждый следующий сигнал подтверждения истинности выданных инструментальным компьютером данных на вход записи соответствующего регистра-защелки. Дополнительно введенные узлы формирования сигналов занятости и подтверждения приёма байта дают возможность устройству осуществлять взаимодействие с инструментальным компьютером через порт принтера по стандарту интерфейса ‘Centronics’. 2 ил.

Отладочное устройство для цифровых микропроцессорных систем шинной организации, сочетающее в себе функции загрузчика программ и эмулятора постоянного запоминающего устройства, использующего часть памяти внешнего инструментального компьютера для хранения программы отлаживаемой микропроцессорной системы и имеющее в своем составе интерфейс порта принтера для передачи программ и данных в отлаживаемую микропроцессорную систему через тристабильный восьмиразрядный буферный шинный формирователь, а также устройство синхронизации, управляющее процессом передачи данных через шинный формирователь и представляющее собой бистабильный RS-триггер с подключенными к его входам формирователями коротких импульсов, отличающийся тем, что в него дополнительно введены в зависимости от разрядности N микропроцессора отлаживаемой системы, N/8 восьмиразрядных регистров-защелок с тристабильным выходом, двоичный счетчик и дешифратор, а также узлы формирования сигналов занятости и подтверждения приёма байта, причем входы восьмиразрядных регистров-защелок объединяются поразрядно и подключаются через тристабильный восьмиразрядный буферный шинный формирователь соответственно к линиям данных интерфейса принтера, а выходы соединяются через панельки ПЗУ отлаживаемого устройства с его шиной данных, двоичный счетчик и дешифратор, образуют демультиплексор–распределитель сигнала стробирования, направляющий каждый следующий сигнал подтверждения истинности выданных инструментальным компьютером данных на вход записи соответствующего регистра-защелки, а узлы формирования сигналов занятости и подтверждения приёма байта, позволяют осуществлять взаимодействие с инструментальным компьютером через порт принтера по стандарту интерфейса ‘Centronics’.

| Способ получения суспензионного полистирола | 1961 |

|

SU148227A1 |

| Машина для производства земляных работ | 1919 |

|

SU523A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| АКТИВНЫЙ АППАРАТНЫЙ СТЕК ПРОЦЕССОРА | 2013 |

|

RU2530285C1 |

Авторы

Даты

2017-10-24—Публикация

2016-10-05—Подача