выходу первого элемента НЕ, а третьим входом - к входу второго элемента ИЕ и выходу третьего логического компаратора, соединенного первым входом с вторым выходом делителя частоты, первым входом второго логического компаратора и первым входом четвертого логич-ского компаратора, подключенного выходом к первому входу третьего элемента И, соединенного вторым входом с выходом второго элемента НЕ, а третьим входом - с вторым выходом дешифратора, подключенного входом к первому выходу счетчика уставок и первому вход

первого логического компаратора, соединенного выходом с вторыми входами четвертого и третьего логических компараторов и вторым входом второго Логического компаратора, подключенного выходом к входу первого элемента НЕ, причем второй выход счетчика уставок соединен с входом элемента задержки, выход третьего элемента И - с вторым входом второго элемента памяти, выход второго элемента ИЛИ с вторьм входом блока противовключения, третий вход которого подключен к выходу распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1987 |

|

SU1480079A1 |

| Устройство для управления шаговым двигателем | 1987 |

|

SU1607071A1 |

| Устройство для управления шаговым двигателем | 1989 |

|

SU1646036A2 |

| Система программного управления | 1982 |

|

SU1022116A1 |

| Многоканальное устройство программного управления шаговыми двигателями | 1985 |

|

SU1320794A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1334350A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1356176A2 |

| Многоканальное устройство для программного управления | 1978 |

|

SU748431A1 |

| Устройство для кинематического дробления стружки на токарных станках с числовым программным управлением | 1981 |

|

SU1004974A1 |

| Устройство для программного управления | 1986 |

|

SU1397880A1 |

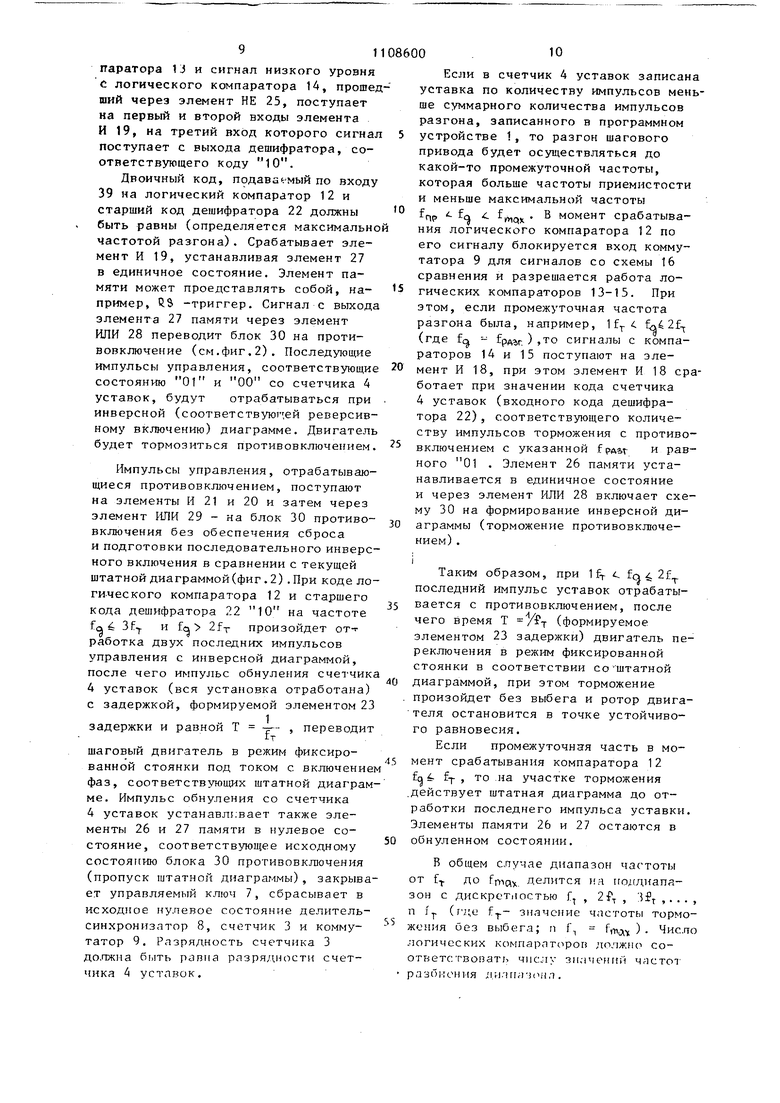

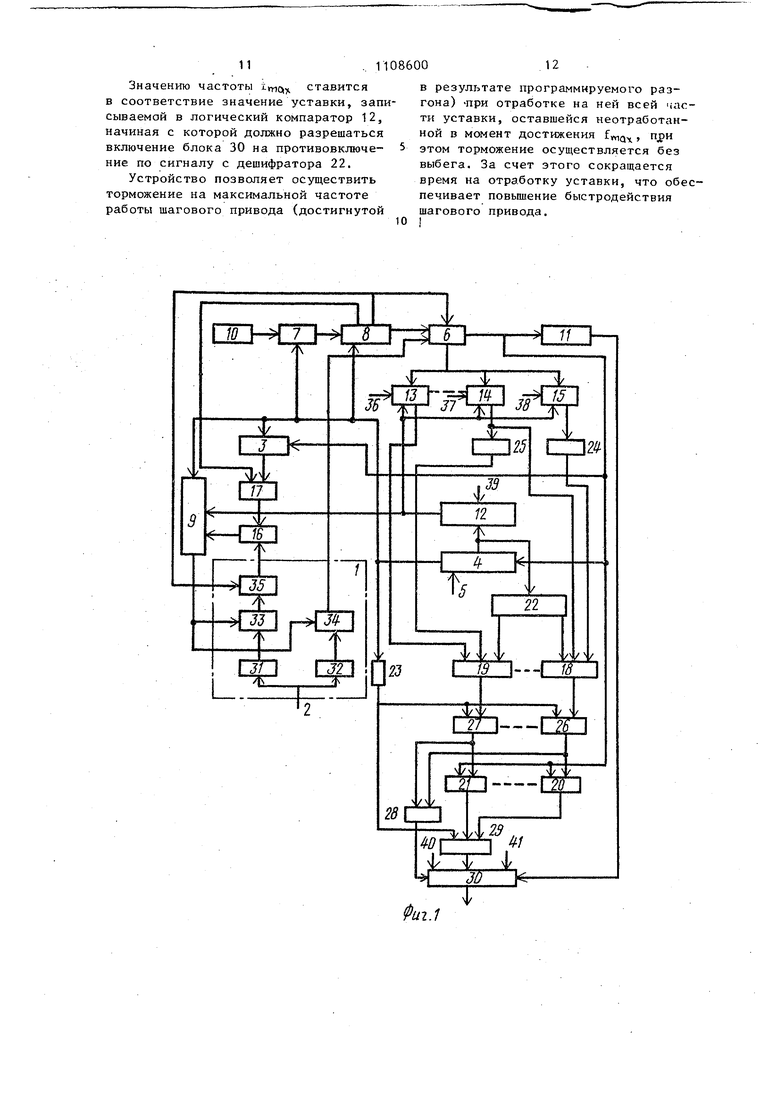

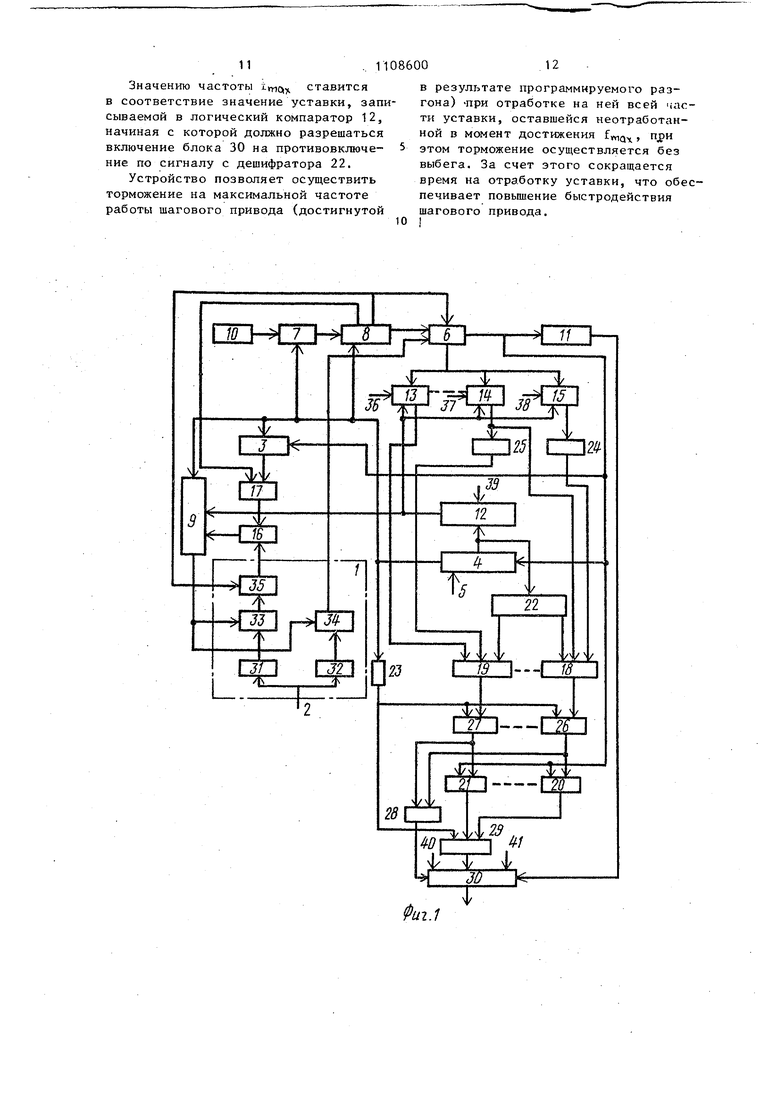

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ, содержащее распределитель, делитель частоты, делитель-синхронизатор, счетчик уставок, логический компаратор, управляемый ключ, счетчик, коммутатор, элемент И, схему сравнения,программное устройство и генератор импульсов, выход которого Подключен к первому входу управляемого ключа, соединенного выходом с первым входом делителя-синхронизатора , подключенного первым выходом. к первому входу делителя частоты, связанного первьЕм вькодом с входом распределителя, первым входом счетчика и первым входом счетчика уставок, первый выход которого подключен к первому входу логического компаратора, а вторым выходом соединенного с первым входом коммутатора, вторым входом счетчика, вторым входом управляемого ключа и вторым входом делителя-синхронизатора, подключенного рторым выходом к первому входу элемента И, а третьим выходом к первому входу программного устройства и второму входу делителя частоты, соединенного третьим входом с первым выходом программного устройства, подключенного вторым и третьим входами к выходу коммутатора, связанного вторым входом с выходом схемы сравнения, соединенной первым входом с вторым выходом программного устройства, а вторым входом - с выходом элемента И, подключенного вторым входом к выходу счетчика, а выход логического компаратора соединен с третьим входом коммутатора, отличающееся тем, что, с целью повышения быстродействия шагового двигателя, введены второй, третий и четвертьй логи:еские компараторы, первый и второй элементы НЕ, дешифратор, элемент задержки, второй (Л третий, четвертый и пятый элементы И, первый и второй, элементы памяти, первый и второй элементы ИЛИ и блок противовключения, первый вход которого подключен к выходу первого элемента ИЛИ, соединенного первьм входом с первым входом пятого элемента и выходом второго элемента памяти, а вторьм входом - с выходом первого элемента памяти и первым входом четвертого элемента И, подключенного вторым входом к первому выходу делителя частоты и второму входу пятого элемента И, соединенного выходом с первым входом второго элемента ИЛИ. подключенного вторым входом к выходу четвертого элемента И, а третьим входом - к выходу элемента задержки, первому входу второго элемента памяти и первому входу первого элемента памяти, соединенного входом с выходом второго элемента И, подключенного первым входом к первому выходу дешифратора, вторым входом - к

Изобретение относится к электротехнике, а именно к системам управления приводами с шаговыми двигателями ,

Известно устройство для управления шаговым двигателем, содержащее мультивибратор, коммутатор и пусково устройство, соединенное с элементами задержки, выходы которых связаны с коммутатором 1.

Однако данное устройство не обеспчивает торможения шагового двигателя с максимальной частотой достигнутой в режиме разгона.

Известно устройство для управлени шаговым двигателем, содержащее тактовый генератор, управляемый ключ, счетчик, делитель, элемент задержки и распределитель .

Устройство предназначено для увеличения быстродействия шагового двигателя, что достигается подачей на распределитель второго импульса частотой меньшей, чем частота входных импульсов, причем следующие после второго импульсы серии поступают на распределитель с собственной частотой и задержкой последнего импульса серии.

Недостаток указанного устройства невозможность разгона шагового двигателя до максимальной частоты и торможения этой частоты без выбега.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство

Для управления шаговым двигателем, содержащее распределитель, управляемый ключ, реверсивный счетчик, схему сравнения, генератор импульсов, программное устройство, делитель частоты, элемент И, коммутатор, счетчик, логический компаратор, элемент памяти и делитель-синхронизатор, первый вход которого соединен с первым выходом счетчика, подключенным к.первому входу коммутатора и второму входу управляемого ключа, выход которого связан с вторым входом делителя-синхронизатора, первый выход которого подключен к первому входу элемента памяти, второй выход - к первому входу элемента И, третий к первому входу делителя частоты, второй вход которого соединен с четвертым выходой делителя-синхронизатора и первым входом программного устройства, второй вход которого соединен с выходом коммутатора, первый выход - с первьм входом схемы сравнения, а второй выход - с третьим входом делителя частоты, выход которого связан с распределите-, лем, первым входом реверсивного счетчика и первым входом счетчика, второй выход которого подключен к первому вхОлТУ логического компаратора, второй вход которого соединен с выходом реверсивного счетчика и вторым входом элемента И, выход которого соединен с вторым входом схе-мы сравнения, выход которой подключен к второму входу коммутатора, третий вход которого соединен с вторым входом реверсивного счетчика, выходом логического компаратора и вторым входом элемента , памяти, выход которого подключен к третьему входу элемента И1.3Д. Известное устройство позволяет реализовать любой закон изменения частоты работы шагового привода в переходных режимах (плавное изменение и скачкообразное изменение с отработкой ааданного количества управляющих импульсов на каждом приращении частоты). Недостатком устройства является невозможность торможения с максималь ной частоты при отработке на ней всех импульсов управления, оставшихся неотработанными в момент достижения максимальной частоты, что не обе спечивает максимального быстродействия в переходных режимах (разгонторможение) . Цель изобретения - повыщение быст родействия шагового двигателя. Поставленная цель достигается тем что в устройство для управления шаговым двигателем, содержащее распределитель, делитель частоты, делитель синхронизатор, счетчик уставок, логический компаратор, управляемый клю счетчик, коммутатор, элемент И, схему сравнения, программное устройство и генератор импульсов, выход которог подключен к первому входу управляемого ключа, соединенного выходом с первым входом делителя-синхронизатора, подключенного первым выходом к первому входу делителя частоты, соединенного первым выходом с входом распределителя, первым входом счетчика и первым входом счетчика уставок, подключенного первым выходом к первому входу логического компаратора, а вторым выходом соединенного с первым входом коммутатора, вторым входом счетчика, вторым входом управляемого ключа и вторым входом делителя-синхронизатора, подключенного вторым выходом к первому входу элемента И, а третьим выходом - к пер- вому входу программного устройства и второму входу делителя частоты, соединенного третьим входом с первы вьтходом программного устройства, по ключенного вторым и входами к выходу коммутатора, связанного торым входом с выходрм схемы срлвения, соединенный первым входом с вторым выходом программного устройства, а вторым входом - с вькодом элемента И, подключенного вторым входом к выходу счетчика, а выход логического компаратора соединен с третьим входом коммутатора, введены второй, третий и четвертый логические компараторы, первый и второй элементы НЕ, дешифратор, элемент задержки, второй, третий, четвертый и пятый элементы И, первый и второй элементы памяти, первый и второй элементы ИЛИ и блок противовключения, первый вход которого подключен к выходу первого элемента ИЛИ, соединенного первым входом с первым входом пятого элемента И и выходом второго элемента памяти, а вторым входом - с .выходом первого элемента памяти и первым входом четвертого элемента И, подключенного вторым входом к первому выходу делителя частоты и второму входу пятого элемента И, соединенного выходом с первым входом второго элемента ИЛИ, подключенного вторым входом к выходу четвертого элемента И, а третьим входом - к выходу элемента задержки, первому входу второго элемента памяти и первому входу первого элемента памяти, соединенного вторым входом с выхсдом второго элемента И, подключенного первым входом к первому выходу дешифратора, вторым входом - к выходу первого элемента НЕ, а третьим входом к входу второго элемента НЕ и выходу третьего логического компаратора, соединенного первым входом с вторым выходом делителя частоты, первым входом второго логического компаратора и первым входом четвертого логического компаратора, подключенного выходом к первому входу третьего элемента И, соединенного вторым входом с выходом второго элемента НЕ, а третьим входом - с вторым выходом дешифратора, подключенного входом к первому выходу счетчика уставок и первому входу первого логического компаратора, соединенного выходом с вторыми выходами четвертого и третьего логических компараторов и вторым входом второго логического компаратора, подключенного выходом к входу первого элемента НЕ, причем второй выход счетчика уставок соединен с входом элемента задержки, выход третьего элемента И - с вторым входом второго элемента памяти, выход второго элемента ИЛИ - с вторым входом блока противовключения, третий вход которого подключен к выходу распределителя . На фиг, 1 приведена функциональная схема устройства для управления шаговым двигателем в однолинейном изображении; на фиг. 2 - один из ва риантов выполнения блока противовключения с таблицей истинности для четырехфазного шагового двигателя. Устройство {фиг. 1) содержит про граммное устройство 1 с входом записи 2, счетчик 3, счетчик 4 уставо с входом 5, делитель 6 частоты, управляемый ключ 7, делитель-синхронизатор 8, коммутатор 9, генератор 10 импульсов, распределитель 11, ло гические компараторы 12-15, схему 16 сравнения, элементы И 17-21, дешифратор 22, элемент 23. задержки, элементы НЕ 24 и 25, элементы 26 и 27 памяти, элементы ИЛИ 28 и 29 и блок 30 противовключения. Программное устройство 1 может состоять, например, из регистровой памяти 31. и 32 констант количества импульсов управления и констант частоты соответственно, мультиплексоров 33 и 34 и выходного регистра 35. В качестве мультиплексоров могут быть использованы, например, интегральные микросхемы серии 564ИП2. Объем регистровой памяти 31 и 32 зависит от реализуемого в программе закона. Логические компараторы 12-15 снабжены входами 36-39 а блок 30 - входами 40 и 41. Предлагаемое устройство работает следующим образом. В программное устройство 1 по вх ду 2 записывается оптимальная для конкретного шагового привода програ ма разгона, состоящая из констант (в двоичном коде) приращения часто и констант (в двоичном коде) количе ства импульсов управления, необходи мых для отработки на каждом прираще нии частоты. В исходном состоянии счетчики 3 и 4, делитель 6 частоты, делительсинхронизатор 8, элементы 26 и 27 памяти находятся в .обнуленном состо янии. Нулевое состояние счетчика 4 уставок, предназначенного для прием через вход 5 и отработки заданной на привод уставки (числа импульсов управления), запирает управляемый ключ 7. Исходное состояние коммутатора 9 соответствует выборке констант частоты и количества импульсов по первому адресу программного устройства 1 . Коммутатор 9 может быть выполнен, например, в виде двоичного счетчика, разрядность которого выбирается исходя из количества ступеней (закона) разгона. При значении двоичного кода 111 (соответствующего максимально возможной частоте разгона) и по сигналу с логического компаратора 12 счетный вход коммутатора 9 закрывается для сигнала со схемы 16 сравнения. При записи уставки в счетчик 4 уставок через вход 5 (состояние счетчика отлично от нуля) управляемый ключ 7 открывается и постоянная частота генератора 10 импульсов Лоступает на вход двухразрядного делителя-синхронизатора 8, второй синхронизирующий импульс которого осуществляет запись кода, соответствующего первому значению частоты работы привода и содержащегося по первому адресу регистровой памяти 32 программного устройства 1, в делитель 6 частоты и кода, соответствующего количеству импульсов отработки на этой частоте и содержащегося по первому адресу регистровой памяти 31, в выходной регистр 35 программного устройства 1. Импульсы переполнения с делителя-синхронизатора 8 являются входными для делителя 6 частоты. Импульсы переполнения с делителя 6 частоты следуют с заданной частотой, f i ( частота приемистости шагового двигателя для соответствующей нагрузки привода) и поступают на распределитель 11 для. формирования диаграммы работы шагового двигателя. Делитель 6 частоты - двоичный счетчик, работающий на сложение, с параллельным вводом и поразрядным выводом инфорации (может быть реализован, например, на микросхеме серии 564ИЕ11). С выхода распределителя 11 импульсы управления поступают на вход блока 3d противопключсиия, который пропускает импульсы управления на усилмтоль мощности в соответствии с 7 . . диаграммой, сформированной распреде лителем 11, поскольку элементы 26 и 27 памяти находятся в обнуленном состоянии. Одновременно импульсы с выхода д лителя 6 частоты поступают на входы счетчика 3 и.счетчика А уставок. Счетчик 4 уставок работает на вычитание, счетчик 3 - на сложение. Разрядность счетчика 3 и 4 одинакова. После отработки заданного количества импульсов Г) на частоте срабатывает схема 16 сравнения по первому синхроимпульсу делителясинхронизатора 8, который через элемент И 17 (элементы И для каждого разряда счетчика 3) подключает параллельный код счетчика 3 к схеме 16 сравнения.. Сигнал с выхода схемы 16 сравнения переключает коммутатор 9 на выборку кодов (при помощи мультиплексоров 34 и 33) частоты и количества импульсов по следующему адресу программного устройства 1. Коды частот и количества импульсов, соответству щих 2 и , записываются в делител 6 частоты и в вЬкодной регистр 35 программного устройства 1 вторым синхроимпульсом делителя-синхрониза тора 8. При этом значение количества импульсов программируется в количе виде п ство импульсов, заданное для отработки на частоте f ; д.д - количеств импульсов, заданное для отработки на частоте f2 После отработки на этой частоте заданного количества импульсов процесс приращения частот повторяется и осуществляется разгон привода. Если в счетчик 4 уставок записан уставка, превышающая суммарное коли чество импульсов разгона, записанное в программном устройстве 1, то разгон осуществляется по заложенном в программном устройстве 1 закону до максимальной частоты. При этом коммутатор 9 выбирает по последнему адресу программного устройства 1 максимальноезначение частоты и нулевое значение количества отработан ,ных импульсов. этого привод работает на максимальной частоте, причем нулево значение количества отработанных им пульсов врегистре 35 обеспечивает несрабатывание схемы 16 сравнения 0 И тем самым постоянство значения максимальной частоты в делителе 6 частоты. Работа привода на максимальной частоте продолжается до момента срабатывания логического компаратора 12, который предназначен для сравнения параллельных кодов со счетчика 4 уставок, поданных по входу 39. По входу 39 подается двоичный код, соответствующий количеству импульсов отработки, в течение которых при включении торможения . против ов к лючением рассеивается вся к инетическая энергия системы, накопленная при разгоне и работе на максимальной частоте, и привод после отработки последнего импульса остановится в расчетной точке устойчивого равновесия, перейдя в режим фиксированной стоянки под током. Логический компаратор 12 срабатывает при равенстве кода счетчика 4.уставок, работающего на вычитание, и кода, поданного по входу 39. Сигнал с выхода компаратора 12 разрешает работу логических компараторов 13-15, которые предназначены для сравнения параллельных кодов с д.елителя 6 частоты, поданньсх по входам 36-38. В логический компаратор 15 по Входу 38 подается значение частоты т - частоты торможения без выбега, в логический компаратор 14 по входу 37 - значение частоты , в логический компаратор 13 по входу 36 значение частоты 3. Логические компараторы 13-15 срабатывают при значениях частоты в делителе 6 частоты fqt3f-f , fa 4 2fT , fn t f т- соответственно. Логические компараторы 12-15 могут быть выполнены, например, на базе микросхем 564Ж11. На вход двоичного дешифратора 22 подается параллельный код со счетчика 4 уставок. Дешифратор 22 расчитан на двоичные коды количества импульсов торможения противовключением. На фиг. 1 показан дешифратор на двоичные коды 01 и 10. Если, например, максимально достигнутая в результате разгона частота работы привода составляет и f л 2f- , то на этой частоте происходит отработка всей уставки до момента срабатывания логического компаратора 12, после чего сигнал высокого уровня с логического ком91ггаратора 13 и сигнал низкого уровня с логического компаратора 14, проше ший через элемент НЕ 25, поступает на первый и второй входы элемента И 19, на третий вход которого сигна поступает с выхода дешифратора, соответствующего коду 10. Двоичный код, прдава мый по входу 39 на логический компаратор 12 и старший код дешифратора 22 должны быть равны (определяется максимальн Частотой разгона). Срабатывает элемент И 19, устанавливая элемент 27 в единичное состояние. Элемент памяти может проедставлять собой, например, 5S -триггер. Сигнал с выход элемента 27 памяти через элемент ИЛИ 28 переводит блок 30 на противовключение (см.фиг.2). Последующие импульсы управления, соответствующи состоянию 01 и 00 со счетчика 4 уставок, будут отрабатываться при инверсной (соответствуюг;ей реверсивному включению) диаграмме. Двигатель будет тормозиться противовключением Импульсы управления, отрабатывающиеся противовключением, поступают на элементы И 21 и 20 и затем через элемент ИЛИ 29 - на блок 30 противовключения без обеспечения сброса и подготовки последовательного инверс ного включения в сравнении с текущей штатной диаграммой(фиг .2) . При коде ло ги-ческого компаратора 12 и старшего кода дешифратора 22 10 на частоте fa 6 3f и fq 2f-(- произойдет от-т работка двух последних импульсов управления с инверсной диаграммой, после чего импульс обнуления счетчик 4 уставок (вся установка отработана) с задержкой, формируемой элементом 23 задержки и равной Т -г- , переводит шаговый двигатель в режим фиксированной стоянки под током с включение фаз. Соответствующих штатной диаграм ме. Импульс обнуления со счетчика 4 уставок устанавл1:вает также элементы 26 и 27 памяти в нулевое состояние, соответствующее исходному состоянию блока 30 противовключения (пропуск штатной диаграммы), закрыва ет управляемый ключ 7, сбрасывает в исходное нулевое состояние делительсинхронизатор 8, счетчик 3 и коммутатор 9. Разрядность счетчика 3 до.ожна быть равна разрядности счетчика 4 уставок. 0 Если в счетчик 4 уставок записана уставка по количеству импульсов меньше суммарного количества импульсов разгона, записанного в программном устройстве 1, то разгон шагового привода будет осуществляться до какой-то промежуточной частоты, которая больще частоты приемистости и меньше максимальной частоты fqp - f а rnqx момент срабатывания логического компаратора 12 по его сигналу блокируется вход коммутатора 9 для сигналов со схемы 16 сравнения и разрешается работа логических компараторов 13-15. При этом, если промежуточная частота разгона была, например, 1 f i. 4 (где fa - fpAir. ) jTo сигналы с компараторов 14 и 15 поступают на элемент И 18, при этом элемент И 18 сработает при значении кода счетчика 4 уставок (входного кода дешифратора 22), соответствующего количеству импульсов торможения с противовключением с указанной Грдаг и равного 01 . Элемент 26 памяти устанавливается в единичное состояние и через элемент ИЛИ 28 включает схему 30 на формирование инверсной диаграммы (торможение противовключением) . Таким образом, при 1 f с f о 4 2f последний импульс уставок отрабатывается с противовключением, после чего время Т / (формируемое элементом 23 задержки) двигатель переключения в peжJiм фиксированной стоянки в соответствии соштатной диаграммой, при этом торможение произойдет без выбега и ротор двигателя остановится в точке устойчивого равновесия. Если промежуточная часть в момент срабатывания компаратора 12 fa 6- &г , то на участке торможения действует штатная диаграмма до отработки последнего импульса уставки. Элементы памяти 26 и 27 остаются в обнуленном состоянии. В общем случае диапазон частоты от f. до fniny. делится на ггоддиапазон с дискретностью f, , 2ff , ,..., j (где значение частоты тормоения без выбега; n f ffnjf ). Число огических компарптсфоп должнс сответствовать числу значений частот азбмонмя л,и.иг;г)(1нл. Значению частоты inio. ставится в соответствие значение уставки, запи сываемой в логический компаратор 12, начиная с которой должно разрешаться включение блока 30 на противовключение по сигналу с дешифратора 22. Устройство позволяет осуществить торможение на максимальной частоте работы шагового привода (достигнутой в результате программируемого разгона) -при отработке на ней всей части уставки, оставшейся неотработанной в момент достижения ,„д, при этом торможение осуществляется без выбега. За счет этого сокращается время на отработку уставки, что обеспечивает повьпиение быстродействия шагового привода.

Таблица, истинности Влока протиВо8клю1 ения

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU268295A1 | |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-08-15—Публикация

1983-04-18—Подача