/СК

дд adpecH ie шины

шины doHHkix

линии 1/йравления

(Л

со со

00 00

Фи.1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах программного управления станками.

Цель изобретения - повышение быстродействия.

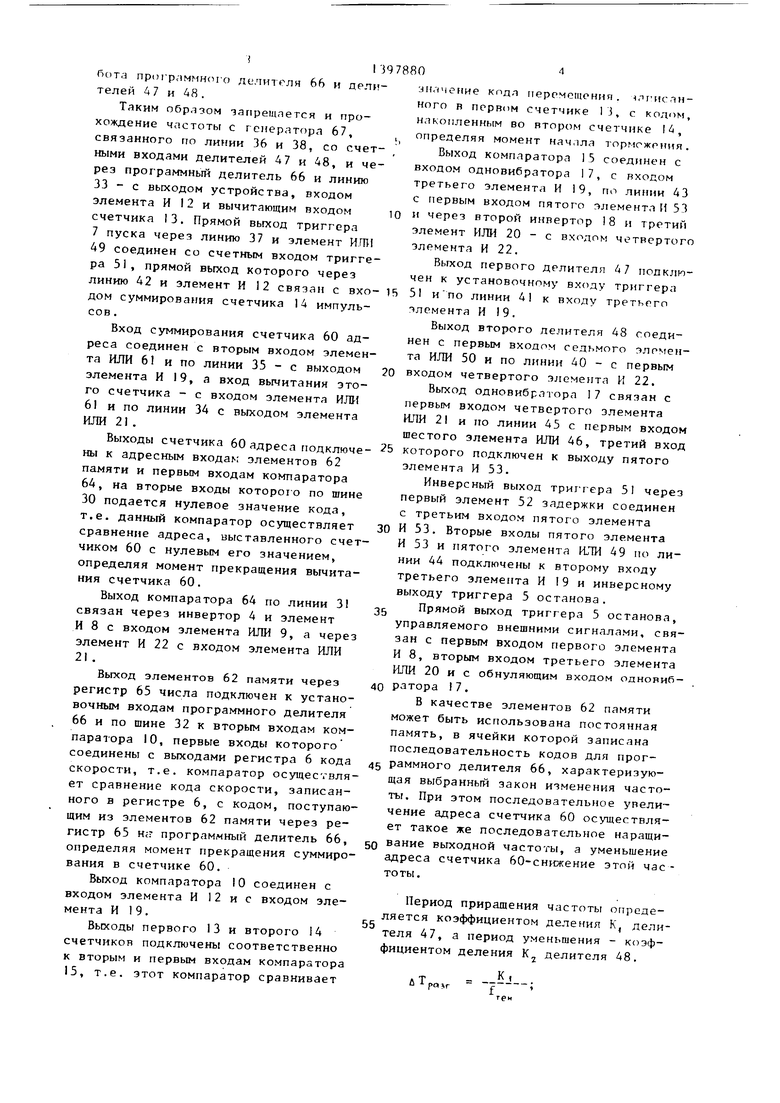

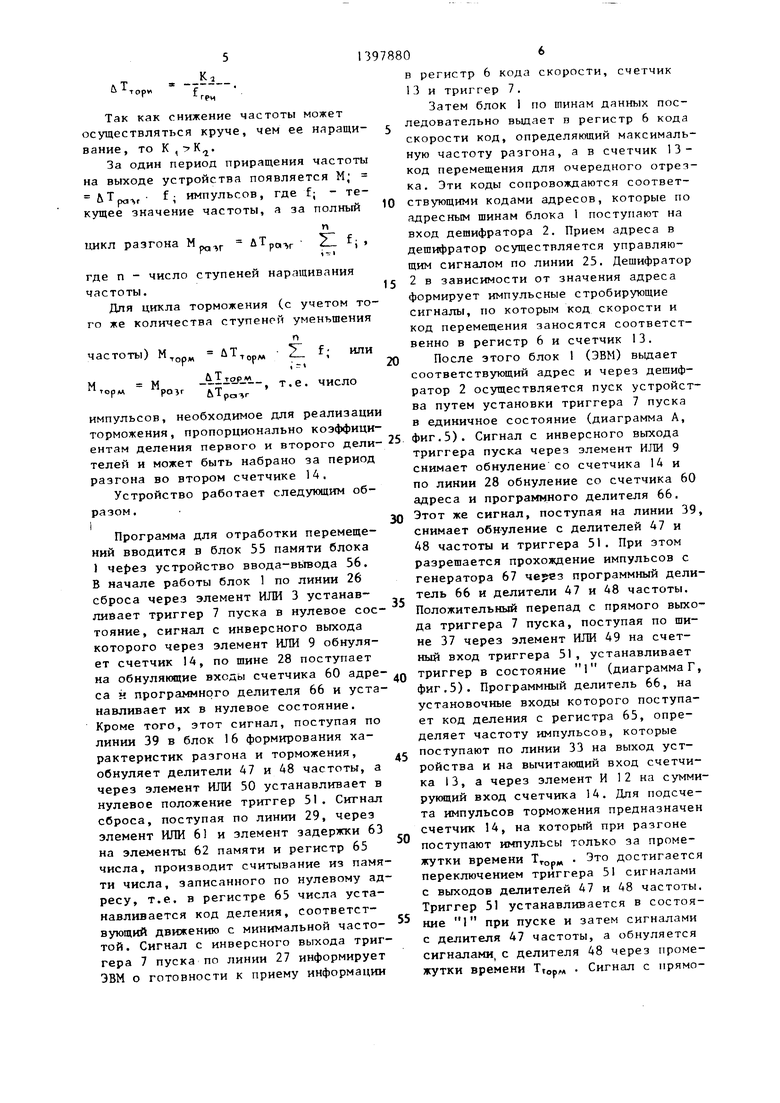

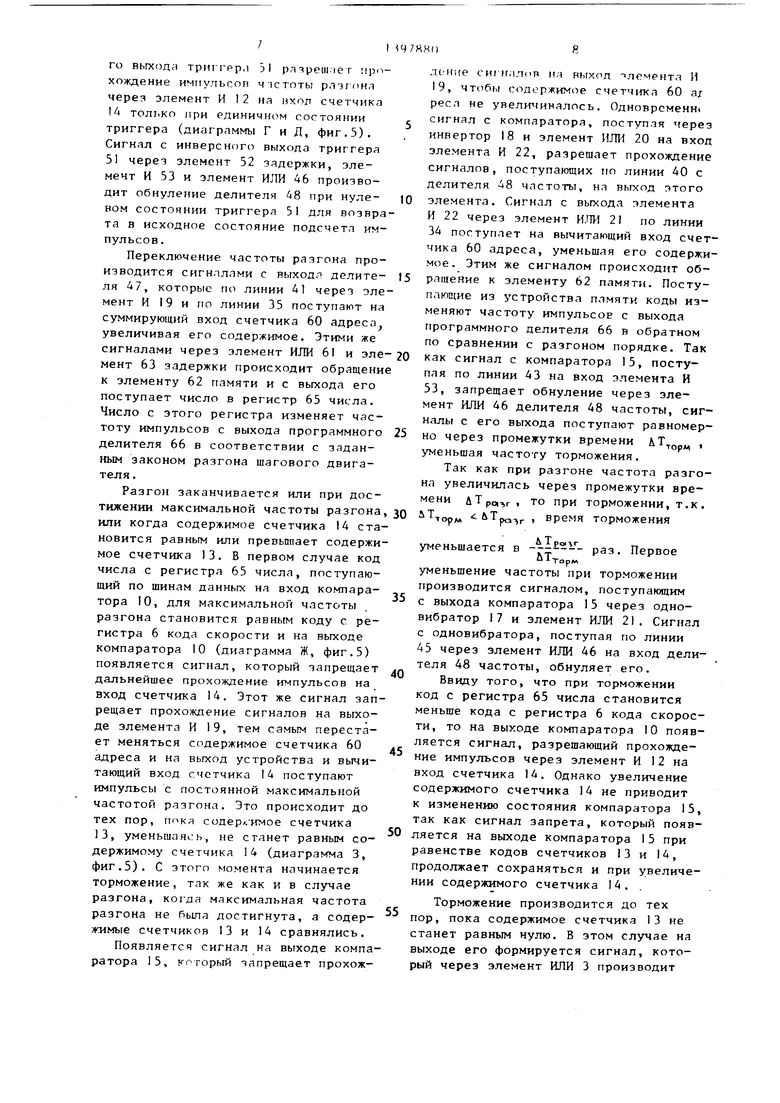

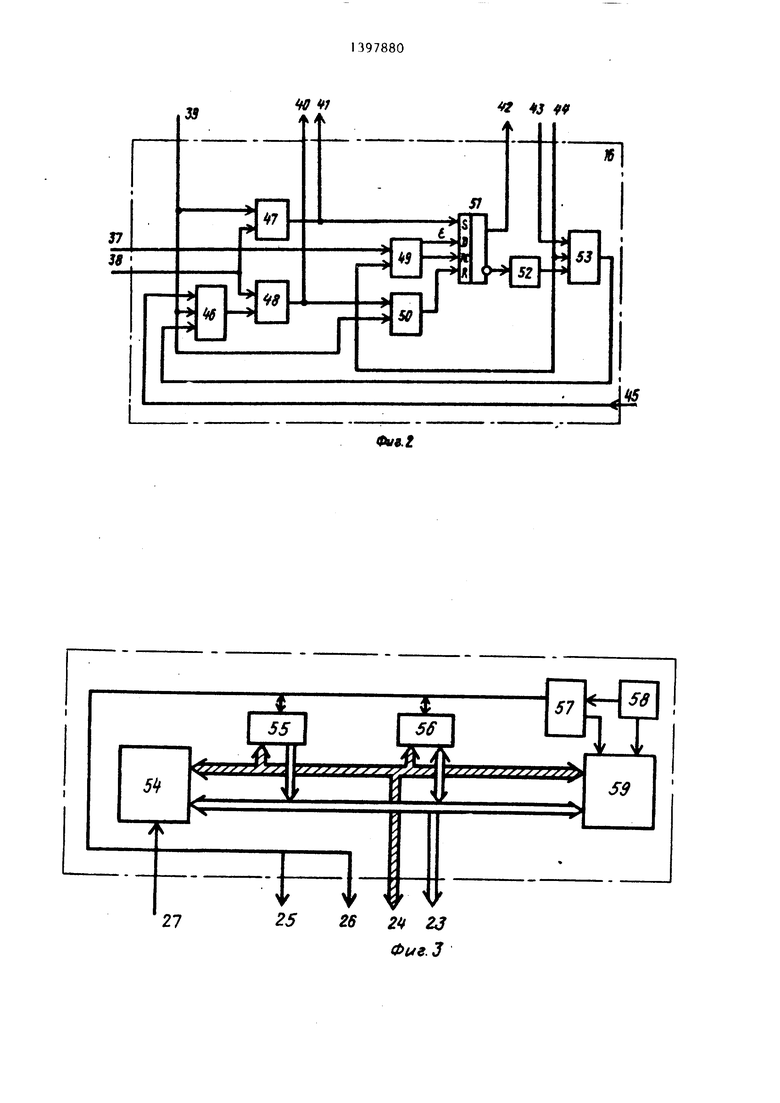

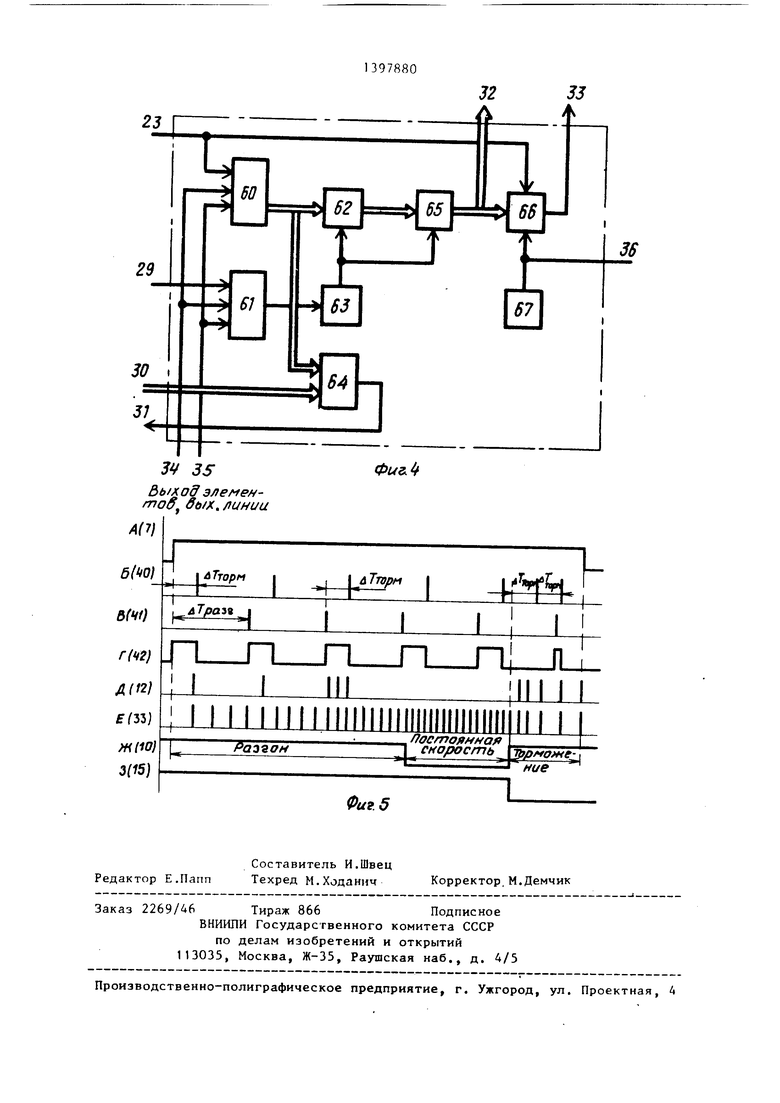

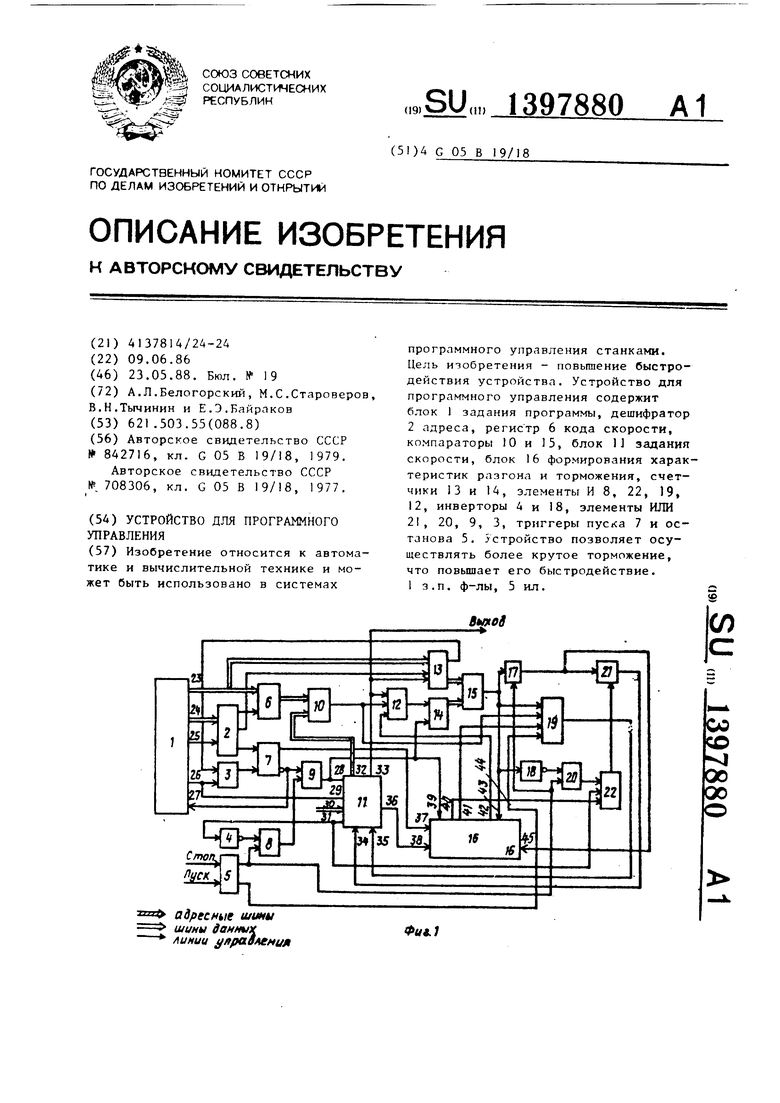

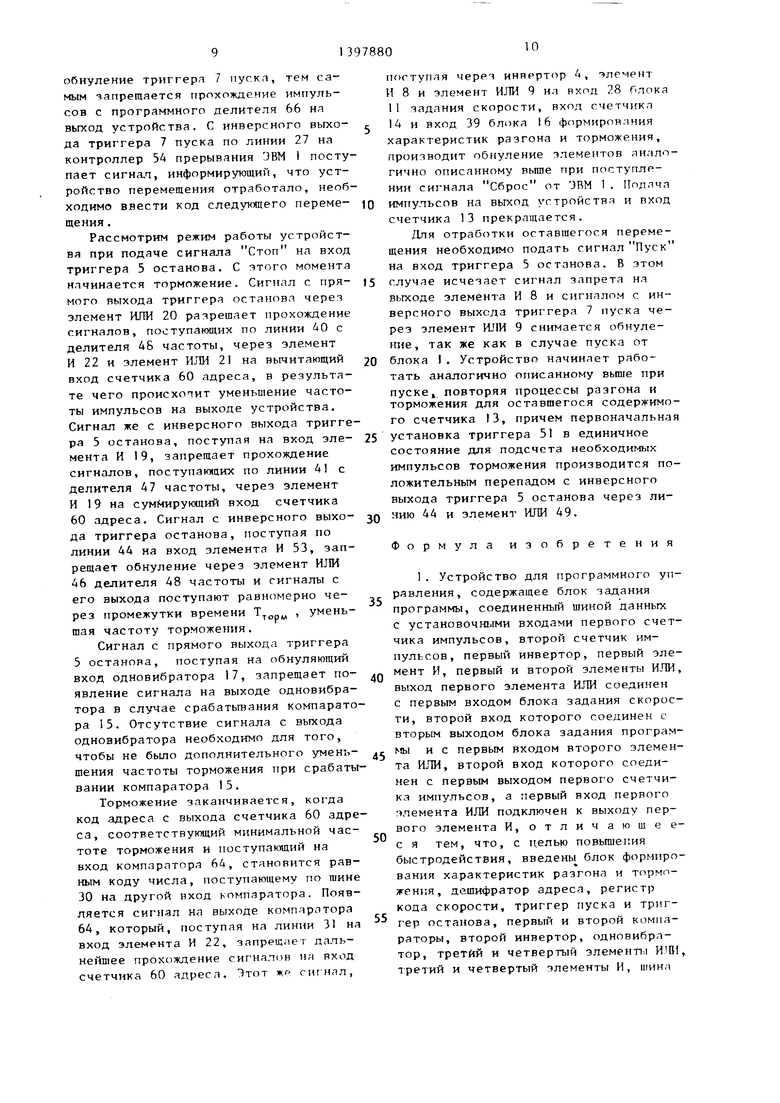

На фиг.1 представлена функциональная схема устройства для программного управления; на фиг.2 - функцио- нальная схема блока формирования характеристики разгона и торможения; на фиг.З - функциональная схема ЭВМ; на фиг.4 - функциональная схема блока задания скорости; на фиг.З - вре- менные диаграммы работы предлагаемого устройства.

Устройство содержит блок 1 задания программы (ЭВМ), дешифратор 2 адреса, элемент ИЛИ 3, инвертор 4, триггер 5 останова, регистр 6 кода скорости, триггер 7 пуска, элемент И 8, элемент ИЛИ 9, компаратор 10, блок 11 задания скорости, элемент И 12, счетчик 13 импульсов, счетчик 14 импульсов, компаратор 15, блок 16 формирования характеристик разгона и торможения, одновибратор 17, инвертор 18, элемент И 1 9, элементы ИЛИ 20 и 21 и элемент И 22, шины 23-27 свя- зи с блоком задания программ, линии 28-36 связи с блоком задания скорости, линии 37-45 связи с блоком 16..

Блок формирования характеристик разгона и торможения (фиг.2) содержит элемент ИЛИ 46, делители 47 и 48 частоты, элементы ИЛИ 49 и 30, триггер 31, элемент 32 задержки, элемент И 53.

Блок задания программы (фиг.З) со- держит контроллер 34 прерывания, блок 33 памяти, устройство 36 ввода- вывода, системный контроллер 37 ЭВМ, тактовый генератор 38, центральный процессор 39, шину 23 данных, адрес- ную шину 24, шину 23 управления, линию 26 сброса и линию 27 прерывания.

Блок задания скорости (фиг.4) содержит счетчик 60 адреса, восьмой элемент ИЛИ 61, элементы 62 памяти, второй элемент 63 задержки, третий 64 компаратор, регистр 63 числа, программный делитель 66, генератор 67 импульсов, входные линии 28, 29, 34 и 33, шины 30 и 32 данных, входные линии 31, 33 и 36.

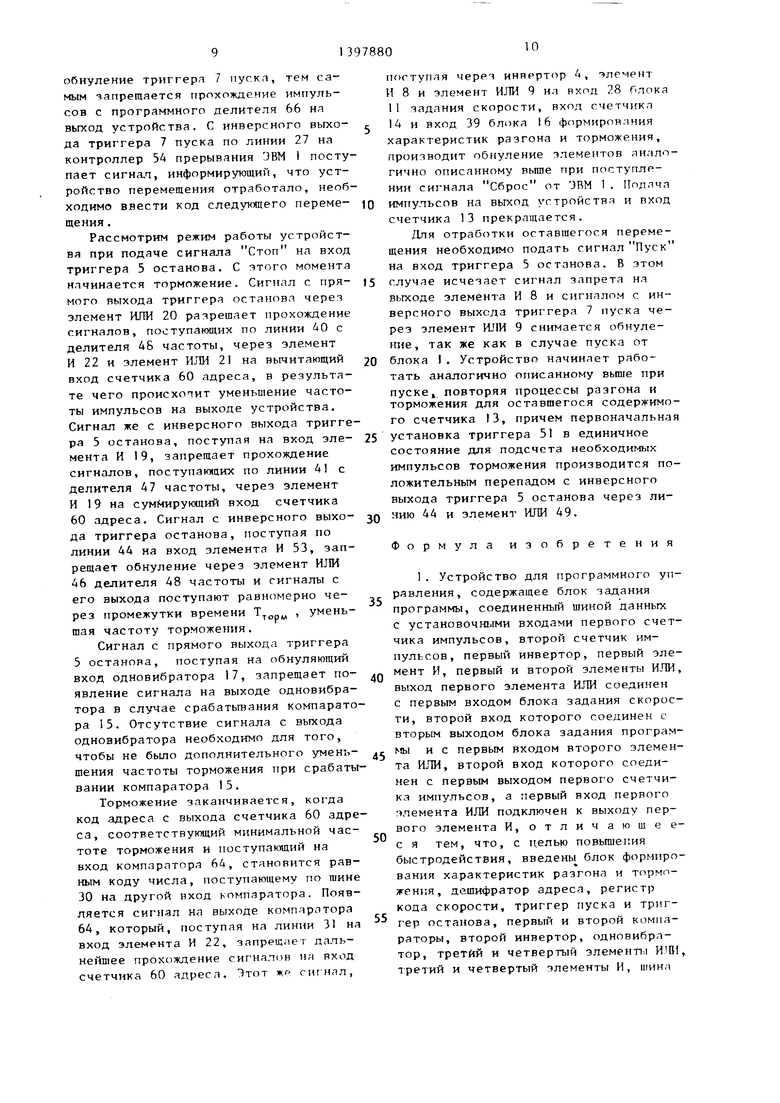

На фиг.З приведены временные диаграммы импульсов: А - на прямом выходе триггера 7 пуска, Е,Б,В,Г - соответственно на выходных линиях 33,40, 41,42; Д - на выходе второго элемента И 12; Ж,3 - соответственно на выходах компараторов 10 и 15.

Дешифратор 2 соединен с адресной шиной 24 и линией 23 управления с блоком 1 задания программы (ЭВМ). В зависимости от кода адреса дешифратор выдает сигнал на одном из трех своих выходов, соединенных соответственно со стробирующим входом регистра 6 кода скорости, подобным входом первого счетчика 13 и установочным входом триггера 7 пуска. Входы регистра 6 кода скорости и установочные входы первого счетчика I3 объединены с шиной 23. Таким образом, дешифратор 2 в соответствии со значением адреса, поступающего из блока 1 осуществляет запись информации или в регистр 6 кода скорости, или в первый счетчик 13, либо взводит триггер 7 пуска.

Блок 1 задания программы по линии 26 сброса через элемент ИЛИ 3 связан с обнуляющим входом триггера 7 пуска, а через линию 29, элемент ИЛИ 6 и элемент 63 задержки с входом считывания элементов 62 памяти и стробирующим входом регистра 63 числа. Вход элемента ИЛИ 3 подключен к выходу обратного переноса счетчика 13, т.е. при вьщаче сигнала Сброс с блока 1 или по окончании вычитания счетчика 13 осуществляется обнуление триггера 7 пуска. Инверсный выход триггера пуска 7 по линии 27 связан с блоком 1 и при положительном своем уровне информирует его о готовности устройства принять новые значения кодов скорости и перемещения в регистр 6 и счетчик 13 для осуществления следующего перемещения. Этот же инверсный выход триггера пуска связан с входом элемента ИЛИ 9, выход которого соединен с обнуляющим входом счетчика 14, по линии 28 - с обнуляющими входами счетчика 60 адреса и программного делителя 66, а по линии 39 - с обнуляющим входом делителя 47 и входами элементов ИЛИ 46 и 30, выходы которых подключены соответственно к обнуляющим входам делителя 48 и триггера 31, т.е. при сброшенном состоянии триггера 7 пуска в исходное нулевое состояние устанавливаются и счетчик 14, счетчик 60 адреса, триггер 5 и запрещается раПота пpo|p -lм H(Чo делителя 66 и дели телей 47 и 48.

Таким обрляом запрещпется и прохождение частоты с гсиерлторя 67, связанного по линии 36 и 38, со счет ными входами делителей 47 и 48, и че рез программный делитель 66 и линию 33 - с выходом устройства, входом элемента И I2 и вычитающим входом счетчика 13. Прямой выход триггера 7 пуска через линию 37 и элемент ИШ1 49 соединен со счетным входом тригге ра 51, прямой выход которого через линию 42 и элемент И 12 связан с вхо дом суммирования счетчика 14 импульсов .

Вход суммирования счетчика 60 адреса соединен с вторым входом элемен та ИЛИ 61 и по линии 35 - с выходом элемента И 19, а вход вычитания этого счетчика - с входом элемента ИЛИ 61 и по линии 34 с выходом элемента ИЛИ 21.

Выходы счетчика 60 адреса подключе ны к адресным входам элементов 62 памяти и первым входам компаратора 64, иа вторые входы которох о по шине 30 подается нулевое значение кода, т.е. данный компаратор осуществляет сравнение адреса, выставленного счет чиком 60 с нулевым его значением, определяя момент прекращения вычитания счетчика 60.

Выход компаратора 64 по линии 31 связан через инвертор 4 и элемент И 8 с входом элемента ИЛИ 9, а через элемент И 22 с входом элемента ИЛИ 21.

Выход элементов 62 памяти через регистр 65 числа подключен к установочным входам программного делителя 66 и по шине 32 к вторым входам компаратора 10, первые входы которого соединены с выходами регистра 6 кода скорости, т.е. компаратор осуществляет сравнение кода скорости, записанного в регистре 6, с кодом, поступающим из элементов 62 памяти через регистр 65 н; программный делитель 66, определяя момент прекращения суммирования в счетчике 60.

Выход компаратора 10 соединен с входом элемента И 12 и с входом элемента И 19.

Выходы первого 13 и второго 14 счетчиков подключены соответственно к вторым и первым входам компаратора 15, т.е. этот компаратор сравнивает

7880

значение кодл перемсщонип. 1Лг испм- ного в первом счетчике 13, с ко/чом, накопленным во втором счетчике 14,

J определяя момент начлла тормгжрния.

, Выход компаратора 15 соединен с

входом одновибратора 17, с входом третьего элемента И 19, по линии 43 с первым входом пятого элемента И 53 10 и через второй инвертор 18 и третий элемент ИЛИ 20 - с входом четвертого элемента И 22.

Выход первого делителя 47 подключен к установочному входу триггера

15 51 и по линии 41 к входу третьего

элемента И 19.

Выход второго делителя 48 соединен с первым входом седьмого элпмен- та ИЛИ 50 и по линии 40 - с первым

20 входом четвертого элемента И 22.

Выход одновибрптора I7 связан с первым входом четвертого элемента ИЛИ 21 и по линии 45 с первым входом шестого элемента ИЛИ 46, третий вход

25 которого подключен к выходу пятого элемента И 53.

Инверсный выход тригтера 51 через первый элемент 52 задержки соединен с третьим входом пятого элемента

30 И 53. Вторые входы пятого элемента И 53 и пятого элемента ИЛИ 49 по линии 44 подключены к второму входу третьего элемента И 19 и инверсному выходу триггера 5 останова.

25 Прямой выход триггера 5 останова, управляемого внешними сигналами, связан с первым входом первого элемента И 8, вторым входом третьего элемента ИЛИ 20 и с обнуляющим входом олиовиб40 ратора 17.

В качестве элементов 62 памяти может быть использована постоянная память, в ячейки которой записана последовательность кодов для прог45 раммного делителя 66, характеризующая выбранный закон изменения частоты. При этом последовательное увеличение адреса счетчика 60 осуществляет такое же последовательное наращи5Q вание выходной частоты, а уменьшение адреса счетчика 60-снюкение этой частоты.

55

Период приращения частоты определяется коэффициентом деления К, делителя 47, а период уменьшения - коэффициентом деления К делителя 48.

- К| .

йТ

Л Т,

Ki

ори

гри

Так как снижение частоты может осуществляться круче, чем ее наращивание , то К , т- К,

За один период приращения частоты на выходе устройства появляется М;

ЛТралг- i импульсов, ГДе f; - Твкущее значение частоты, а за полный

цикл разгона Мр ЛТро,где п - число ступеней наращивания частоты.

Для цикла торможения (с учетом того же количества ступеней уменьшения

г частоты) М

торм розг

импульсов, необходимое для реализации торможения, пропорционально коэффициентам деления первого и второго делителей и может быть набрано за период разгона во втором счетчике 14.

Устройство работает следующим образом. I

Программа для отработки перемещений вводится в блок 55 памяти блока 1 через устройство ввода-вЬгеода 56. В начале работы блок 1 по линии 26 сброса через элемент ИЛИ 3 устанавливает триггер 7 пуска в нулевое состояние, сигнал с инверсного выхода которого через элемент ИЛИ 9 обнуляет счетчик 14, по шине 28 поступает на обнуляющие входы счетчика 60 адреса н программного делителя 66 и устанавливает их в нулевое состояние. Кроме того, этот сигнал, поступая по линии 39 в блок 16 формирования характеристик разгона и торможения, обнуляет делители 47 и 48 частоты, а через элемент ИЛИ 50 устанавливает в нулевое положение триггер 51. Сигнал сброса, поступая по линии 29, через элемент ИЛИ 61 и элемент задержки 63 на элементы 62 памяти и регистр 65 числа, производит считывание из памяти числа, записанного по нулевому адресу, т.е. в регистре 65 числа устанавливается код деления, соответствующий движению с минимальной частотой. Сигнал с инверсного выхода триггера 7 пуска по линии 27 информирует ЭВМ о готовности к приему информации

10

15

20

25

30

35

40

45

50

55

в регистр 6 кода скорости, счетчик 13 и триггер 7.

Затем блок 1 по шинам данных последовательно выдает п регистр 6 кода скорости код, определяющий максимальную частоту разгона, а в счетчик 13- код перемещения для очередного отрезка. Эти коды сопровождаются соответствующими кодами адресов, которые по адресным шинам блока 1 поступают на вход дешифратора 2. Прием адреса в дешифратор осуществляется управляющим сигналом по линии 25. Дешифратор 2 в зависимости от значения адреса формирует импульсные стробирующие сигналы, по которым код скорости и код перемещения заносятся соответственно в регистр 6 и счетчик 13.

После этого блок 1 (ЭВМ) выдает соответствующий адрес и через дешифратор 2 осуществляется пуск устройства путем установки триггера 7 пуска в единичное состояние (диаграмма А, фиг.5). Сигнал с инверсного выхода триггера пуска через элемент ИЛИ 9 снимает обнуление со счетчика 14 и по линии 28 обнуление со счетчика 60 адреса и программного делителя 66. Этот же сигнал, поступая на линии 39, снимает обнуление с делителей 47 и 48 частоты и триггера 51. При этом разрешается прохождение импульсов с генератора 67 через программный делитель 66 и делители 47 и 48 частоты. Положительный перепад с прямого выхода триггера 7 пуска, поступая по шине 37 через элемент ИЛИ 49 на счетный вход триггера 51, устанавливает триггер в состояние 1 (диаграмма Г, фиг.5). Программный делитель 66, на установочные входы которого поступает код деления с регистра 65, определяет частоту импульсов, которые поступают по линии 33 на выход устройства и на вычитающий вход счетчика 13, а через элемент И 12 на суммирующий вход счетчика 14. Для подсчета импульсов торможения предназначен счетчик 14, на который при разгоне поступают импульсы только за промежутки времени Это достигается переключением триггера 51 сигналами с выходов делителей 47 и 48 частоты. Триггер 51 устанавливается в состояние 1 при пуске и затем сигналами с делителя 47 частоты, а обнуляется сигналами, с делителя 48 через промежутки времени Т,ор„ . Сигнал с прямого выхсзда триггер.1 31 раэрешмег прохождение импульсов Ч1СТОТЫ р.ТЗГОНЛ

через элемент И 12 пя нхол счетчика 14 только при единичном состоянии триггера (диаграм Г и Д, фиг.5). Сигнал с инверсного выхода триггера 51 через элемент 52 задержки, элемент И 53 и элемент ИЛИ 46 производит обнуление делителя 48 при нулевом состоянии триггера 51 для возврата в исходное состояние подсчета импульсов .

Переключение частоты разгона производится сигналами с выходя делителя 47, которые по линии 41 через элемент И 19 и по линии 35 поступают на суммирующий вход счетчика 60 адреса увеличивая его содержимое. Этими же сигналами через элемент ИЛИ 61 и элемент 63 задержки происходит обращени к элементу 62 памяти и с выхода его поступает число в регистр 65 числа. Число с этого регистра изменяет частоту импульсов с выхода программного делителя 66 в соответствии с заданным законом разгона шагового двигателя .

Разгон заканчивается или при достижении максимальной частоты разгона или когда содержимое счетчика 14 становится равным или превьппает содержимое счетчика 13. В первом случае код числа с регистра 65 числа, поступающий по шинам данных на вход компаратора 10, для максимальной частоты разгона становится равным коду с регистра 6 кода скорости и на выходе компаратора 10 (диаграмма Ж, фиг.5) появляется сигнал, который запрещает дальнейшее прохождение импульсов на вход счетчика 14. Этот же сигнал запрещает прохождение сигналов на выходе элемента И 19, тем самым перестает меняться содержимое счетчика 60 адреса и на выход устройства и вычитающий вход счетчика 14 поступают импульсы с постоянной максимальной частотой разгона. Это происходит до тех пор, пока содер/. имое счетчика 13, уменьшаясь, не станет равным содержимому счетчика 14 (диаграмма 3, фиг.5). С этого момента начинается торможение, так же как и в случае разгона, когда максимальная частота разгона не была достигнута, а содержимые счетчиков 13 и 14 сравнялись.

Появляется сигнал на выходе компаратора 15, который запрещает прохож-

0

5

0

5

0

5

0

5

0

5

торм

Л1МИ(е см1 И;1Л( р и,ч выход элемента И 19, чтобы содержимое счетчгжа 60 а/ реса не увеличивалось, Одновременн сигнал с компаратора, поступая через инвертор 18 и элемент ИЛИ 20 на вход элемента И 22, разрешает прохождение сигналов, поступающих по линии 40 с делителя 48 частоты, на выход этого элемента. Сигнал с выхода элемента И 22 через элемент И.Ш-1 21 по линии 34 поступает на вычитающий вход счетчика 60 адреса, уменьшая его содержимое. Этим же сигналом происходит обращение к элементу 62 памяти. Поступающие из устройства памяти коды изменяют частоту импульсов с выхода программного делителя 66 в обратном по сравнении с разгоном порядке. Так как сигнал с компаратора 15, поступая по линии 43 на вход элемента И 53, запрещает обнуление через элемент ИЛИ 46 делителя 48 частоты, сигналы с его выхода поступают равномерно через промежутки времени уменьшая частоту торможения.

Так как при разгоне частота разгона увеличилась через промежутки времени йТро,,г. то при торможении, т. к . , 1ЛТра , время торможения

уменьшается в раз. Первое

йТтарм

уменьшение частоты при торможении производится сигналом, поступающим с выхода компаратора 15 через одно- вибратор 17 и элемент ИЛИ 21. Сигнзл с одновибратора, поступая по линии 45 через элемент ИЛИ 46 на вход делителя 48 частоты, обнуляет его.

Ввиду того, что при торможении код с регистра 65 числа становится меньше кода с регистра 6 кода скорости, то на выходе компаратора 10 появляется сигнал, разрешающий прохояоде- ние импульсов через элемент И 12 на вход счетчика 14. Однако увеличение содержимого счетчика 14 не приводит к изменению состояния компаратора 15, так как сигнал запрета, который появляется на выходе компаратора I5 при равенстве кодов счетчиков 13 и 14, продолжает сохраняться и при увеличении содержимого счетчика 14. .

Торможение производится до тех пор, пока содержимое счетчика 13 не станет равным нулю. В этом случае на выходе его формируется сигнал, который через элемент ИЛИ 3 производит

обнуление триггера 7 пускл, тем самым запрещается прохождение импульсов с программного делителя 66 на выход устройства. С инверсного вьтхо- да триггера 7 пуска по линии 27 на контроллер 54 прерывания ЭВМ I поступает сигнап, информирующий, что устройство перемещения отработало, необходимо ввести код следующего переме- щения.

Рассмотрим режим работы устройства при подаче сигнала Стоп на вход триггера 5 останова. С этого момента начинается торможение. Сигнал с пря- мого выхода триггера останова через элемент ИЛИ 20 разрешает прохождение сигналов, поступающих по линии с делителя 48 частоты, через элемент И 22 и элемент ИЛИ 21 на вычитающий вход счетчика 60 адреса, в результате чего происходит уменьщение частоты импульсов на выходе устройства, Сигнал же с инверсного выхода триггера 5 останова, поступая на вход эле- мента И 19, запрещает прохождение сигналов, поступающих по линии 41 с делителя 47 частоты, через элемент И 19 на суммирующий вход счетчика 60 адреса. Сигнал с инверсного выхо- да триггера останова, поступая по линии 44 на вход элемента И 53, запрещает обнуление через элемент ИЛИ 46 делителя 48 частоты и сигналы с его выхода поступают равномерно через промежутки времени Т , умень- щая частоту торможения.

Сигнал с прямого выхода триггера 5 останова, поступая на обнуляющий вход одновибратора 17, запрещает по- явление сигнала на выходе одновибратора в случае срабатьгаания компаратора 15. Отсутствие сигнала с выхода одновибратора необходимо для того, чтобы не было дополнительного умень- шения частоты торможения при срабатывании компаратора 15.

Торможение заканчивается, когда код адреса с выхода счетчика 60 адреса, соответствующий минимальной частоте торможения и поступающий на вход компаратора 64, становится равным коду числа, поступающему по шине 30 на другой вход компаратора. Появляется сигнал на выходе компаратора 64, который, поступая на линии 31 на вход элемента И 22, запрещает дальнейшее прохождение сигналов на вход счетчика 60 адреса. Этот жр сигнал,

поступая череч инвертор 4, элемент И 8 и элемент ИЛИ 9 на вход 28 Гьтока 11 задания скорости, вход счетчика 14 и вход 39 блока 16 формирования характеристик разгона и торможения, производит обнуление элементов аналогично описанному вьщ1е при поступлении сигнала Сброс от JBM 1 . Подача импульсов на выход устройства и вход счетчика 13 прекращается.

Для отработки оставшегося перемещения необходимо подать сигнал Пуск на вход триггера 5 останова. В этом случае исчезает сигнал запрета на выходе элемента И В и сигналом с инверсного выхода триггера 7 пуска через элемент ИЛИ 9 снимается обнуление, так же как в случае пуска от блока I. Устройство начинает работать аналогично описанному выше при

пуске повторяя процессы разгона и торможения для оставшегося содержимого счетчика 13, причем первоначальная установка триггера 51 в единичное состояние для подсчета необходимых импульсов торможения производится положительным перепадом с инверсного выхода триггера 5 останова через линию 44 и элемент ИЛИ 49.

Формула изобретения

1. Устройство для программного управления, содержащее блок задания программы, соединенный шиной данных с установочными входами первого счетчика импульсов, второй счетчик импульсов, первый инвертор, первый элемент И, первый и второй элементы ИЛИ, выход первого элемента ИЛИ соединен с первым входом блока задания скорости, второй вход которого соединен с вторым выходом блока задания программы и с первым входом второго элемента ИЛИ, второй вход которого соединен с первым выходом первого счетчика импульсов, а первый вход первого элемента ИЛИ подключен к выходу первого элемента И, отличаюшее- с я тем, что, с целью повышения быстродействия, введены блок формирования характеристик разгона и торможения, дешифратор адреса, регистр кода скорости, триггер пуска и триггер останова, первый и второй компараторы, второй инвертор, одновибра- тор, третий и четвертый элемент, ИЛИ, третий и четвертый элементы И, шина

данных блока задания програг мы соединена с входами регистра кода скорости, адресные шины и выход управления - с соответствующими входами дешифратора адреса, первый выход которого соединен со стробирукяцим входом регистра кода, второй выход дешифратора адреса подключен к стробирующе- му входу первого счетчика импульсов, третий выход - к установочному входу триггера пуска, обнуляющий вход которого соединен с выходом второго элемента ИЛИ, прямой выход триггера пуска подключен к первому входу блока формирования характеристик разгона и торможения, второй вход - к выходу первого элемента ИЛИ и к первому входу второго счетчика импульсов, второй вход которого соединен с выходом второго элемента И, а выход - с первым входом первого компаратора, второй вход которого подключен к второму выходу первого счетчика импульсов а выход - к первому входу третьего элемента И, к первому входу одновиб- ратора, к третьему входу блока формирования характеристик разгона и торможения и через второй инвертор - к первому входу третьего элемента ИЛИ, второй вход которого соединен с вторым входом одновибратора, с первым входом первого элемента И и с прямым выходом триггера останова, инверсный выход которого подключен к второму входу третьего элемента И и к четвертому входу блока формирования характеристик разгона и торможения, пятый вход которого соединен с выходом одновибратора и с первым входом четвертого элемента ИЛИ, шестой вход - с выходом блока задания скорости, первый выход - с первым входом четвертого элемента И, второй выход - с третьим входом третьего элемента И, третий выход - с первым входом второго элемента И, второй вход которого подключен к второму Bbf ходу блока задания скорости, к третьему входу первого счетчика импульсов и к выходу устройства для прог- рам1чиого управления, третий вход второго элемента И соединен с четвертым входом третьего элемента И и с выходом второго компаратора, первый вход которого подключен к выходу регистра

o

5

0

5

0

5

0

S

0

5

кода скорости, второй вход - к третьему выходу блока задания скорости, четвертый выход которого через первый инвертор соединен с вторым входом первого элемента И и с вторым входом четвертого элемента И, третий вход которого подключен к выходу третьего элемента ИЛИ, выход четвертого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого подключен к третьему входу блока задания скорости, четвертый вход которого соединен с выходом треть его элемента И, инверсный выход триггера пуска соединен с вторым входом первого элемента ИЛИ и с входом блока задания программы.

2. Устройство по п.1, о т л и - чающееся тем, что блок формирования характеристик разгона и торможения содержит первый и второй делители частоты, пятый, шестой и седьмой элементы ИЛИ, пятый элемент И, триггер и первый элемент задержки, причем счетные входы первого и второго делителей соединены с шестым входом блока, первый вход пятого элемента ИЛИ связан с первым входом блока, первый вход пятого элемента И подключен к третьему входу блока, второй вход пятого элемента И связан с вторым входом пятого элемента ИЛИ и четвертым входом блока, первый вход шестого элемента ИЛИ соединен с пятым входом блока, вторые входы шестого и седьмого элементов ИЛИ и обнуляющий вход первого делителя объединены с вторым входом блока, обнуляющий вход второго делителя связан с выходом шестого элемента ИЛИ , третьим входом соединенного с выходом пятого элемента И, третий вход которого через первый элемент задержки подключен к инверсному выходу триггера, а выход второго делителя соединен с первым выходом блока и первым входом седьмого элемента ИЛИ, выход которого связан с обнуляющим входом триггера, счетным входом,подключенным к выходу пятого элемента ИЛИ, выход первого делителя соединен с вторым выходом блока и установочным входом триггера, прямой выход которого подключен к третьему выходу блока формирования характеристик разгона и торможения.

j 99

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство программного управления шаговыми двигателями | 1985 |

|

SU1320794A1 |

| Многоканальное устройство программного управления шаговыми двигателями | 1987 |

|

SU1481714A2 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1365342A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| Устройство для управления шаговым двигателем | 1987 |

|

SU1607071A1 |

| Устройство для управления перемоточным станком | 1982 |

|

SU1087594A1 |

| Устройство для программного управления разгоном и торможением двигателя | 1986 |

|

SU1314309A1 |

| Устройство для управления скоростными режимами перемоточного станка | 1984 |

|

SU1236037A1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного управления станками. Цель изобретения - повышение быстродействия устройства. Устройство для программного управления содержит блок 1 задания программы, дешифратор 2 адреса, регистр 6 кода скорости, компараторы 10 и 15, блок 1J задания скорости, блок 16 формирования характеристик разгона и торможения, счетчики 13 и 14, элементы ИВ, 22, 19, 12, инверторы 4 и 18, элементы ИЛИ 21, 20, 9, 3, триггеры пуска 7 и останова 5. Устройство позволяет осуществлять более крутое торможение, что повышает его быстродействие. 1 3.п. ф-лы, 5 ил.

27

2S 26 2 2J .J

| Устройство для программного управленияшАгОВыМи дВигАТЕляМи | 1979 |

|

SU842716A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1977 |

|

SU708306A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-05-23—Публикация

1986-06-09—Подача