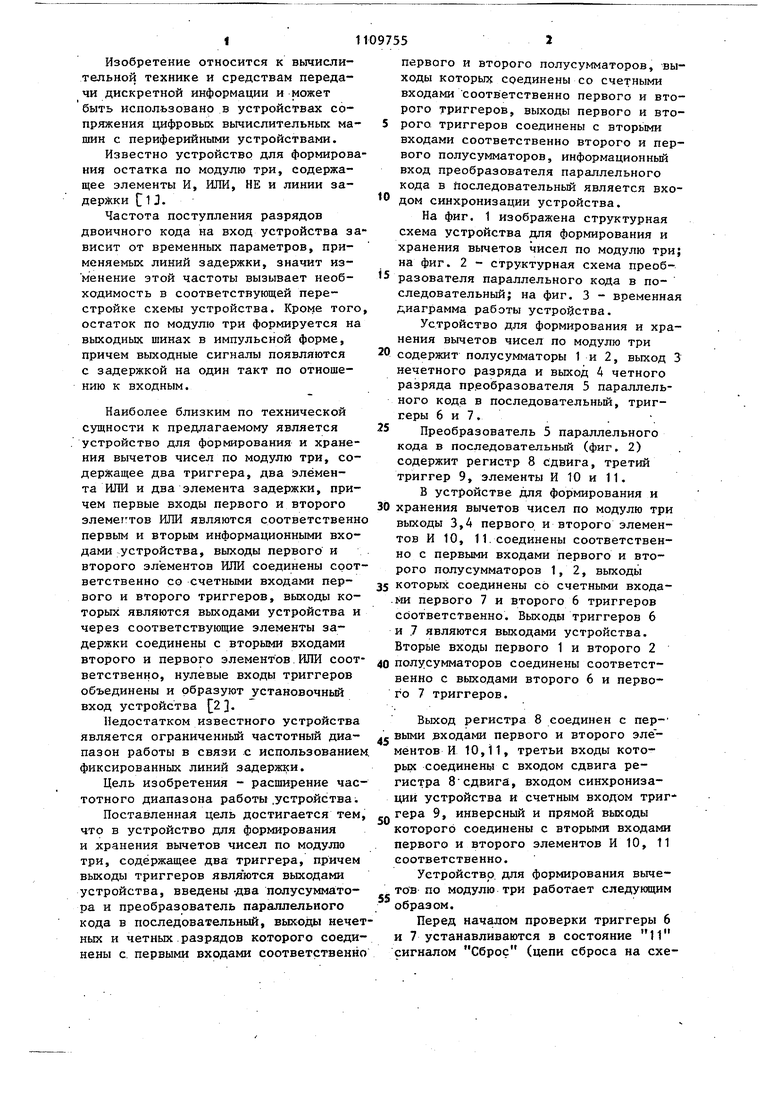

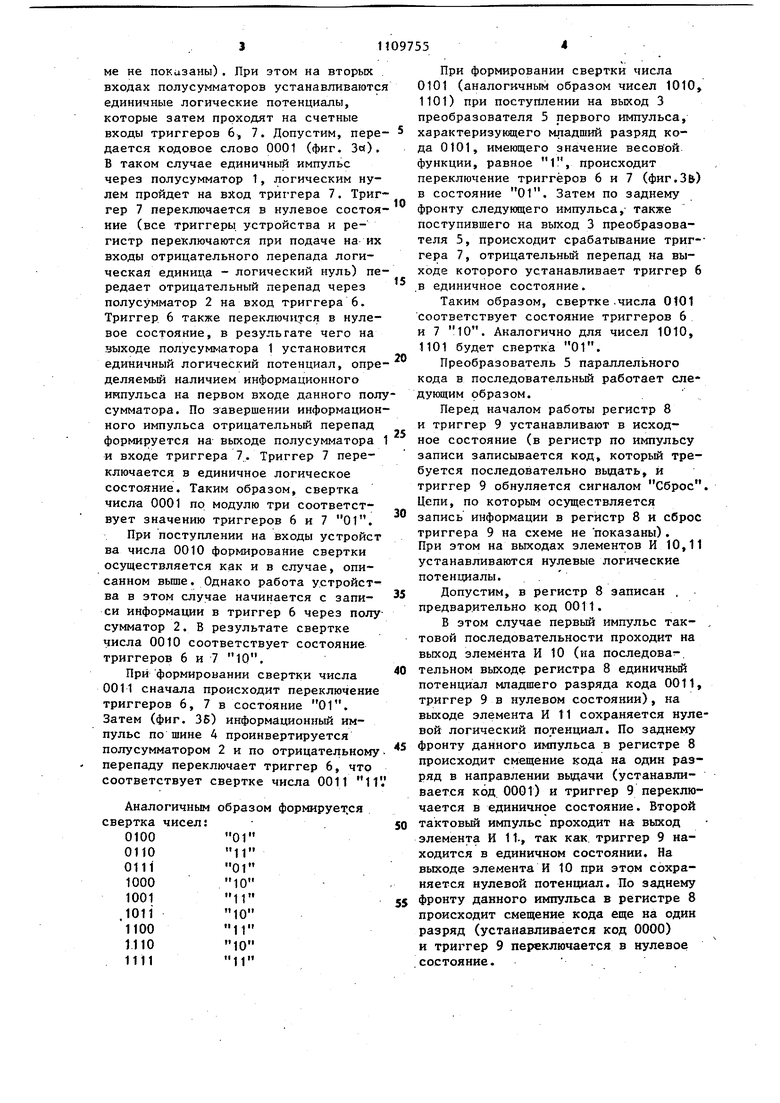

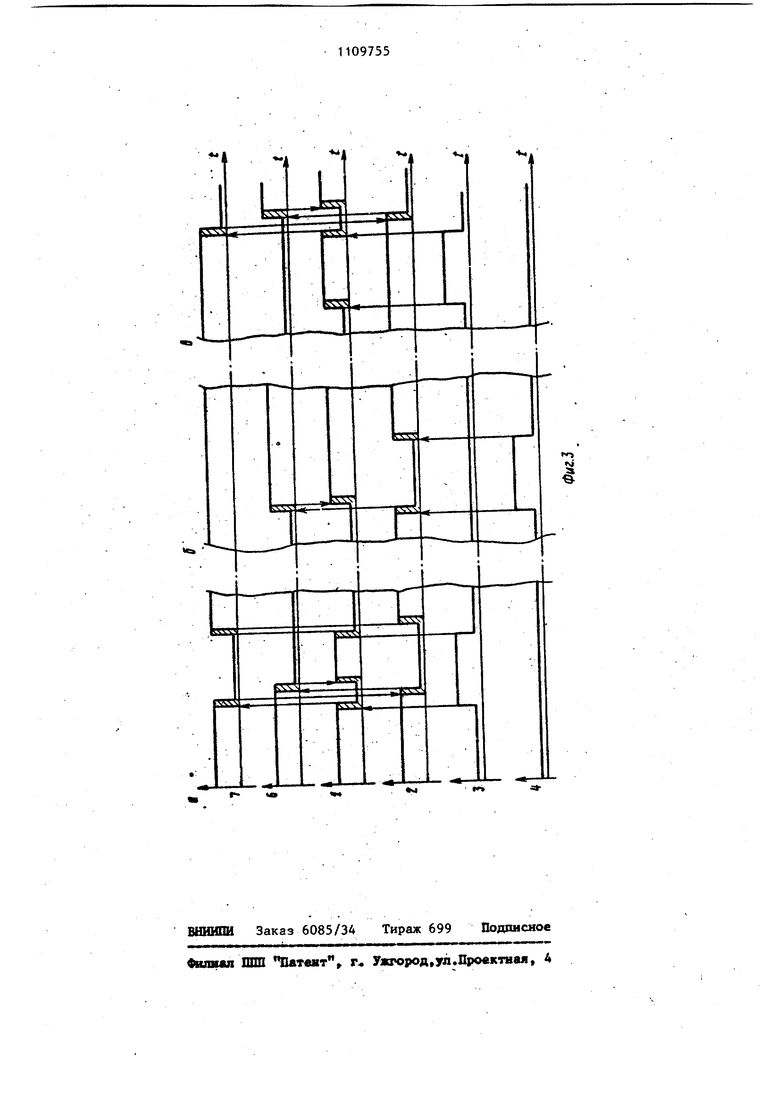

со ел ел Изобретение относится к вычислительной технике и средствам передачи дискретной информации и может быть использовано в устройствах сопряжения цифровых вычислительных машин с периферийньми устройствами. Известно устройство для формирова ния остатка по модулю три, содержащее элементы И, ИЛИ, НЕ и линии задержки Ci JЧастота поступления разрядов двоичного кода на вход устройства за висит от временных параметров, применяемых линий задержки, значит изменение этой частоты вызывает необходимость в соответствующей перестройке схемы устройства. Кроме того остаток по модулю три формируется на выходных шинах в импульсной форме, причем выходные сигналы появляются с задержкой на один такт по отношению к входным. Наиболее близким по технической сущности к предлагаемому является устройство для формирования и хранения вычетов чисел по модулю три, содержащее два триггера, два :элёмента ИЛИ и два элемента задержки, причем первые входы первого и второго элеметтов ИЛИ являются соответственн первым и вторым информационными входами устройства, выходы первого и второго элементов ИЛИ соединены соот ветственно со счетными входами первого и второго триггеров, выходы которых являются выходами устройства и через соответствующие элементы задержки соединены с вторыми входами второго и первого элементов.ИЛИ соот ветственно, нулевые входы триггеров объединены и образуют установочньй вход устройства 2. Недостатком известного устройства является ограниченньй частотный диапазон работы в связи .с использование фиксированных линий задержки. Цель изобретения - расширение час тотного диапазона работы .устройства; Поставленная цель достигается тем что в устройство для формирования и хранения вычетов чисел по модулю три, содержащее два триггера, причем выходы триггеров являются выходами устройства, введены -два полусумматора и преобразователь параллельного кода в последовательный, выходы нече ных и четных.разрядов которого соеди нены с. первыми входами соответственн первого и второго полусумматоров, выходы которых соединены со счетными входами соответственно первого и второго триггеров, выходы первого и второга триггеров соединены с вторыми входами соответственно второго и первого полусумматоров, информационньй вход преобразователя параллельного кода в Последовательный является входом синхронизации устройства. На фиг, 1 изображена структурная схема устройства для формирования и хранения вычетов чисел по модулю три; на фиг. 2 - структурная схема преобразователя параллельного кода в последовательный; на фиг. 3 - временная диаграмма работы устройства. Устройство для формирования и хранения вычетов чисел по модулю три содержит полусумматоры 1 и 2, выход 3 нечетного разряда и выход А четного разряда преобразователя 5 параллельного кода в последовательный, триггеры 6 и 7. Преобразователь 5 параллельного кода в последовательный (фиг. 2) содержит регистр 8 сдвига, третий триггер 9, элементы И 10 и 11. В устройстве для формирования и хранения вычетов чисел по модулю три выходы 3,4 первого и второго элементов И 10, 11. соединены соответственно с первыми входами первого и второго полусумматоров 1, 2, выходы которых соединены со счетными входами первого 7 и второго 6 триггеров соответственно. Выходы триггеров 6 и 7 являются выходами устройства. Вторые входы первого 1 и второго 2 полусумматоров соединены соответственно с выходами второго 6 и первого 7 триггеров. Выход регистра 8 соединен с первыми входами первого и второго элементов И 10,11, третьи входы которых соединены с входом сдвига регистра 8сдвига, входом синхронизации устройства и счетным входом триг гера 9, инверсный и прямой выходы которого соединены с вторыми входами первого и второго элементов И 10, 11 соответственно. Устройство, для формирования вычетов по модулю три работает следующим образом. Перед началом проверки триггеры 6 и 7 устанавливаются в состояние 11 сигналом Сброс (цепи сброса на схеме не показаны). При этом на вторых входах полусумматоров устанавливают единичные логические потенциалы, которые затем проходят на счетные входы триггеров 6, 7. Допустим, пере дается кодовое слово 0001 (фиг. 3«) В таком случае единичный импульс через полусумматор 1, логическим ну лем пройдет на вход триггера 7. Три гер 7 переключается в нулевое состоя ние (все триггеры, устройства и регистр переключаются при подаче на- их входы отрицательного перепада логическая единица - логический нуль) п редает отрицательный перепад через полусумматор 2 на вход триггера 6. Триггер 6 также переключится в нулевое состояние, в результате чего на выходе пoлyeyм aтopa 1 установится единичный логический потенциал, опре деляемый наличием информационного инпульса на первом входе данного пол сумматора. По завершении информацио ного импульса отрицательный перепад формируется на выходе полусумматора и входе триггера 7. Триггер 7 переключается в единичное логическое состояние. Таким образом, свертка числ-а 0001 по модулю три соответствует значению триггеров 6 и 7 01. При поступлении на входы устройст ва числа 0010 формирование свертки осуществляется как и в случае, описанном выше. Однако работа устройства в этом случае начинается с записи информации в триггер 6 через полу сумматор 2. В результате свертке числа 0010 соответствует состояние триггеров 6 и 7 10. При формировании свертки числа 0011 сначала происходит переключение триггеров 6, 7 в состояние 01. Затем (фиг. ЗБ) информационный импульс по шине 4 проинвертируется полусумматором 2 и по отрицательному перепаду переключает триггер 6, что соответствует свертке числа 0011 11 Аналогичнымобразом формирует.ся свертка чисел: 0100 01 0110 11 0111 01 1000 10 1001 11 1011 10 При формировании свертки числа 0101 (аналогичным образом чисел 1010, 1101) при поступлении на выход 3 преобразователя 5 первого импульса, характеризующего младший разряд кода 0101, имеющего значение весовой функции, равное 1, происходит переключение триггеров 6 и 7 (фиг.3&) в состояние 01. Затем по заднему фронту следующего импульса,- также поступившего на выход 3 преобразователя 5, происходит срабатывание триг-гера 7, отрицательный перепад на выходе которого устанавливает триггер 6 .в единичное состояние. Таким образом, свертке .числа 0101 соответствует состояние триггеров 6 и 7 10. Аналогично для чисел 1010, 1101 будет свертка 01. Преобразователь 5 параллельного кода в последовательный работает следующим рбразом.. Перед началом работы регистр 8 и триггер 9 устанавливают в исходное состояние (в регистр по импульсу записи записывается код, которьй требуется последовательно выдать, и триггер 9 обнуляется сигналом Сброс. Цепи, по которым осуществляется запись информации в регистр 8 и сброс триггера 9 на схеме не показаны). При этом на выходах элементов И 10,11 устанавливаются нулевые логические потенциалы. . Допустим, в регистр 8 записан , предварительно код 0011. В этом случае первый импульс тактовой последовательности проходит на вь1ход элемента И 10 (на последовав, тельном выходу регистра 8 единичный потенциал младшего разряда кода 0011, триггер 9 в нулевом состоянии), на выходе элемента И 11 сохраняется нулевой логический потенциал. По заднему фронту данного импульса в регистре 8 происходит смещение кода на один разряд в направлении выдачи (устанавливается код 0001) и триггер 9 переключается в единичное состояние. Второй тактовый импульс проходит на выход элемента И 11-, так как триггер 9 находится в единичном состоянии. На выходе элемента И 10 при этом сохраняется нулевой потенциал. По заднему фронту данного импульса в регистре 8 происходит смещение кода еще на один разряд (устаиавливается код 0000) и триггер 9 переключается в нулевое состояние. Два последующих импульса не изменя ют состояния преобразователя, так как в регистре 8 единичная информация передаваемого кода исчерпана, и на выходах элементов И 10, 11 сохраняются нулевые логические потенциалы. Таким образом, триггер 9, определяя четность передаваемого разряда информации регистра 8, обеспечивает соответствующее распределение единичной информации передаваемого кода йм115 пульсами на выходах нечетных 3 и четных 4 разрядов информации преобразователя 5... Таким образом, предлагаемое устройство для формирования и хранения вычетов чисел по модулю три без какихлибо доработок может быть использовано в устройствах сопряжения цифровых вычислительных машин с периферийными устройствами, работакядими на плавающих или переменных частотах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

| Устройство для формирования и храненияВычЕТОВ пО МОдулю ТРи | 1979 |

|

SU796849A1 |

| Устройство для формирования и хранения вычетов чисел по модулю три | 1973 |

|

SU473184A1 |

| Пересчетное устройство с контролем | 1984 |

|

SU1221653A2 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU293256A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ И ХРАНЕНИЯ ВЫЧЕТОВ ЧИСЕЛ ПО МОДУЛЮ ТРИ, содержащее два триггера, причем выходы триггеров являются выходами устройства, отличающе. е с я тем, что, с целью расширения частичГ.. него диапазона работы устройства, в него введены два полусумматора и преобразователь параллельного кода в последовательный, выходы нечетных и четнёк разрядов которого соединены с первыми входами соответственно первого и второго полусумматоров, выходы которьк соединены со счетными входами соответственно первого и второго триггеров, выходы первого и второго триггеров соединены с вторыми входами соответственно второго и первого полусумматоров, информационный вход преобразователя параллельного кода в последовательный является входом 3 синхронизации устройства. (Л 7... 8нмЛ1

ffi

Г

fo

ES

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ТРИ | 0 |

|

SU388265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования и хранения вычетов чисел по модулю три | 1973 |

|

SU473184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип) | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-13—Подача