1

Устройство относится к вычислительной технике и предназначено для использования в трактах передачи дискретной информации между цифровыми устройствами.

Цель изобретения повьшение дос товерности контроля.

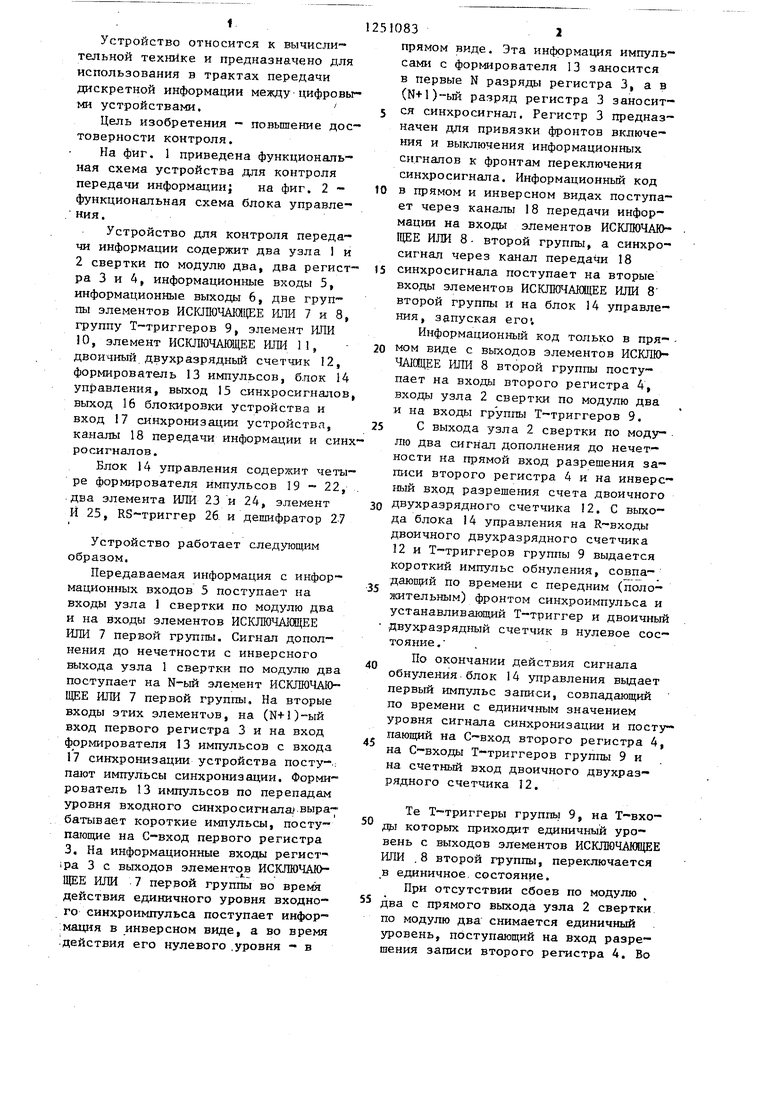

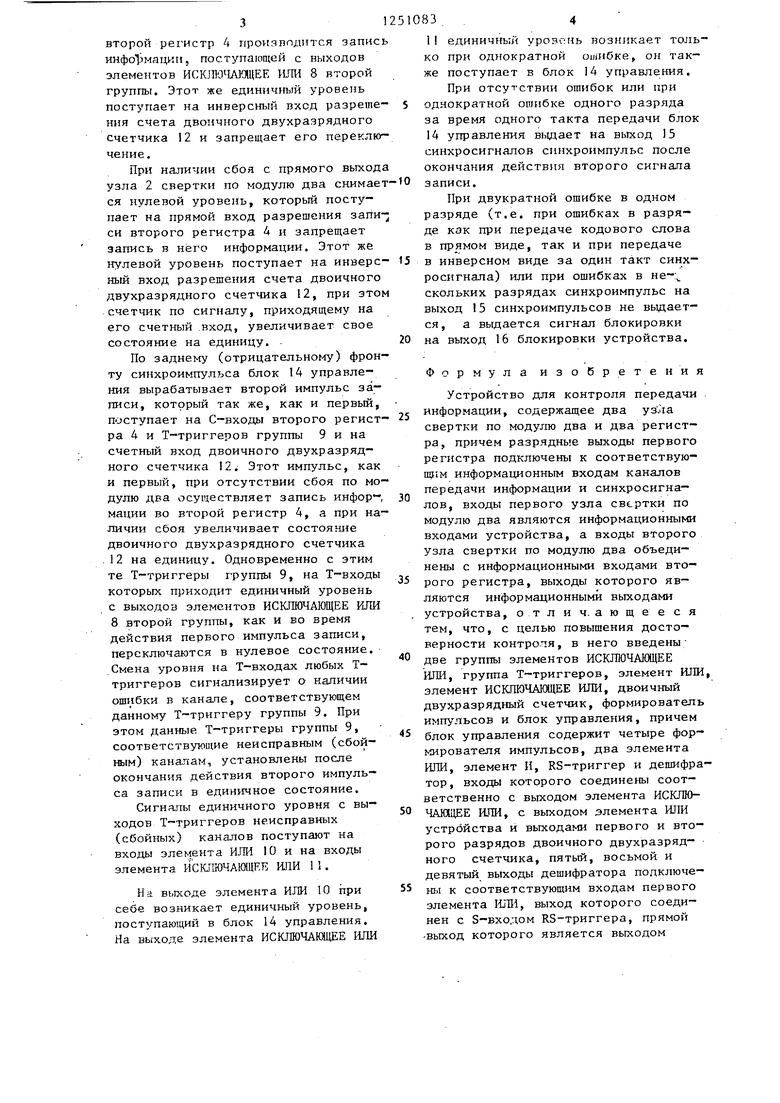

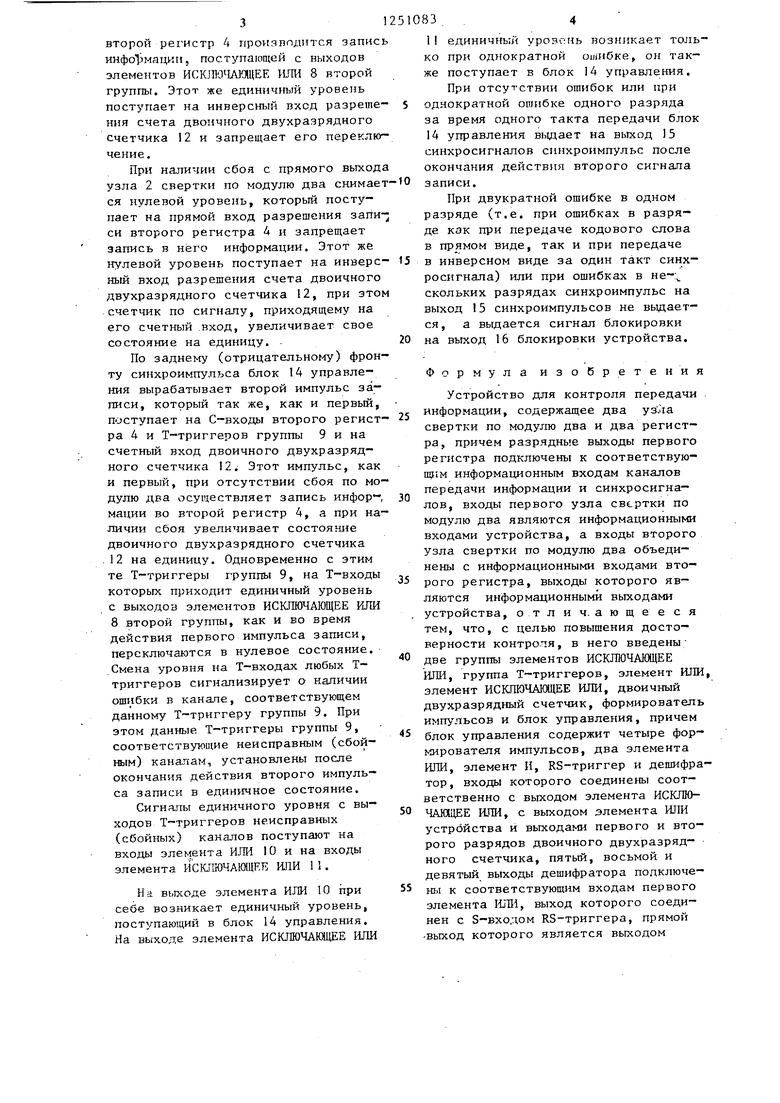

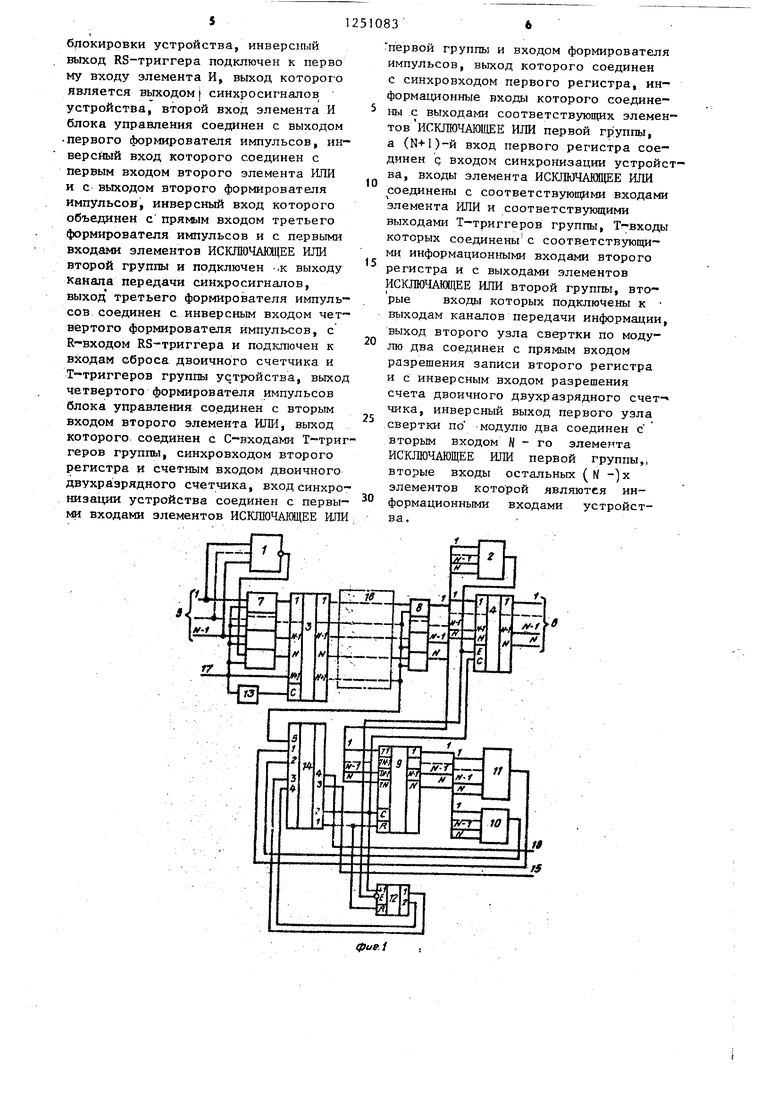

На фиг. 1 приведена функциональная схема устройства для контроля передачи информации; на фиг. 2 - функциональная схема блока управления .

Устройство для контроля передачи информации содержит два узла 1 и 2 свертки по модулю два, два регистра 3 и i, информационные входы 5, информационные выходы 6, две груп пы элементов ИСКЛЮЧАКШ ЕЕ ИЛИ 7 и 8, группу Т триггеров 9, элемент ИЛИ 10, элемент ИСКЛЮЧАЩЕЕ ИЛИ 11, двоичный двухразрядный счетчик 12, формирователь 13 импульсов, блок 14 управления, выход 15 синхросигналов выход 16 блокировки устройства и вход 17 синхронизации устройства, каналы 18 передачи информации и син росигналов.

Блок 14 управления содержит четыре формирователя Импульсов 19 22, -два элемента ШШ 23 и 24, элемент И 25, Е8 триггер 26 и дешифратор 27

Устройство работает следующим образом.

Передаваемая информация с информационных входов 5 поступает на входы узла 1 свертки по модулю два и на входы элементов ИСКЛЮЧАЩЕЕ ИЛИ 7 первой группы. Сигнал дополнения до нечетности с инверсного выхода узла 1 свертки по модулю два поступает на N-bA элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 первой группы. На вторые входы этих элементов, на (К+)-ый вход первого регистра 3 и на вход формирователя 13 импульсов с входа 17 синхронизации устройства посту-.: пают имтгульсы синхронизации. Формирователь 13 импульсов по перепадам уровня входного синхросигнала/ вырабатывает короткие импульсы, поступающие на С-вход первого регистра 3. На информационные входы регист- ipa 3 с выходов элементо в ИСКЛЮЧАЮЩЕЕ ИЛИ 7 первой группы во вреин действия единичного уровня входного синхроимпульса поступает информация в инверсном виде, а во время действия его нулевого .уровня - в

510832

прямом виде. Эта информация импульсами с формирователя 13 заносится в первые N разряды регистра 3, а в (N+O-brii разряд регистра 3 заносит5 ся синхросигнал. Регистр 3 предназначен для привязки фронтов включения и выключения информационных сигналов к фронтам переключения синхросигнала. Информационный код

10 в прямом и инверсном видах поступает через каналы 18 передачи информации на входы элементов ИСКЛЮЧАЮ- . ЩЕЕ ИЛИ 8 - второй группы, а синхросигнал через канал передачи 18

15 синхросигнала поступает на вторые входы элементов ИСКЛЮЧАЩЕЕ ШШ 8 второй группы и на блок 4 управления, запуская его .

Информационный код только в пря- 20 мом виде с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 второй группы поступает на входы второго регистра 4, входы узла 2 свертки по модулю два и на входы группы Т-триггеров 9.

25 С выхода узла 2 свертки по моду- лю два сигнал дополнения до нечетности на прямой вход разрешения записи второго регистра 4 и на инверс- Ш1Й вход разрешения счета двоичного

30 двухразрядного счетчика 2. С выхода блока I4 управления на R-входы двоичного двухразрядного счетчика 12 и Т-триггеров группы 9 выдается короткий импульс обнуления, совпадающий по времени с передним (положительным) фронтом синхроимпульса и устанавливающий Т-триггер и двоичный двухразрядный счетчик в нулевое состояние,

По окончании действия сигнала обнуления блок 14 управления выдает первый импульс записи, совпадающий по времени с единичным значением уровня сигнала синхронизации и поступающий на С-вход второго регистра 4, на С-входы Т-триггеров группы 9 и на счетный вход двоичного двухразрядного счетчика 12.

Те Т-триггеры группы 9, на Т-вхо- ды которых приходит единичный уровень с выходов элементов ИСКЛЮЧАЮ1ЦЕЕ ИЛИ ,8 второй группы, переключается в единичное, состояние.

При отсутствии сбоев по модулю 55 два с прямого выхода узла 2 свертки по модулю два снимается единичный уровень, поступающий на вход разрешения записи второго регистра 4. Во

35

40

15

второй регистр 4 проияппдится запись инфо1;)ма1:;ии, поступающей с выходов элементов ИСКЛЮЧАЮЩЕЕ HJM 8 второй группы. Этот же единичный уровень поступает на инверсшлй вход разреше- 5 ния счета двоичного двухразрядного Счетчика 12 и запрещает его переключение.

При наличии сбоя с прямого выхода узла 2 свертки по модулю два снимает- О ся нулевой уровень, который поступает на прямой вход разрешения записи второго регистра 4 и запрещает запись в него информации. Этот же нулевой уровень поступает на инверсный вход разрешения счета двоичного двухразрядного счетчика 12, при этом счетчик по сигналу, приходящему на его счетный вход, увеличивает свое состояние на единицу. .

По заднему (отрицательному) фронту синхроимпульса блок 14 управления вырабатывает второй импульс записи, который так же, как и первый, поступает на С-входы второго регист- 23 а 4 и Т-триггеров группы 9 и на счетный вход двоичного двухразрядного счетчика 12. Этот импульс, как первый, при отсутствии сбоя по моулю два осуществляет запись инфор ации во второй регистр 4, а при наичии сбоя увеличивает состояние воичного двухразрядного счетчика 12 на единицу. Одновременно с этим е Т-триггеры группы 9, на Т-входы оторых приходит единичный уровень выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 второй группы, как и во время действия первого импульса записи, переключаются в нулевое состояние. Смена уровня на Т входах любых Т- триггеров сигнализирует о наличии ошибки в канапе, соответствующем данному Т триггеру группы 9. При этом данные Т-триггеры группы 9, соответствующие неисправным (сбойным) каналам, установлены после окончания действия второго импульса записи в единичное состояние.

Сигналы единичного уровня с выходов Т-триггеров неисправных (сбойных) каналов поступают на входы элемента ИЛИ 10 и на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11.

20

30

35

40

45

50

На выходе элемента ИЛИ 10 при себе возникает единичный уровень, поступающий в блок 14 управления. На выходе элемента ИС1аЮЧАЮЩЕЕ ИЛИ

15

5

О

51083

1

ко же

единич{сь:и уровень возникает толь- при од гократной , он так- поступает в блок 14 управления. При отсутствии ошибок или при однократной ошибке одного разряда за время одного такта передачи блок 14 управления вьщает на выход 15 синхросигналов синхроимпульс после окончания действия второго сигнала записи.

При двукратной ощибке в одном разряде (т.е. при ощибках в разряде кок при передаче кодового слова в прямом виде, так и при передаче в инверсном виде за один такт синхросигнала) или при ошибках в не-: скольких разрядах синхроимпульс на выход 15 синхроимпульсов не выдается, а выдается сигнал блокировки 20 на выход 16 блокировки устройства.

Формула изобретения

Устройство для контроля передачи информации, содержащее два уз ла свертки по модулю два и два регистра, причем разрядные выходы первого регистра подключены к соответствующим информационным входам каналов передачи информации и синхросигналов, входы первого узла свертки по модулю два являются информационными входами устройства, а входы второго узла свертки по модулю два объединены с информационными входами второго регистра, выходы которого являются информационными выходами устройства, отлич. ающее ся тем, что, с целью повышения достоверности контроля, в него введены; две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группа Т-триггеров, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, двоичный двухразрядный счетчик, формирователь импульсов и блок управления, причем блок управления содержит четыре формирователя импульсов, два элемента ИЛИ, элемент И, RS-триггер и дешифратор, входы которого соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ШШ, с выходом элемента ИЛИ устройства и выходами первого и второго разрядов двоичного двухразрядного счетчика, пятый, восьмой и девятый выходы дешифратора подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с S-входом RS-триггера, прямой -выход которого является выходом

блокировки устройства, инверсный выход RS-триггера подключен к перво му входу элемента И, выход которого является выходом j синхросигналов устройства, второй вход элемента И блока управления соединен с выходом первого формирователя импульсов, ин- версйый вход которого соединен с первым входом второго элемента ИЛИ и с выходом второго формирователя импульсов, инверсный вход которого объединен с прямым входом третьего формирователя импульсов и с первыми входами элементов ИСКЛЮЧАКШЩЕ ИЛИ второй группы и подключен -.к выходу Канала передачи синхросигналов, выход третьего формирователя импульсов соединен с инверсным входом четвёртого формирователя импульсов, с R-входом RS-триггера и подключен к входам сброса двоичного счетчика и Т триггеров группы устройства, выход четвертого формирователя импульсов блока управления соединен с вторым входом второго элемента ИЛИ, выход которого соединен с С входами геров группы, синхровходом второго регистра и счетным входом двоичного двухраэрядного счетчика, вход синхронизации устройства соединен с первыми входами элементов ИСКЛЮЧАЩЕЕ ИЛИ

Гпервой группы и входом формирователя импульсов, вьщод которого соединен с синхровходом первого регистра, информационные входы которого соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ или первой группы, а (Н+1)-й вход первого регистра соединен Q входом синхронизации устройства, входы элемента ИСКПИЧАНЯЦЕЕ ИЛИ соединены с соответствующими входами элемента ИЛИ и соответствующими выходами Т-триггеров группы, Т-входы которых соединены с соответствующими информациони 1ми входами второго регистра и с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вто- рые входы которых подключены к выходам каналов передачи информации, выход второго узла свертки по модулю два соединён с прямым входом разрешения записи второго регистра и с инверсным входом разрешения счета двоичного двухразрядного чика, инверсный выход первого узла свертки по -модулю два соединен с вторым входом N - го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы,, вторые входы остальных (N -)х элементов кото рой являются информационными входами устройства.

(pue.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| Счетчик | 1987 |

|

SU1437993A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2029352C1 |

| Устройство для моделирования процесса передачи информации | 1989 |

|

SU1777149A1 |

| Адаптивное устройство декодирования кода Манчестер | 1988 |

|

SU1640826A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

Изобретение относится к области вычислительной техники и предназначено для использования в трактах передачи дискретной информации между цифровыми устройства1-ш. Целью изобретения является повышение достоверности контроля. Устройство для контроля передачи информации содержит два узла свертки по модулюгДва, два регистра, информационные входы, информационные выходы, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу Т-триггеров, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, двоичный двухразрядный счетчик, формирователь импульсовj блок управления. В устройстве информация передается по каналам передачи информации в прямом и инверсном виде. 2 ил. to (Л

| Устройство для контроля информации по модулю два | 1979 |

|

SU877546A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Захаров В.Н | |||

| и др | |||

| Справочник по радиоэлектроииым системам | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| I, с | |||

| Складная решетчатая мачта | 1919 |

|

SU198A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-08-15—Публикация

1984-08-25—Подача