формациокный канал, кроме последнего, введены переключающий триггер, элемент И и элемент ИЛИ-НЕ, выход которого соединен с первым входом реверсивного счетчика, первЬ)1Й и второй выходы блока элементов задержки подключены к первому и второму входам элемента ИЛИ-НЕ, к второму входу реверсивного счетчика подключен выход нереключаюпхего триггера, к первому и второму входам которого подключены соответственно первый и второй выходы блока переключения, выход элемента И соединен с третьими входами регистра сдвига и блока элементов задержки, выход арифметического блока подключен к первому входу элемента И, к второму входу которого подключен четвертый выход блока управления, первый выход реверсивного счетчика соединен с вторым входом комнаратора, второй выход реверсивного счетчика подключен к входам второго блока переноса кода и блока сравнения, выход которого соединен с шестым входом блока управления, третий выход реверсивного счетчика соединен с седьмым входом блока управления, седьмой выход которого подключен к второму входу счетного блока, восьмой выход блока управления соедипен с третьим входом реверсивного счетчика, вторые выходы блока памяти подключены соответственно к восьмому входу блока управления каждого ипформанионного канала, кроме последнего, вторая клемма системы соединена с девятым входом блока управления каждого ипформацнонного канала, кроме последнего, и с третьим входом блока управления последнсго информационного канала, выход счетного блока каждого информанионного капала, кроме последнего, соединен с четвертым входом блока управления последнего информационного канала.

2. Система по п. 1, отличающаяся тем, , что блок управления каждого информационного капала, кроме носледпего содержит триггеры переключения, формирователи импульсов, элементы И, элемепты ИЛИ и элемент задержки, выход первого триггера переключения соединеп с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, к второму входу которого подключен выход

второго элемента И, к первому входу которого подключен выход второго триггера переключения, выход третьего триггера переключения подключен к первому входу третьего элемента Ник входу формирователя импульсов, выход которого подключен к первому входу второго триггера переключения и к первому входу второго элемента ИЛИ, выхо,д которого подключен к входу элемента задержки и к первому входу первого триггера переключения, выход второго формирователя импульсов подключен к первым входам четвертого триггера переключения, третьего элемента ИЛИ, к второму входу второго элемента ИЛИ и к первому входу четвертого элемента ИЛИ, выход которого соединеп с нервым выходом третьего триггера переключения, выход пятого элемента ИЛИ соединен с вторым входом четвертого триггера нереключения, выход которого подключен к четвертому выходу блока управления, седьмой и девятый входы которого подключены к первому и второму входам пятого элемента ИЛИ, пятый вход блока унравления соединен с вторыми входами четвертого и третьего элемента ИЛИ, выход третьего элемента ИЛИ подключен к пятому выходу блока управления, пятый вход которого соединен с входом второго формирователя импульсов, выход которого подключен к первому выходу блока управления, первый вход которого подключен к вторым входам третьего триггера переключения и второго элемента И, седьмой вход блока унравления соединен с вторыми входами первого и второго триггеров переключения, шестой вход блока управления соединен с вторым входом первого элемента И, вгорой вход блока управления подключен к второму входу третьего элемента И, выход которого соединен с седьмым выходом блока управления, четвертый вход которого подключен к третьему входу второго элемента ИЛИ и к входу третьего формирователя импульсов, выход которого соединен с шестым выходом, блока управления, выход первого формирователя импульсов подключен к третьему выходу блока унравления, выход первого элемента ИЛИ соединен с вторым выходом блока унравле}1ия, выход элемента задержки подключен к восьмому выходу блока унравления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1054828A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1056246A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1051703A1 |

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU866734A1 |

1. СИСТЕМА ДЛЯ ПЕРЕДАЧИ ТЕЛЕИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ, каждый информационный канал которой содержит первичный преобразователь, выход которого через первый преобразователь импульсов соединен с входом арифметического блока, каждый информационный канал, кроме последнего, содержит регистр сдвига, первый выход которого подключен к первым входам блока управления и блока элементов задержки, первый и второй выходы которого соединены соответственно с первым и вторым входами блока переключения, управляющий триггер, первый выход которого соединен с третьим входом блока переключения, четвертый выход управляющего триггера подключен к четвертому входу блока переключения и к первому входу первого блока переноса кода, к второму входу которого подключен выход формирователя номера канала, генератор импульсов, выход которого соединен с первым входом регистра и вторым входом блока элементов задержки, выход блока задания апертуры соединен с первым входом компаратора, первый выход блока управления подключен к первому входу управляющего триггера. входу формирователя номера канала и второму входу первого регистра сдвига, второй выход блока упражнения подключен -к первому и второму входам управляюпхего триггера, третий выход соединен с первым входом второго блока переноса кода, четвертый выход - с входом блока задания апертуры, пятый выход - с первым входом счетного блока, щестой выход - с третьим входом первого блока переноса кода, выход компаратора подключен к второму входу блока управления, выход счетного блока подключен к третьему входу блока управления, реверсивный счетчик и блок сравнения, последний информационный канал содержит блок управления, первый и второй выходы которого подключены соответственS но к первому и второму входам второго преобразователя импульсов, третий выход под(Л ключен к первому входу блока переноса кода, к второму входу которого подключен выход второго преобразователя импульсов, к третьему входу которого подключен выход арифметического, блока, между .информационными каналами - блок элементов задержки, выходы которого подключены к четвертому входу блока управления каждого ин00 4 формационного канала, кроме последнего, и к первому входу блока управления последнего информационного канала, первая к,;1емоо ма системы содинена с пяты.м входом блоСП ка управления каждого информационного Ю канала, кроме последнего, и с вторым входом блока управления последнего информационного канала, блок памяти, к первым и вторым входам которого подключены соответственно выходы первого и второго блоков переноса кода каждого информационного канала, кроме последнего, к третьему входу блока памяти подключен выход блока переноса кода последнего информационного канала, первый выход блока памяти через согласующий блок подключен к системы, отличающаяся тем, что, с целью повыщения точности измерения, в каждый ин

f

Изобретение относится к информационноизмерительной технике и может быть использовано для сбора и передачи телеиз.мерительной информации, а также для построения

вертикальной структуры изменения гидрофизических параметров с помощью автономных зондирующих комплексов.

Известна система для сбора и передачи телеизмерительной информации о гидрофизических параметрах, содержащая запоминающее устройство, программно-временное устройство, блок управления в составе генератора опорной частоты, делителя частоты и канального распределителя, а также узел связи и многоканальную систему оцифровки, каждый канал которой содержит первичный измерительный преобразователь, преобразователь аналог - частота, частотное множительно-делительное устройство, формирователь импульсов, ключ, преобразователь средней частоты в код, включающий двоичный счетчик, запоминающий регистр со схемами ввода и вывода кода 1.

Однако эта система обладает динамической погрещностью осреднения за временной интервал преобразования и погрешностью ступенчатой аппроксимации, в результате которой сохраняется предыдущее значение преобразованного сигнала на время текущего преобразования. Кроме того, из-за равномерной дискретизации преобразования в ОЗУ записывается больщое число избыточных данных, что снижает информативность системы.

Наиболее близкой по технической сущности к предложенной является система для передачи телеизмерительной информации, каждый информационный канал которой содержит первичный преобразователь, выход которого через первый преобразователь импульсов соединен с входом арифметического блока, каждый информационный канал, кроме последнего, содержит регистр сдвига, первый выход которого подключен к первым входам блока управления и блока элементов задержки, первый и второй выходы которого соединены соответственно с первым и вторым входами блока переключения, управляющий триггер, первый выход которого соединен с третьим входом блока переключения, четвертый выход управляющего триггера подключен к четвертому входу блока переключения и к первому входу первого блока переноса кода, к второму входу которого подключен выход формирователя номера канала, генератор импульсов, выход которого соединен с первым входом регистра сдвига и вторым входом блока элементов задержки, выход блока задания апертуры соединен с первым входом компаратора, первый выход блока управления подключен к первому входу управляющего триггера, входу формирователя номера канала и второму входу первого регистра сдвига, второй выход блока управления подключен к первому и второму входам управляющего триггера, третий выход соединен с первым

входом второго олока переноса кода, четвертый выход - с входом блока задания апертуры, пятый выход - с первым входом счетного блока, шестой выход - с третьим входом первого блока переноса кода, выход компаратора подключен к второму входу блока управления, выход счетного блока подключен к третьему входу блока управления, реверсивный счетчик и блок сравнения, последний информационный канал содержит блок управления, первый и второй выходы которого подключены соответственно к первому и второму входам второго преобразователя импульсов, третий выход подключен к первому входу блока переноса кода, к второму входу которого подключен выход второго преобразователя импульсов, к третьему входу которого подключен выход арифметического блока, между информационными каналами - блок элементов задержки, выходы которого подключены к четвертому входу блока управления каждого информационного канала, кроме последнего, и к первому входу блока управления последнего инфор мационного канала, первая клемма системы соединена с пятым входом блока управления каждого информационного канала, кроме последнего, и с вторым входом блока управления последнего информационного канала, блок памяти, к первым и вторы.м Ьходам которого подключены соответственно выходы первого и второго блоков переноса кода каждого информационного канала, кроме последнего, к третьему входу блока памяти подключен выход блока переноса кода последнего информационного канала, первый выход блока памяти через согласующий блок подключен к вы.ходу системы 2.

Известная система позволяет уменьщить динамическую погрешность преобразователя и повысить информативность за счет адаптивного сжатия данных и оптимальной организации сбора данных в память.

Однако в адаптивных каналах известной системы имеется систематическая погрешность при оцифровке приращения входного сигнала, которая связана с тем, что при выбранной структуре анализатора и алгоритме его работы для обеспечения нормального функционирования преобразователя приращения средней частоты в код при разных знаках приращения необходимо устанавливать реверсивный счетчик преобразователя в положение «1, в моменты формирования начального значения сигнала и существенных отсчетов. В результате этого при изменении знака кода в преобразователе в процессе анализа возникает систематическая погрешность до двух и более единиц младшего разряда счетчика. Эту погрешность практически невозможно учесть, так как в системе не фиксируются моменты

перехода кодом счетчика через нулевое состояние. В результате определение моментов еущеетвенных отечетов производится с погрешностью, связанной с выбранным алгоритмом преобразования, снижающей точность шмерения. Кроме того, выданная схема адаптивного канала обладает огра1П1ченной эффективностью в связи с тем, что два режима работы - режим формирования начального кода измеряемого параметра и режим адаптивного анализа прнрапдения измеряемого параметра с формированием существенных отсчетов - - реализуются различным оборудованием, хотя эти режимы разделены .во времени, и, в принципе, из-за аналогичных физических процессов могут быть совмещены в одном и том же оборудовании.

Целью изобретения является уве.личение точности измерения за счет устранения систематической погрешности преобразования и как дополнительный эффект - повып1ение эффективности использования оборудования.

Поставленная цель достигается тем, что в каждый информационный канал, кроме последнего, введены переключающий триггер, элемент И, элемент ИЛИ-НЕ, выход которого соединен с первым входом реверсивного счетчика, первый и второй выходыпервого блока элементов задержки подключены к тервому и второму входам элемента ИЛИ-НЕ, к второму входу реверсивного счетчика подключен выход переключаюц;его триггера, к перрюму и второму входам которого 1ю.,т.к; ючены соответсчвенпо первый и второй выходы блоков переключения, выход элемента Vi соединен с ч третьими входами регистра сдвига и блока элементов задержки, выход арифметического б.чока подключен к первому входу элемента И. ч второму входу которого подключен четвертый выход блока уггравлепия, первый выкод реверсивного счетчика соединен с вторым входом компаратора, второй выход реверсивного счетчика подключен к входам второго блока переноса кода к блока сравнения, выход которого еоединеп с шестым входом блока управления, третий выход ревереивного ечетчика соединен с седьмым входом блока управления, седьмой выход KOTOpoio подключен к второму входу счетного блока, восьмой выход блока управления соединен с третьим входом реверсивного счетчика, вторые выходы блока памяти подключены соответственно к восьмому входу блока управления каждого информационного капала, кроме последнего, вторая клемма системы соединегаа с девятым входом блока управления каждого информационного канала, кроме последнего, и с третьим входом блока управлепия последнего ииформациопного канала, выход счетного блока каждого ипсрорманионного канала, Kporvie последнего, соединен с ч.етвертым входом блока управления последнего информационного канала. Кроме того, блок управления содержит триггеры переключения, формирователи импульсов, элементы И, элементы ИЛИ и элемент задержки, выход первого триггера переключения соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, к второму входу которого подключен выход

второго элемента И, к первому входу которого подключен выход второго триггера переключения, выход третьего триггера переключения подключен к первому входу третьего элемента Инк входу формирователя импульсов, выход которого подключен к первому входу второго триггера переключения и к первому входу второго элемента ИЛИ,. выход которого подключен к входу элемента задержки и к первому входу первого триггера переключения, выход второго формирователя импульсов подключен к первым входам четвертого триггера переключения, третьего элемента ИЛИ, к второму входу второго элемента ИЛИ и к первому входу четвертого элемента ИЛИ, выход которого соединен с первым выходом третьего триггера переключения, выход, пятого элемента ИЛИ соединен с вторым входом четвертого триггера переключения, ВРЛХОД которого подключен к четвертому выходу блока управления, седьмой и девятый входы которого подключены к первому и второму входам пятого элемента ИЛИ, пятый вход блока управления соединен с вторыми входами четвертого и третьего элемента ИЛИ, выход третьего элемента ИЛИ подключен к пятому выходу блока управления, пятый вход которого соединен с входом второго формировате.пя импульсов, выход которого подключен к первому выходу блока управления, первый вход которого подключен к вторым входа.У третьего триггера переключения и второго элемента И, седьмой вход блока управления соединен с вторыми входами первого и второго триггеров переключения, шестой вход блокр управления соединен с вторым входом первого элемента И, второй вход управления подключен к второму входу

третьего элемента И, зыхо.а которого соединен с седьмым выходом блока управления, четвертый вход которого подключен к третьему входу второго элемента ИЛИ и к входу третьего формирователя импульсов, выход которого соединен с шестым выходом блока

управления, выход первого формирователя импульсов подключен к третьему выходу блока управления, выход первого элемента ИЛИ соединен с вторым выходом блока управлепия, выход элемента задержки подключей к восьмому выходу блока управления.

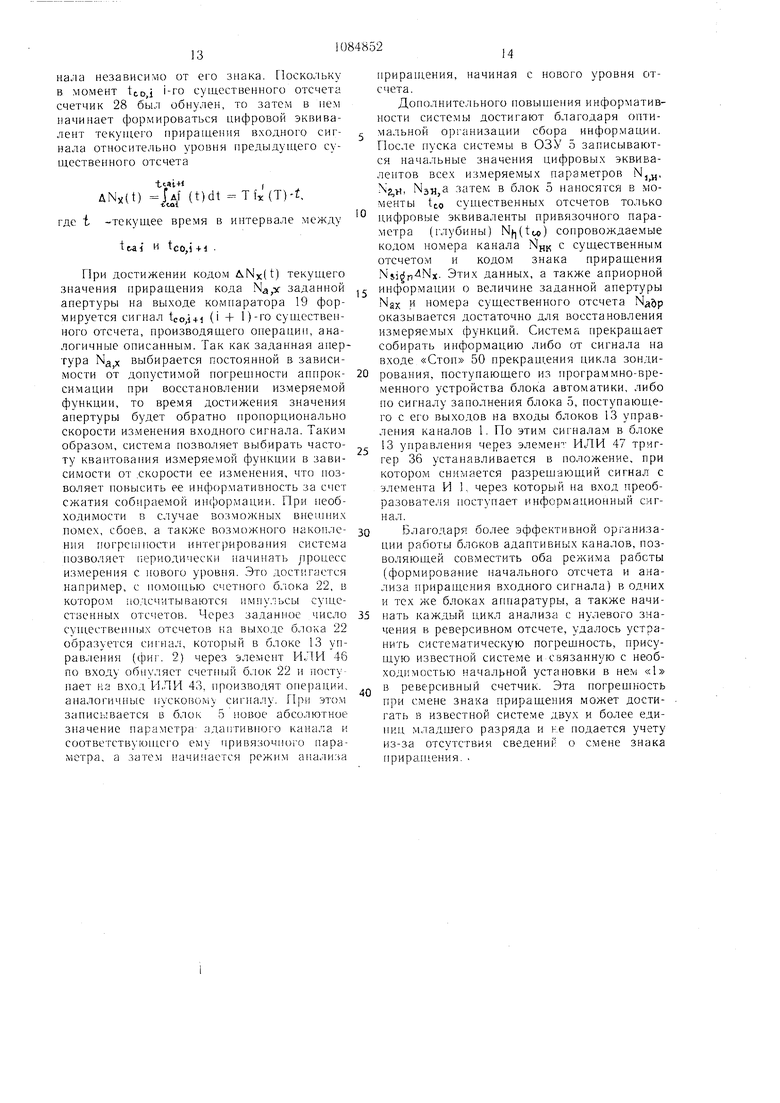

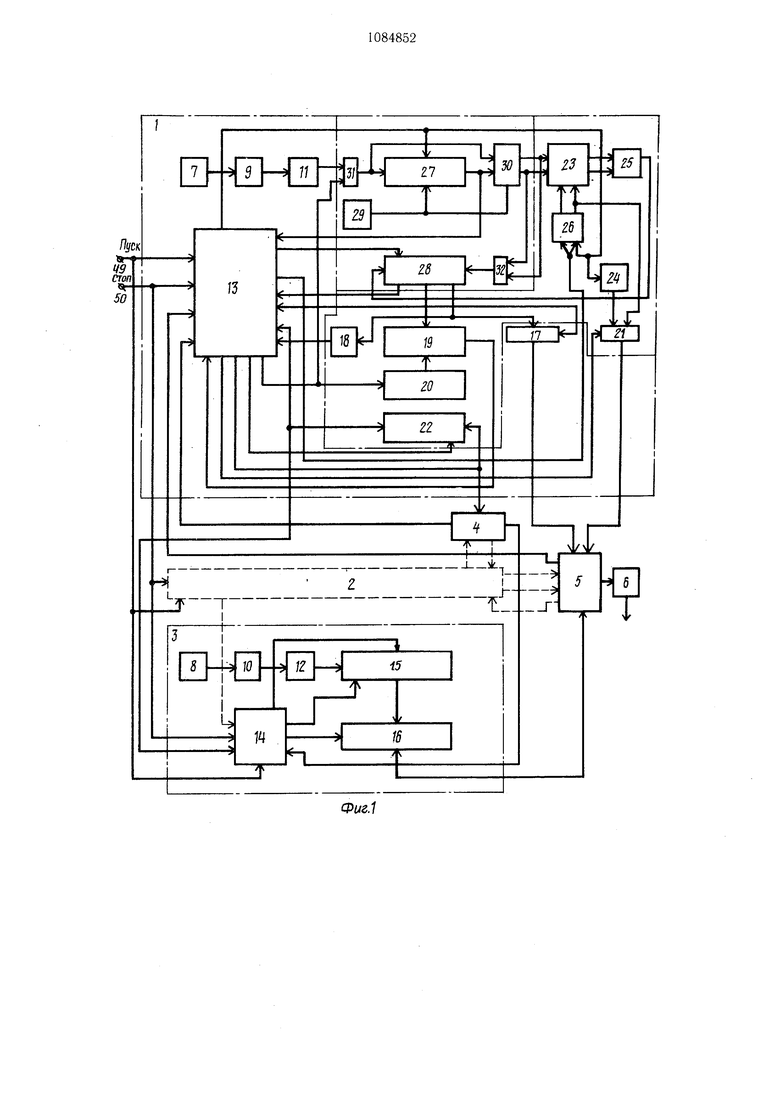

На фиг. 1 изображена блок-схема предложенной системы; на фиг. 2 -- функциональная схема блока управления адаптивного канала. Система (фиг. 1) содержит п информационных каналов 1-3, блок 4 элементов задержки, блок 5 памяти, согласующий блок 6, каждый информационный канал содержит первичные преобразователи 7 и 8, первые преобразователи 9 и 10 импульсов, арифметические блоки 11 и 12, блоки 13 и 14 управления. Последний информационный канал содержит второй преобразователь 15 импульсов и блок 16 переноса кода, остальные информационные каналы содержат второй блок 17 переноса кода, блок 18 сравнения, компаратор 19, блок 20 задания апертуры, первый блок 21 переноса кода, счетный блок 22, блок 23 переключения, формирователь 24 номера канала, переключающий триггер 25, управляющий триггер 26, регистр 27 сдвига, реверсивный счетчик 28, генератор 29 импульсов, блок 30 элементов задержки, элемент И 31, элемент ИЛИ-НЕ 32. Генератор 29 и реверсивный счетчик 28 составляют второй преобразователь импульсов всех информационных каналов, кроме последнего. Блок 13 управления каждого информационного канала, кроме последнего, содержит триггеры 33-36 переключения, элементы И 37-39, формирователи 40-42 импульсов, элементы ИЛИ 43;-47 и элемент 48 задержки. Система имеет первую клемму 49 и вторую клемму 50. Система работает следующим образом. Аппаратура системы в зависимости от применяемой системы спуска и подъема зондирующего комплекса может располагаться или в зонде или на борту плавучести, с которой производится зондирование. Если используется система спуска и подъема со свободным движением зонда по направляющему кабель-тросу, то аппаратура размещается в корпусе зонда, а в бортовой аппаратуре размещается узел связи, буферное ОЗУ, программно-временное устройство и блок передачи данных. Если используется система принудительного движения зонда с постоянной электрической связью между аппаратурой зонда и бортовой аппаратурой, то в корпусе зонда размещаются только преобразователи 7 и 8 и преобразователи 9 и 10, подключаемые через согласующий блок 6 к остальной аппаратуре, размещенной на борту плавучести. Принципы и средства сбора информации для обоих вариантов аналогичны. В момент начала процесса зондирования от программно-временного устройства или датчиков блока автоматики (не показано) на клемму 49 поступает сигнал начала цикла измерения. Этот сигнал поступает на входы блоков 13 и 14 управления, в которых вырабатываются сигналы управления, устанавливающие блоки системы в исходное состояние. По сигналу «Пуск на клемме 49 блока 13 управления (фиг. 2), на выходе формирователя 41 появляется импульс, по которому по первому выходу обнуляется регистр 27 сдвига и устанавливается в исходное положение формирователь -24 и в нулевое положение триггер 26. Импульс с выхода формирователя 41 через элемент ИЛИ 46 поступает также на шестой выход блока 13 управления, с которого он поступает на вход обнуления счетного блока 22. Этот же импульс устанавливает через элемент ИЛИ 45 в нулевое положение триггер 33, через элемент ИЛИ 43 - в нулевое положение триггер 34, а триггер 36 устанавливается в положение «1, при этом сигналом с четвертого выхода включается в работу блок 20 задания апертуры и открывается элемент И 31. Импульс с выхода элемента ИЛИ 45, задержанный в элементе 48, по второму выходу блока 13 управления обнуляет реверсивный счетчик 28. Аналогично в блоке 14 управления последнего канала 3 вырабатываются сигналы, устанавливающие по второму выходу реверсивный счетчик преобразователя 15 в нулевое положение и открывающие информационный вход преобразователя. Сигналы с преобразователей 7 и 8, преобразованные в блоках 9 и 10 в частоту следования импульсов, после масштабирования в блоках 11 и 12, поступают через открытые элементы И 31 на информационные входы третьих преобразователей. Импульсы входной частоты f)((t) поступают с выхода элемента И 31 на информационные входы блока 30 и регистра 27 сдвига, на сдвигающий вход которого поступают тактовые импульсы fg с выхода генератора 29 опорной частоты. Регистр 27 сдвига выполняет функцию цифровой линии задержки входной последовательности импульсов. Импульсы входной последовательности fx(t), поступающие на информационный вход регистра 27 сдвига, сдвигаются в нем тактовыми импульсами fo с выхода генератора 29 и появляются на выходе регистра 27 сдвига с задержкой на интервал времениТ Npeдto, где Ыред емкость в битах регистра сдвига; tq- период следования тактовых импульсов. Стабильность интервала времени Т определяется стабильностью генератора 29, а в случае использования кварцевого генератора имеет высокое значение. Задержанная последовательность импульсов f,(t-Т) с выхода регистра 27 сдвига поступает на второй вход блока 30, который обеспечивает сдвиг во времени друг относительно друга импульсов прямой fx(t) и задержанной последовательностей f3c(t-Т) с по.мощью, например, синхронизации одной последовательности передним фронтом, а другой последовательности - задним фронтом тактовых импульсов, Г1оступаюи1,их с выхода генераимпульсов, поступающих с выхода генератора 29 на синхронизирующий вход бло ка 30. Благодаря этому обеспечивается несовпадение во времени следования импульсов обеих последовательностей, необходимое для нормальной работы реверсивного счетчика. Импульсы прямой fx{t) и задержанной fs(t-Т) последовательности поступают с выходов блока 30 на входы элемента ИЛИ-НЕ 32 и блока 23 переключения, установленного с помощью триггера 26 в прямом направлении. При изменении положения триггера 26 блок 23 устанавливается в инверсное положение. В соответствии с последовательностью поступающих на входы импульсов триггер 25 переключается и устанавливает сигналом с выхода направление счета импульсов входной и задержанной последовательностей, просуммированных элементом ИЛИ-НЕ 32 и поступаюпдих на вход реверсивного счетчика 28. Поскольку триггер 25 переключается пере.аним фронтом импульсов, а реверсивный счетчик срабатывает по задним фронтам этих же импульсов (благодаря элементу ИЛИ-НЕ), то в реверсивном счетчике производится интегрирование разницы импульсов входной ty(t) и задержанной fx(t-Т) последовательяостей. Так как в начальный момент регистр 27 сдвига удтановлен в нулевое положение, то в течение времени Т после пуска на входы блока 30 будут поступать по входу только импульсы входной последовательности fx(t). Благодаря начальной установке триггера 26 в нулевое положение блок 23 переключения устанавливается в прямом 1 аправлении, при котором импульсы входной последовательности I (t) проходят на выход, устанавливая триггера 25 в единичное положение. При этом сигналом с прямого выхода триггера 25 счетчик 28 устанавливается на «Сложение, и импульсы входной последовательности fj,(l) поступая через элемент ИЛИ-НЕ 32 на счетный вход счетчика 28, суммируются в нем. За вре.мя Т в счетчике 28 образуется число ИМПУЛЬСОВт fxitidt Tfx(T). где Т -время задержки з регистре сдвпга; fx rt} - средняя за время Т частота входных импульсов, являюи1аяси пифровым эквивалентом начального значения входного сигнала. Через интервал времени Т 1юсле пуска на выходе регистра 27 сдвига появляется первый импульс задержанной последовательности fj((t- Т), по которому производится перевод канала па работу в режим анализа приращения вх(5дрого сигнала. Ио сигналу на первом входе блока 13 управ.ления (фиг. 2) триггер 34 устанавливается в единичное положение. При этом сигналом с выхода триггера 34 открывается элемент И 39. По переднему фронту сигна.ла на выходе триггера 34 на выходе формирователя 40 образуется импульс, который по третьему выходу поступает на управляющий вход блока 17, через который код N.M начального значения измеряемого параметра переносится в блок 5. Импульс с выхода формирователя 40 также устанавливает в единичное положение триггер 35 и через элемент ИЛИ 45 устанавливает в нулевое положение триггер 33, а затем этот же импульс после задержки в элементе 48 обнуляет по второму выходу реверсивный счетчик 23. Срабатывающий при этом блок 18 формирует на выходе импульс, который однако не проходит через элемент И 37, поскольку на нем нет разрещающего потенциала с прямого выхода триггера 33, установленного в нулевое положение. Схема подготовлена для работы в режиме анализа текущего приращения входного сигнала. Если первым после установки режима анализа придет импульс входной последовательности fylt), то благодаря начальному положению триггера 26, установленного с блока 23 переключения в прямом направлении, он поступит на вход «Сложение в счетчике 28. Если первым в режиме анализа поступает импульс задержанной последовательности yii-Т), то он при начальной установке триггера 26 должен был бы поступить на вход «Вычитание в счетчике 28, а при его начальном обнулении это привело бы к .образованию обратного кода на его выходах. Так как сравнение приращения осуществляется по абсолютному значению, то необходимо, чтобы в счетчике 28 всегда, независимо от знака приращения, образовывался прямой код. Это достигается тем, что первый после установки режима анализа импульс (второй после пуска системы) задержанной последовательности с первого входа бло1са 13 управления поступает через открытый элемент И 38 и затем через элемент ИЛИ 44 по второму выходу на счетный вход триггера 26. перебрасывая его в положение, при которо.м блок 23 переключения устанавливается в инверсное положение. Благодаря этому первый задержанный имлу/;ьс поступает опять на вход «Сложение счетчика 28, образуя в пем прямой 1-;од. Затем на вход счегчика 28 начнут поступать импульсы прямой fx(t) и задержанной 1(1-Т) последовательностей, причем имг1ульсы од.ной последовательности будут суммироваться, а импульсы другой -- вычитаться. Если после установки режима ана.:1иза первым прип1ел импульс входной последовательности ficlt), записав единицу в счетчике 28, и частота входной последовательности больнее, чем задержанной (параметр растет), то в счетчике число тоже будет расти. Если в процессе анализа знак приращения меняется, то импульсы задержанной последовательности fj(t-Т) начинают поступать чаше и число в счетчике 28 начнет уменьшаться. При достижении числом в счетчике 28 нулевого значения срабатывает блок 16 и сигнал с его выхода проходит в блоке 13 управления (фиг. 2) через открытый элемент И 37 и элемент ИЛИ 44 по второму выходу на счетный вход триггера 26, меняющего свое положение и устанавливающего блок 23 переключения в инверсное.положение. При этом импульсы задержанной последовательности ljf(t-Т), имеющие больщую частоту следования, начинают поступать на вход «Сложение счетчика 28 и в нем образуется прямой код. Поскольку, как уже отмечалось, счетчик 28 суммирует импульсы одной последовательности (например, входной) и вычитают импульсы другой последовательности (задержанной), то в нем образуется цифровой эквивалент текущего прира.щения входного сигнала 1() (t)ti(t-T)dt (t)t Af,(T)(T)-t, fxCT)-текущее приращение входной частоты за время Т; fv{T) t -первая производная входной частоты; -текущее время, изменяющееся от Т до момента формирования первого существенного отсчета Причем независимо от знака приращения на выходах разрядов .счетчика 28 образуется всегда прямой код абсолютного значения приращения, а его знак SigAN определяется положением триггера 26, устанавливающего всегда направление счета, таким образом, чтобы преобладающая по частоте последовательность импульсов поступала на вход сложения счетчика 28. Код 4Nx(t) младщих разрядов с выходов счетчика 28 непрерывно сравнивается в цифровом компараторе 19 с кодом Na апертуры, задаваемой блоком 20. При достижении текущим кодом приращения сигнала кода заданной апертуры, т.е. при ANx(t) Na срабатывает компаратор 19 и сигнал с его выхода поступает через открытый элемент И 39 в блоке 13 управления на вход блока 4 и на вход счетного блока 22. Срабатывание компаратора 19 означает формирование сигнала первого существенного отсчета ico , по которому должен быть опрощен последний канал 3. В блоке 4, если сигналы на его входы приходят из каналов 1 и 2 раздельно во времени, то они появляются на выходе для соответствующего канала, опрашивая через блок 14 управления привязочный канал 3.-Если сигналы на входы блока 4 приходят одновременно или смещены на время меньще. чем необходимо для четкой записи кода в блок 5, то блок 4 производит временной сдвиг этих сигналов, отдавая приоритет одному нз них. Сигналом с выхода блока 4 в блоке 14 управления последнего канала 3 формируется сигнал управления, открывающий блок 16, через который в блок 5 из преобразователя 15 переносится текущий код привязочного параметра (например, глубиньО. Поскольку после получения начального кода привязочного параметра Nf,д счетчик в преобразователе 15 не обнуляется и на его счетные входы начинают поступать входная и задержанная последовательность импульсов, формируя в нем текущее приращение входного сигнала, то на выходах разрядов преобразователя 15 образуется прямой текущий код привязочного параметра./ N},(t) NH.i±4Nh(t) T(Tn(T) ±fh(T)-t;, Сигнал с выхода блока 4, соответствующий моменту формирования очередного i-ro существенного отсчета icQi поступает на вход блока 13 управления канала, в котором он сформировался. По этому сигналу в формирователе 42 блока 13 управления (фиг. 2) образуется импульс заданной длительности, открывающий блок 21 переноса кода, через который в блок 5 памяти записывается с выхода формирователя 24 код номера канала Njfn,B котором произошел существенньЕЙ отсчет, и код знака приращения NsigdN с выхода триггера 26. Сигнал с входа в блоке 13 управления поступает также через элемент ИЛИ 45 на вход триггера 33, снимающего разрещающий сигнал с элемента И 37, а затем через элемент 48 задержки обнуляет по второму выходу счетчик 28. Импульс с выхода сработавшего блока 18 не проходит по входу через закрытый элемент И 37 и не меняет положение триггера 26. Запрет на прохождение сигнала совпадения нулей счетчика 28 снимается после поступления первого импульса в счетчик 28. При этом с выхода первого , разряда счетчика 28 поступает сигнал, который устанавливает единицу в триггере 33 и нуль в триггере 35. При этом элемент И 37 открывается, а элемент И 38 закрывается. Таким образом, если обнуление счетчика 28 производится внешним сигналом (при пуске, при переходе в режим анализа и при формировании сигналов существенных отсчетов), то триггер 26 направления счета не меняет своего положения, поскольку сигнал с выхода блока 18 не проходит на в.ход триггера 26. После начала образования приращения в счетчике 28 сигналом с его первого разряда блокировка сигнала с выхода блока 18 снимается и сигналы обнуления счетчика 28, происходящие от изменения знака приращения, проходят на вход триггера 26. меняя его положение таким образом, что в счетчике 28 образуется всегда прямой код приращения входного сигHa;ia независимо от его знака. Поскольку в момент ttD,i iTO cymecTfseHHoro отсчета счетчик 28 был обнулен, то затем в нем начинает формироваться цифровой эквивалент текущего прирагцения входного сигнала относительно уровня нредыдущего сунцественного отсчета

ANx(t) Гд1 (t)dt (T)f,

t-tui где t -текущее время в интервале между

1:ьа1 и tcOji +1 .

При достижении кодом ANx(t) текущего значения нриращения кода Nape заданной анертуры на выходе компаратора 19 формируется сигнал tco,i+i (i + 1)-го существенного отсчета, производящего онерацин, аналогичные описанным. Так как заданная анертура Ng X выбирается постоянной в зависимости от допустимой погреншости аппроксимации при восстановлении измеряемой функции, то время достижения значения апертуры будет обратно пропорционально скорости изменения входного сигнала. Таким образом, система позволяет выбирать частоту кваптования измеряемой функции в зависимости от .скорости ее изменения, что позволяет повысить ее инфор.мативность за счет сжатия собираемой инсрормации. При необходимости в случае возможных виеплни.х помех, сбоев, а также возможного накопления погрешности интегрирования система позволяет периодически начинать jipouecc измерения с нового уровня. Это достигается например, с номоп1ью счетного блока 22, в котором подсчитываются импульсы существенных отсчетов. Через заданное число суп|,ествен1И)1х отсчетов на выхо.те блока 22 образуется сигнал, который в блоке 13 управления (фиг. 2) через элемент ИЛИ 46 по входу обнуляет счетн1,1Й блок 22 и посту пает на вход ИЛИ 43, производят операции, аналогичные пусковому сигналу. При это.м записывается в блок .5 повое абсолютное значение параметра- адаптивного канала и соответствующего ему привязочгюго параметра, а затем начи1ается режим апали.за

прирап1ения, начиная с нового уровня отсчета.

Дополнительного повышепия информативности системы достигают благодаря оптимальной организации сбора информации. После пуска системы в ОЗУ 5 записываются начальные значения цифровых эквивалентов всех нз.меряемых параметров N,, 2,м. эя,а затем в блок 5 наносятся в моменты ttQ существенных отсчетов только

цифровые эквиваленты привязочного параметра (глубины) Nf(tto) сонровождаемые кодом номера канала NHJ с существенным отсчетом и кодом знака приращения . Этих данных, а также априорной

информации о величине заданной апертуры Nax и номера существенного отсчета оказывается достаточно для восстановления измеряемых функций. Система прекращает собирать информацию либо от сигнала на входе «Стоп 50 прекращения цикла зондирования, поступающего из программно-временного устройства блока автоматики, либо по сигналу заполнения блока 5, поступающего с его выходов на входы блоков 13 управления каналов 1. По этим сигналам в блоке

13 управления через элемен-; ИЛИ 47 триггер 36 устанавливается в положение, при котором снимается разрещающий сигнал с элемента И 1, через который на вход преобразователя поступает информационный сигнал.

Благодаря более эффективной ор1анизации работы блоков адаптивных каналов, позволяющей совместить оба режима работы (формирование начального отсчета и анализа прирац;ения входного сигнала) в одних и тех же блоках аппаратуры, а также начипать каждый цикл анализа с нулевого значения в реверсивном отсчете, удалось устранить систематическую погрешность, присущую известной систе.ме и связанную с необходимостью начал1 ной установки в нем «1

в реверсивный счетчик. Эта погрешность при смене знака приращения может достигать в известной систегле двух и более единиц младщего разряда и н,е подается учету из-за отсутствия сведение о смене знака прирапления. .

SH-

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Антонов В | |||

| И., Бабит В | |||

| И | |||

| и Куприянов В | |||

| К | |||

| Автономный гидрофизический измерительный комплекс | |||

| - «Автоматизация научных исследований морей и океанов | |||

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| I, Севастополь, МГИ АН УССР, 1972, с | |||

| Способ закалки пил | 1915 |

|

SU140A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2923605/18-24, 1980 (прототип). | |||

Авторы

Даты

1984-04-07—Публикация

1981-05-28—Подача