пы, выходы регистров данных соединены соответственно с информационными входами элементов И первой и второй Групп, отличающееся тем, что, с целью повьппения быстродействия .обмена информацией между ЭВМ, в него введены два регистра режимов, два регистра адреса вектора прерьгаания, а в каждом из регистров слова состояния введены триггеры режима, при этом входы первого триггера режима и первого регистра режима соединены с четвертьм и пятым выходами первоги коммутатора, а входы второго триггера режима и второго регистра соединены соответственно с четвертым и пятым выходами третьего коммутатора, прямые выходы второго и первого триггеров режима регистров слова состояния соединены соответственно с управлякицими входами третьего и четвертого регистров адреса вектора

прерывания, с третьими входами первого и третьего коммутаторов, а инверсные выходы - с управляющими входами первого и второго регистров адреса вектора прерывания, выходы первого и второго регистров режима соединены соответственно с четвертыми входами третьего и первого коммутаторов, вторые входы триггеров готовности соединены с упрайляющдаш входами эле;ментов И второй и первой групп, а .третьи входы - с управляющими входами первого и второго регистров данныхувыходы первых триггеров разрешения прерывания соединены соответстзен но с И1 ормационными входами первого и второго регистров адреса вектора прерьтания, выходы третьего и четвертого регистров адреса вектора прерыванйя Соединены соответственно с информационными входа ш второго и четвертого коммутаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1312592A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для обмена информацией двух электронно-вычислительных машин | 1984 |

|

SU1231507A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ МАГИСТРАЛЕЙ, содержащее четьфе блока согласования, два регистра данных, два регистра адреса векторов прерывания, блок управления, че тыре коммутатора, две группы элементов И и два регистра слова состояния, каждый из которых содержит два триггера разрешения прерывания и триггер готовности, первые магистральные вход-выход блока управления через первый блок согласования подключен двухсторонней связью к первой магистрали, которая соединена с входом-выходом первого коммутатора с выходами первой группы элементов И и второго коммутатора, с входом второго блока согласования, вторая магистраль соединена через третий блок согласования с вторыми магистральными входами-выходами блока управления, а также с входом-выходом, третьего коммутатора, с выходами элементов И второй группы и четвертого коммутатора, с входами четвертого блока согласования, выходы второго и четвертого блоков согласования соединены соответственно с ин|формационными входами первого и вто.рого регистров данных и с первьм и вторым адресными входами блока управления, первьй и. второй выходы прерывания которого подключены к управляющим входам второго и четвертого коммутаторов, первые информационные входы которых связаны соответственно с выходами первого и второго регистров адреса вектора прерьшания, первый, второй и третий выходы первого коммутатора соединены соответственно с входами первого и второго триггеров разрешения прерьшания и с первым входом, первого триггера г готовности, выходы которых подключены к первому и второму входам ппеоывания и готовности блока управления, первый, второй и третий выходы третьего ксн мутатора соединены соотв с ветственно с входами третьего, четвертого триггеров разрешения прерывания и с первым входом второго триггера готовности, выходы которых подключены к третьему и четвертому входам прерывания и к второму входу готовнбсти блока управления, а выхо vl ды первого и второго триггеров готовности соединены соответственно с первыми входами третьего и первого коммутаторов и с вторыми входами первого и третьего коммутаторов, первый адресный выход блока управления . соединен с управляющими входами второго коммутатора, первого регистра данных и элементов И первой группы, второй адресный выход блока управления соединен с управляюшрми входами третьего коммутатора, второго регист-ра данных и элементов И второй груп

Изобретение относится к вычисли, тельной технике и может быть использовано при проектировании многомашинных вычислительных систем.

Известно устройство, содержащее буферный регистр, два блока связи

с каналом, блок Сравнения команд и блок задания режима Ol3«

Недостатком этого устройства является нейозможность его применения при проектированиимультипроцессорных систем, использующих интерфейс Общая щина.

Наиболее близким к предлагаемому является устройство параллельного обмена, содержащее канальные перегородки, и приемники, дешифратор адреса вектора прерывания, регистр состояния, мультиплексор данных, дешифра тор управляющих сигналов и соответст вующие связи меяиу ними 2 ).

Однако в известном устройстве приемник информации не может изменить состояние регистра состояния устройства обмена передатчика и

таким образом закончить дакл обмена, что приводит к существенному увеличению числа машинных команд в цикле обмена и к увеличению времени обменам

Цель изобретения - повьшение бьютСодействия обмена информацией между ЭВМ.

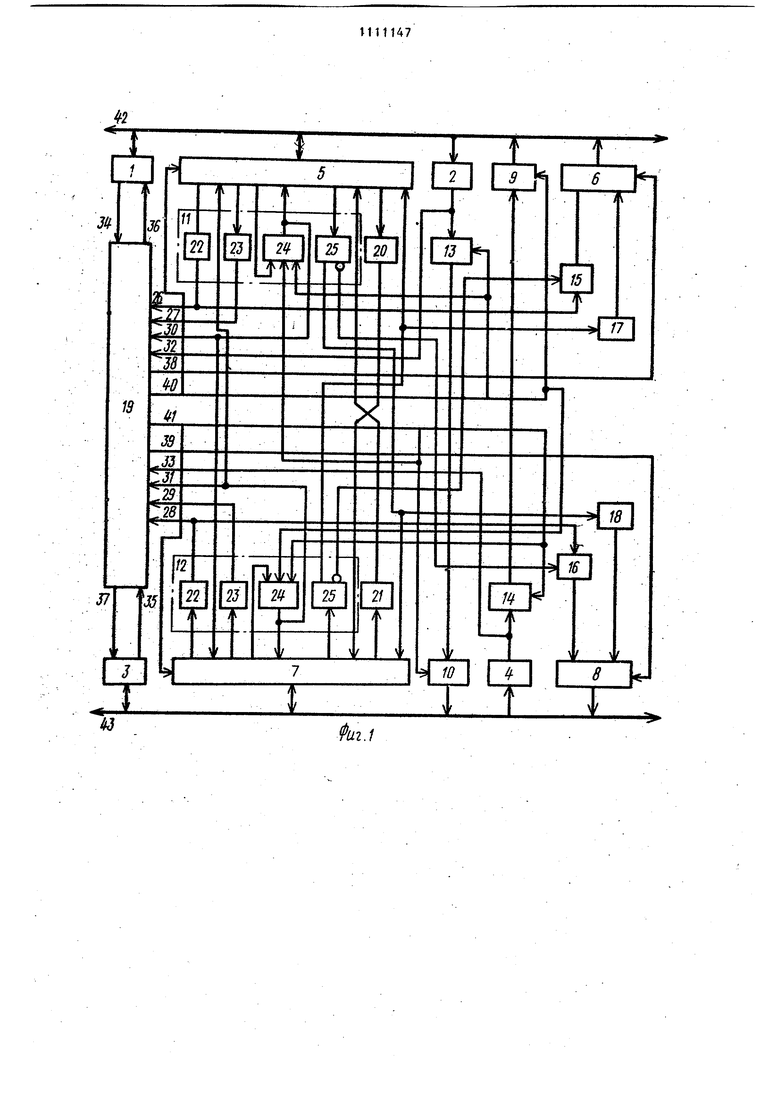

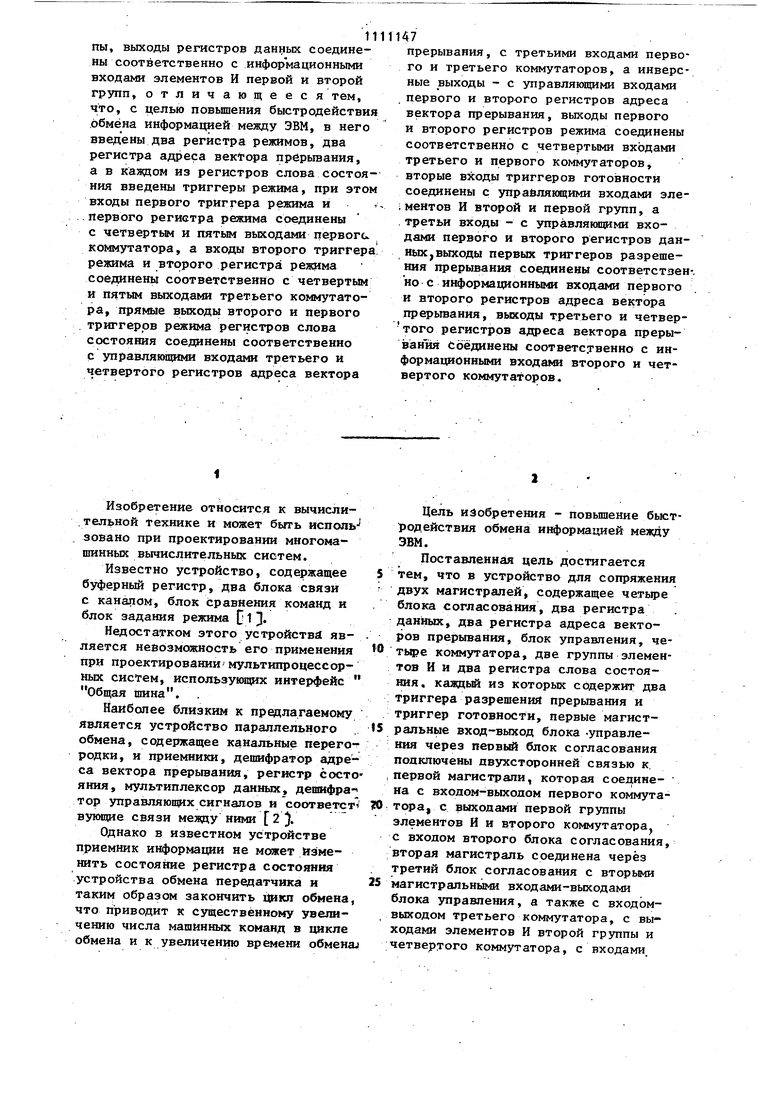

Поставленная цель достигается тем, что в устройство для сопряжения двух магистралей, содержащее четьфе блока согласования, два регистра данных, два регистра адреса векторов прерывания, блок управления, четыре коммутатора, две группы элементов И и два регистра слова состояния, каждый из которых содержит два триггера разрешений прерьтания и триггер готовности, первые магистральные вход-выход блока -управления через первый блок согласования подключены двухсторонней связью к. первой магистрапи, которая соедине- на с входом-выходом первого коммутатора, с выходами первой группы элементов И и второго коммутатора, с входом второго блока согласования, вторая магистраль соединена через ретий блок согласования с вторыми магистральными входами-выходами блока управления, а также с входомвыходом третьего коммутатора, с выодами элементов И второй группы и етвертого коммутатора, с входами. четвертого блока согласования, вы- ходы второго и четвертого блоков согласования соединены соответственно с информационными входами первого и второго регистров данных и с первы и BTopbiM адресными входами блока уттравления, первьй и второй выходы прерывания которог.о подключены к .управляющим входам второго и четвертого коммутаторов, первые информационные входы которых связаны соответственно с выходами первого и второго регистров адреса вектора прерывания, первьй, второй и третий выходы первого коммутатора соединены соответст - венно с входами первого и второго триггеров разрешенияпрерывания и с первым входом первого триггера готов ности, выходы которых подключены к первенцу и второму входам прерывания и готовности блока управления, первы второй и третий выходы третьего коммутатора соединены соответственно с третьего, четвертого триггеров разрешения прерывания и с первым входом второго триггера готовности, выходы которых подключены к третьему и четвертому входам прерывания и квторому входу готовности блока управ ления, а выходы первого и второго трисгеров готовности соединены соответственно с первыми входами третьег и первого коммутаторов и с вторыми входами первого и третьего коммутаторов, первый адресный выход блока управления соединен с управляющими входами второго коммутатора, первого регистра данных и элементов И первой группы, второй адресный выход блока управления соединен с управляющими входами третьего коммутатора, второго регистра данных и элементов И втброй группы, выходы регистров данных соединены соответственно с информационными входами элементов И первой и второй групп, введены два регистра режимов, два регистра адреса вектора прерывания, а в казкдом из регистров слова состояния введены триггеры режима, при этом входы первого триггера режима и первого регистра режима соединены с четверты ;И пятым выходами первого коммутатора а входы второго триггера режима и второго регистЕ1а режима соединены соответственно с четвертым и пятым выходами третьего коммутатора, прямые выходы второго и первого тригге ров резкима регистров слова состояния 1 7соединены соответственно с управляюшими входами третьего и четвертого регистров адреса вектора прерывания, .с третьими входами первого и третьего коммутаторов, а инверсные выходы с управляющими входами первого и второго регистров адреса вектора прерывания, выходы первого и второго регистров реткима соединены соответственно с четвертьми входами третьего и первого коммутаторов, вторые входы триггеров готовности соединены с управляющими.входами элементов И второй и первой групп, а третьи входы - с управляющимивходами первого и второго регистров данных, выходы первых триггеров разрешения прерь вания соединены соответственно с информационными входами первого и второго регистров адреса вектора прерывания, выходы третьего и четвертого регистров адреса вектора прерывания соединены соответственно с информационными в ходами второго и четвертого коммутатора. Нафиг. 1 приведена схема устройства; нафиг. 2-схема блока управления. Устройство содержит блоки-1, 2, 3 и 4 согласования, коммутаторы 5, 6 6,, 7 и 8, группы элементов И 9 и 10, регистры 11 и 12 слова состояния, регистры 13 и 14 данных, регистры 15, 16, 17 и 18 адресоввекторов прерьшания, блок 19 управления, регистры 20 и 21 режимов. Каждый из регистров слова сост.ояния содержит триггеры разрешения прерывания 22 и 23, готовности 24, режима 25. Блок 19 управления имеет входы 26, 27, 28 и 29 прерывания, 30 и 31 готовности, 32 и 33 адресные, 34, 35 и 36, 37 соответственно магистральные входы и выходы управляющих сигналов, вькоды 38 и 39 прерывания, 40 и 41 адресные, магистрали 42 и 43 Блок управления содержит два узла обмена стандартными магистральными , сигналами, каждый из которых содержит регистр 44 прерывания, дешифратор 45 сигналов ответа, дешифратор 46 адреса. Устройство может работать в режиме прерывания с ЭВМ, подключенной, например, к магистрали 42, если ранее в программном режиме в триггер 22 или 23 была записана единица. Сигналы с выходов триггеров 22 и 23 поступают на входы регистра 44 прерывания, а после обмена стандартными S сигналами регистра 44 с магистралью 42 на втором выходе регистра 44 фор мщ уется сигнал разрешения ввода в магистраль 42 адреса вектора преры|вания, адрес которого зависит от состояния триггеров 22 н 23. В соответствии с выработанным адресом вектора прерывания ЭВМ выполняет одну из программ обработки информации. При передаче информации ЭВМ-источник данных определяет готовность устройства к приему информации, для чего считывается в магистраль содер жимое регистра t1. Если триггер 24 находится в нулевом состоянии, устр.ойство готово к приёму данных с магистрали 42. После записи информа ции триггер 24 переходит в единично состояние, которое может быть счита но со стороны магистрали 43, как один из разрядов регистра 12 слова состояния. Считывание информации в магистраль 43 может производиться программно (по флагу) или по прерыванию. Если в начале цикла обмена при считывании и последующем анализе слова состояния с регистра 11 окаже ся, что состояние триггера 24 - еди ница, т.е. в регистре 23 хранится и 7 еще не считано слово данных, то ЭВМ - источник информации занесет программньш путем в триггер 23 разрешения единицу. ЭВМ-источник выходит из подпрограммы передачи информации и продолжает выполнение прерванной на время выполнения этой подпрограммь основной программы пользователя. Когда ЭВМ-приемник считает слово данных из регистра 13 и триггер 24 будет сброшен, возникнет прерывание. Адрес вектора прерывания соответствует нулевому состоянию триггеров 22 и 25. В программе обработки этого прерьгаания ЭВМ занесет программным путем . слово данных в регистр 13. Таким образом, повышается быстродействие обMeHai. Обмен мезвду ЭВМ может быть организован при помощи служебных слов, которые могут быть занесены в регистры режимов 20 и 21. Например, в них могут быть занесены начальные адреса буферных памятей ЭВМ-приемника информации, что также повышает быстродействие обмена. Увеличение быстродействия устройств обмена многомашинной системы позволяет псэтучить существенный экономический эффект.

I

4J

U2.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-30—Публикация

1982-08-04—Подача