Изобретение относится к вычислительной технике и .может быть использовано в вычислителышх системах для сопряжения большой ЭВМ высокой производительности с микро-ЭВМ при построении локальных вычислительных сетей (например, БЭСМ-6 и Электроника 60),

: Целью изобретения является повышение достоверности за счет контроля узлов устройства двумя ВМ.

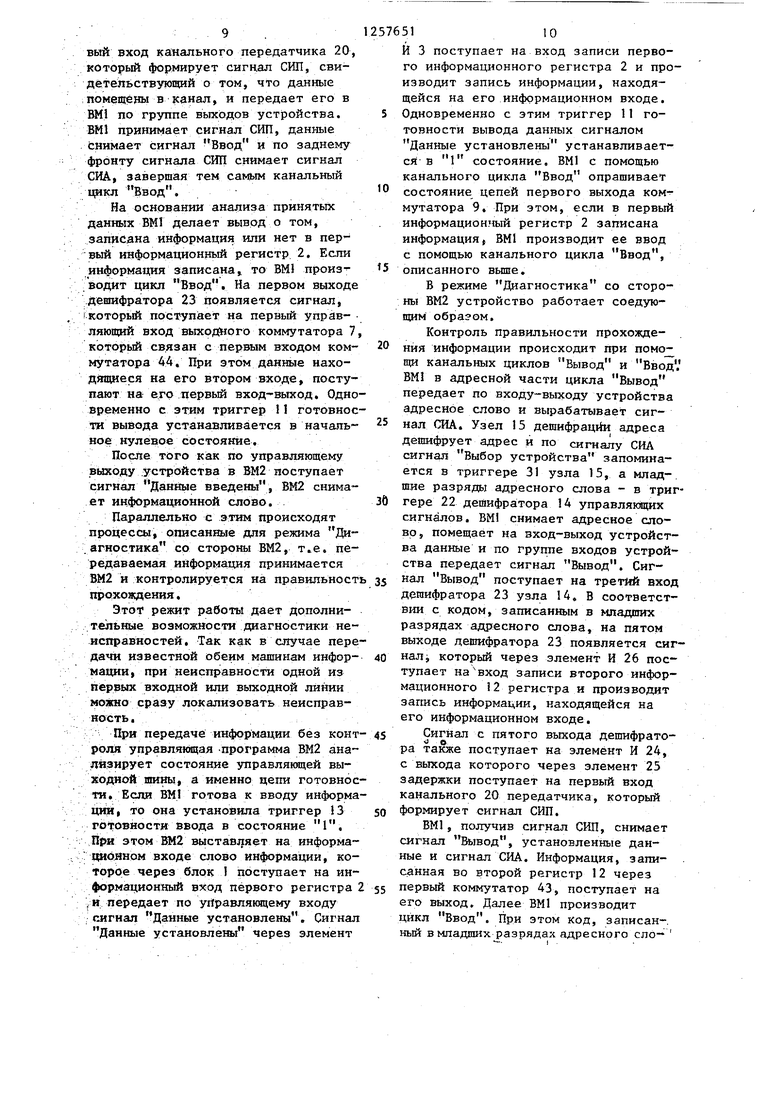

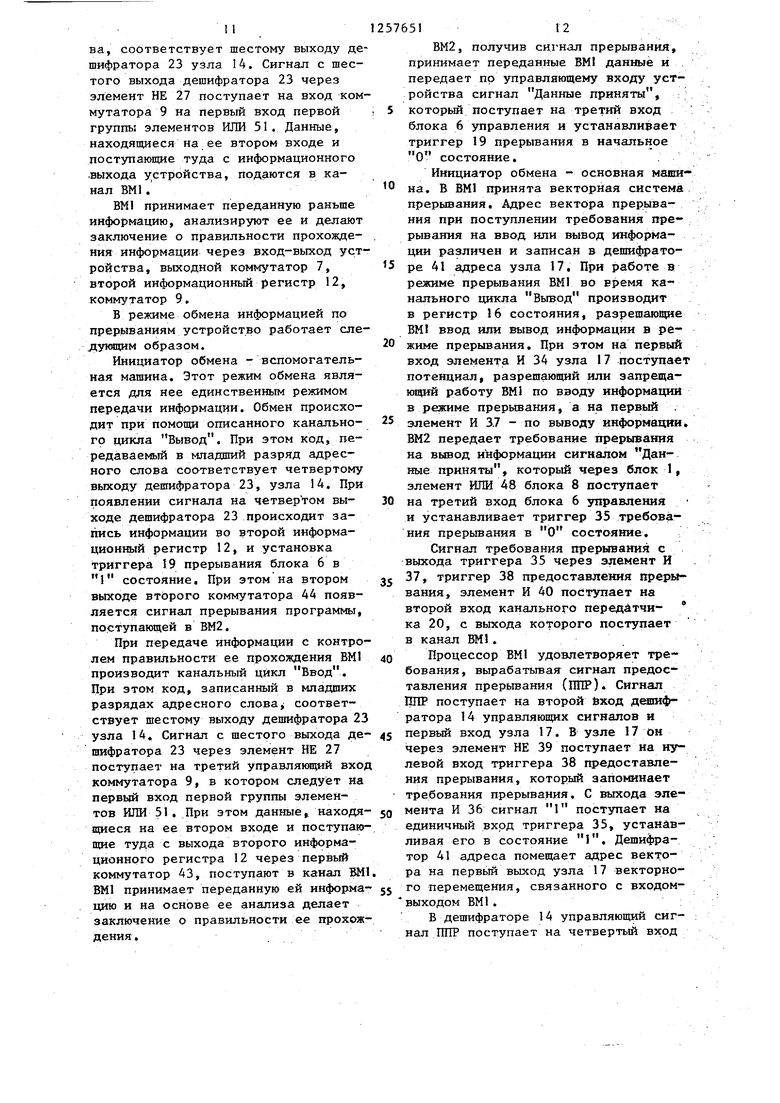

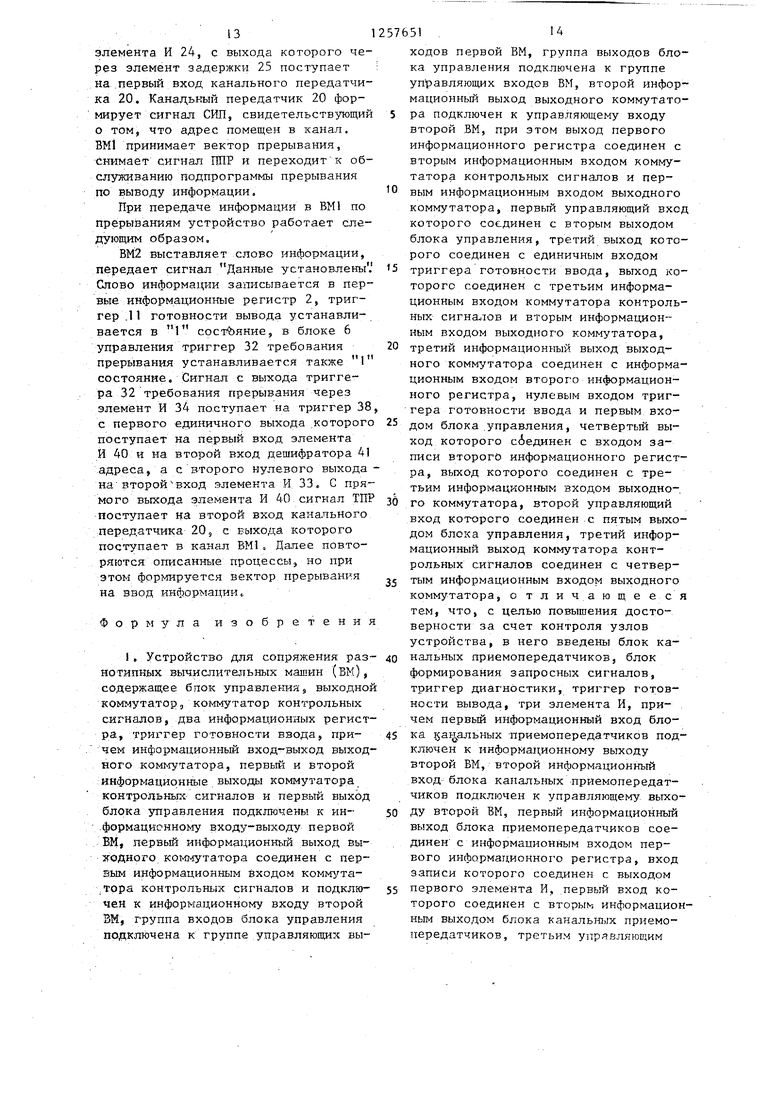

На фиг, 1 представлена блок-схема данного устройства; на фиг, 2 - схема блока управления; на фиг, 3 - схема выгодного коммутатора; на фиг, А - схема блока формирования запро сяых сигналов; на фиг, 5 - схема коммутатора контрольных сигналов.

Устройство содержит (фиг, l) блок 1 канальньт приемопередатчиков, первый информационный регистр 2, первьй .эдемент ИЗ, триггер Л диагностики, второй элемент И 5, блок 6 управления выходной коммутатор 7, блок 8 формирования запросных сигна- JJOB, коммутатор 9 контрольных сигналов, третий элемент И 10, триггер М готовности вывода, второй информационный регистр 12, триггер 13 готовности ввода.

БйОк 6 управления содержит (фиг,2 узел 14 дешифрации управляющих сигналов, узел 15 :Дешифрации адреса, регистр 16 состояния, узел 7 вектора прерывания, второй элемент И 18, четвертый триггер 19, группу 20 канальных передатчиков, первый элемент И 21,

При этом узел 14 дешифрации уп равляющих сигналов содержит первый триггер 22, дешифратор 23 команд, третий элемент И 24, элемент 25 задержки, четвертый элемент И 26, первый элемент НЕ 27.

Узел 15 депгафрации адреса содер- яшт первый дешифратор адреса, состоящий из группы элементов И-НЕ 28, группы перемычек 29 и элемента И-НЕ 30, первый триггер 31.

Узел 17 вектора прерывание содержит второй триггер 32, седьмой и пятый элементы И 33 и ЗА, третий триггер 35, восьмой и шестой элементы И 36 и 37, шестой триггер 38, второй элемент НЕ 39, десятый элемент И 40 второй дешифратор адреса 41, девятый элемент И 42,

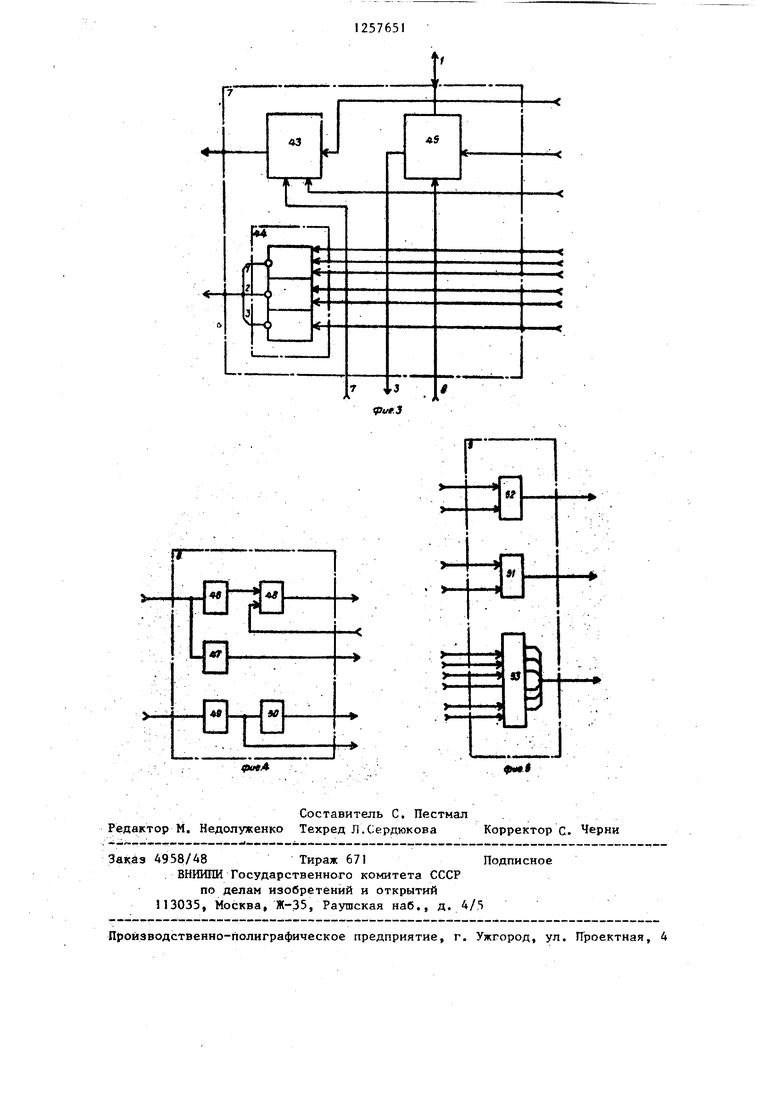

Выходной коммутатор 7 содержит (фиг, З) первый, второй и третий коммутаторы 43, 44 и 45,

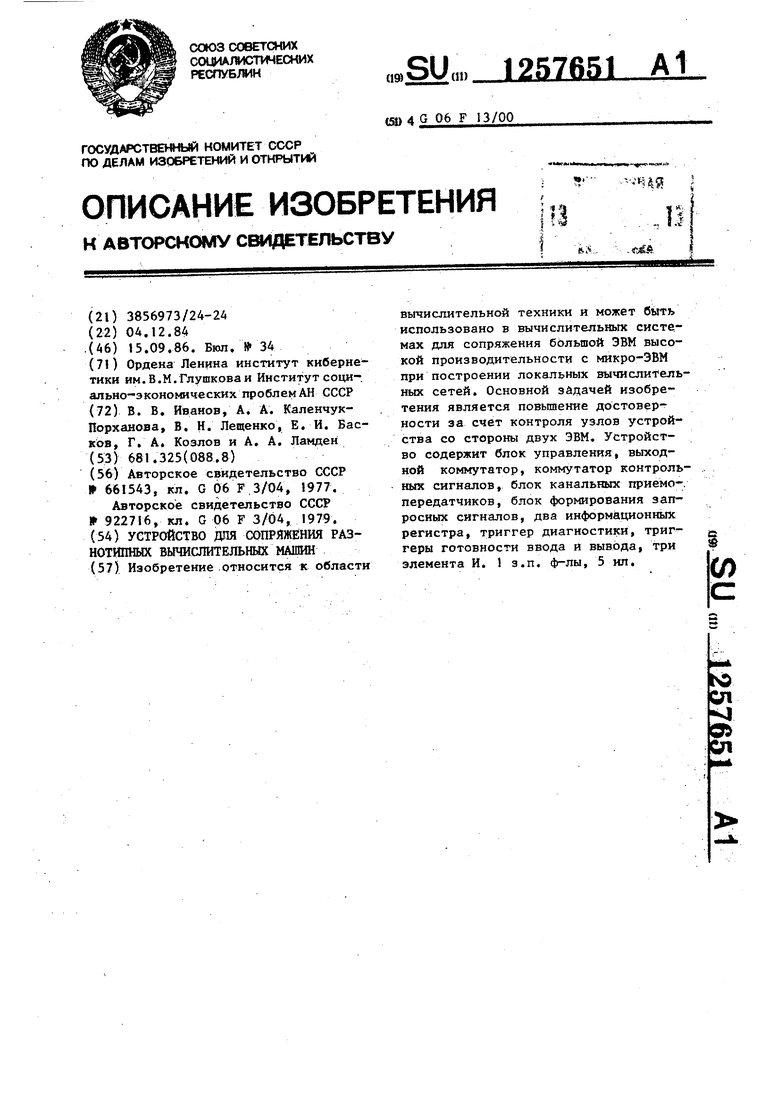

Блок 8 фор.мирования запросных сигналов содержит (фиг. 4) первый элемент 46 задержки, второй одновибра- тор 47, элемент ИЛИ 48, первый одно- вибратор 49, второй элемент 50 задержки,. .

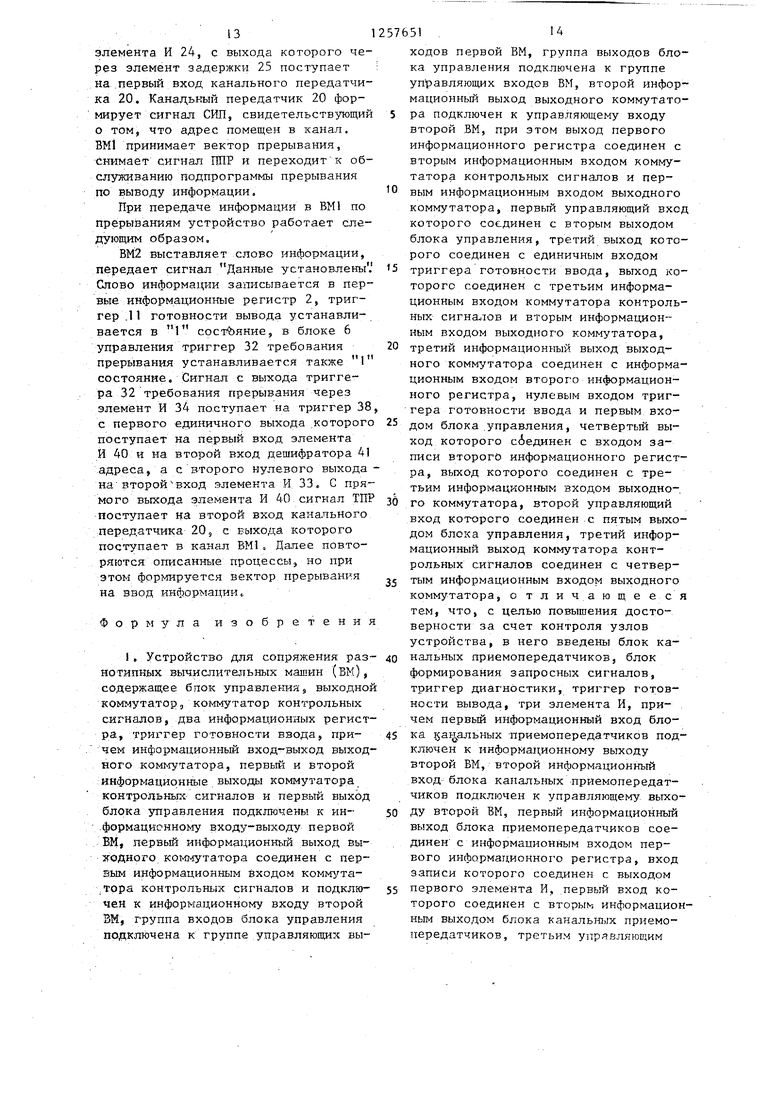

Коммутатор 9 контрольных сигналов содержит (фиг, 5) элементы ИЛИ 51 и 52, элемент И-НЕ 53, .

Блок канальных приемопередатчиков служит для согласования электри - ческих параметров логического нуля и логической единицы по полярности и уровню на стыке устройства с центральной машиной (ВМ2) и за счет этого допускает соединение указанных устройств при любом заданном отличии их элементарных баз и формы электрического представления логических значений. Блок t может быть собран, например, на основе микросхем 293ЛП1,

Триггер 4 диагностики предназначен для организации работы устройства в режиме Диагностика со стороны ВМ2, Единичный выход триггера 4 диагностики соединен с вторым

входом первого элемента И 3 и служит для записи информации в регистр 2. Кроме того, он связан с первым управляющим входом коммутатора 9, служащего для приема потенциала,

разрепшющего прохождение информации, находящейся на его втором информационном входе, первым входом запус- ka блока 8, служащего для запуска формирователя импульсов блока 8, подтверждающего прием информации, и четвертым управляющим входом выходного 7 коммутатора, служащего для приема потенциала изменения направления передачи информации. Нулевой

выход триггера 4 соединен с четвертым информационным входом кoм fyтa- тора 9 и единичный уровень сигнала, находящийся на его выходе, является признаком передачи информации в ре жиме Диагностика со стороны ВМ2, Кроме того, он связан с вторым входом запуска блока 8, служащего для приема Вспомогательного.потенциала при работе устройства в режиме Диагностика.

Блок 8 формирования запускающих Сигналов предназначен для формирования сигналов синхронизации при ра

3

боте устройства в режиме Диагностика. Второй выход блока 8, служащий для выдачи импульса подтверждения приема информации Данные введены, связан с седьмым информационным входом выходного 7 коммутатора. Первый выход блока 8, служащий для передачи сигнала Данные приняты, соединен с третьим входом блока 6 управления и шестым информационным входом выходного 7 коммутатора. Третий выход блока 8 связан с четвертым входом блока 6 управления и первым входом третьего элемента И 10 Четвертый выход блока 8 соединен с пятым входом блока 6 управления и служит для формирования сигнала прерывания программы ВМ2.

Триггер 11 готовности вывода данных служит для индикации наличия информации, передаваемой ВМ2 в вспомогательную машину (ВМ1) в первом информационном регистре 2. Пятый выход блока 6 управления соединен с вторым управлякицим входом выходного 7 коммутатора и служит для вьща- чи сигнала прерывания в ВМ2.

Третий информационный выход коммутатора 9 связан с четвертым инфор мационньш входом выходного 7 коммутатора и служит для выдачи информации в режиме Диагностика, Первый, второй выходы коммутатора 9 подключены к второй шине ввода-вывода информации и служат, соответственно для выдачи в канал разрядов регистра состояния и информации в режиме Диагностика.

На фиг, 2 представ;лен npHMCtp реализации блока 6 управления.

Блок 6 содержит дешифратор 14 управляющих сигналов, первый вход которого подключен к первому входу блока 6, связанного также с первым входом узла 15 дешифрации адреса и информационным входом регистра 16 состояния, второй - К группе входов блоки 6, подключенной также к первому входу узла 17 векторного прерывания, третий, служащий для приема сигнала Устройство выбрано, связан с выходом узла 15 дешифрации адреса. Первый выход дешифратора 14 управляющих сигналов подключен к входу записи регистра 16 состояния, второй - к второму ВХОДУ второго элемента И 18 и. служит для выдачи сигнала требования прерьшания рабо576514

ты ВМ2. Третий выход дешифратора 14 управляющих сигналов связан с четвертым выходом блока 6, четвертый - с вторым, пятьш - с иестым, шестой - 5 с девятым, седьмой - с вторым входом узла 15 детифрации адреса и служит для передачи синхрои тульса (СИл) записи сигнала Устройство выбрано восьмой - с первым входом канально- ° го 20 передатчика и служит для выдачи сигнала синхронизации (СИП). Пер-. вый выход узла 17 векторного прерывания является первым выходом бло- ка 6, второй - восьмым, третий свя- 5 зан с вторым входом канального 20 передатчика и служит для формирования сигналов требования прерывания (ТПР) ВМ1.

Дешифратор 14 управляющих сигна- 20 лов содержит триггер 22 запоминающий, например, младшие разряды адресного слова и первый вход которого является первым входом дешифратора 14 управляющих сигналов, а второй , вход связанный с группой входов блока управления, служит для приема сигнала синхронизации (сил), йлход триггера 22 связан с четвертым входом дешифратора 23, первый и второй вхо- 0 .ды которого связаны с группой вхо- дов блока и служат соответственно для приема сигналов Ввод, Вывод, третий вход дешифратора 23. подключен к третьему входу дешифратора 14 5 управляющих сигналов, 1-6 выходы дептфратора 23 подключены к выходам дешифратора 14 управляющих сигналов и входам элемента И 24, седьмой вход которого связан с группой входов 0 блока и служит для приема сигнала предоставления прерывания (ППР). ВьЬсод элемента И 24 через элемент 25 задержки связан с восьмым выходом дещифратора 14 управляю1цих сигналов.

5 Узел 17 векторного прерывания содержит триггер 32 требования прерывания на ввод, единичньй вход которого связан с третьим входом уз- 17, нулевой вход - выходом эле0 мента И 33 и служит для установки последнего в начальное состояние, а вьгход подключен к второму входу элемента И 34, триггер 35 требования прерьшания на ввод, нулевой вход ко5 торого подключен к четвертому входу узла 17 векторного прерывания, вто- рой - к выходу элемента И 36, служащего для установки триггера 35 в

5

начальное состояние, а выход - второму входу элемента И 37. Первые входы элементов И 34-37 подключены к соответствующим цепям второго входа узла 17 и служат для подачи сиг- налов разрешения прерывания, выходы - к первому и второму единичному входу триггера 38, нулевой вход которого связан с выходом элемента И- НЕ 39, служащего для запоминания сигналов требования прерывания. Первый единичный выход триггера 38 связан с первым входом элемента И 40 и в.торым входом дешифратора адреса 41 второй нулевой, являющийся инверсным выходом первого единичного выхода - с вторым входом элемента И 33, второй единичный - с вторым входом элемента И 36, первьш нулевой являющийся инверсным выходом второго единичного выхода, - с BTOpF iM входом элемента И 40, Кроме того, первый вход элементов И 33, 36, 42 служащий для подачи сигнала представления прерывания (ППР) ВМ1, связан с первым входом узла 17, выход элемента И 42 подключен к первому входу дешифратора 41 адреса, а второй вход элемента И 42 - с первым выхо- .дом элемента И-НЕ 40, являющегося инверсным выходом второго выхода, связанного с третьим выходом узла 17 В начальный момент времени триггер 3 находится в О состоянии, триггер 35 - в 1,

Дешифратор 41 адреса формирует адрес вектора прерывания в зависимости от сигналов, подаваемых на его первый и второй вход, он может представлять, .например, группу элементов И-НЕ, собранную на микросхемах типа 155J1A7,

Устройство работает следующим образом.

Обмен информацией между ЭВМ осу- ществллется программно в режиме оп роса готовности (только для основной ВМ2), или по прерываниям (для обеих), В устройстве предусмотрен режим Диагностика со стороны ВМ1 и ВМ2.

В режиме Диагностика со сторо- :ны ВМ2 устройство работает следующим образом.

Состояние цепи готовности ВМ1 не влияет на режим, ВМ2 выставляет на информационном входе устройства слово информации, которое через блок 1

0

5

0

5

76

,

0

5

0

5

0

5

516

поступает на инфирмацион}тый вход первого 2 информационного регистра и передает по управляющему входу устройства сигнал Диагностика. Сигнал Диагностика устанавливает единичный выход триггера 4 диагностики н О состояние, нулевой - в I, кроме того, через элемент И 5 устанавливает триггер 1I готовности вывода в состояние.

Уровень логического О с единичного выхода триггера 4 диагностики через элемент И 3 поступает на вход записи регистра 2 и производит запись информации, находящейся на его информационном входе.

Одновременно с записью информационного слова ВМ2 в регистр 2 отрицательный перепад сигнала с единичного выхода триггера 4 диагностики производит запуск первого одновибра- тора 49 блока 8. Одновибратор 49 формирует отрицательный импульс, который с его выхода поступает на седьмой информационный вход выходного 7 коммутатора, В выходном 7 коммутаторе он поступает на второй вход второго 44 магистрального передатчика, с первого выхода которого следует в ВМ2 и, получив кото рый, последняя снимает установленные данные.

Одновременно с этим уровень логического О подается на четвертый управляющий вход выходного 7 коммутатора, первый управляющий вход коммутатора 9, где поступает на первый вход второй группы 52 элементов ИЛИ и разрешает прохождение информационного слова ВМ2 через коммутатор 9 на его третий информационный выход, откуда оно поступает на четвертый информационный вход выходного 7 коммутатора.

В выходном 7 коммутаторе информационное слово ВМ2 через первый коммутатор 43 подается на его второй выход и поступает обратно в ВМ2,

Отрицательный импульс, сформированный одновибратором 49 , через второй элемент 50 задержки поступает на пятый -вход блока 6 управления, В блоке 6 управления сигнал через элемент И 2,1 переводит триггер. 19 прерывания в состояние О, При этом на второй управляющий вход выходного коммутатора 7 подается уровень логического О. Уровень логического О в выходном коммутаторе 7 пос7

тупает на пятый вход второго коммутатора 4А и с его второго выхода подается в ВМ2, вызывая прерывание программы, свидетельствуя о том, что данные выведены.

ВМ2 принимает переданное ею раньше информационное слово и передает по управляющему входу устройства сигнал Данные приняты. Сигнал Данные приняты через блок 1 поступает на единичный вход триггера 4 диагностики и разрешающий вход блока 8, в котором подается на дервьй вход элемента ИЛИ 48, При этом триггер 4 диагностики устанавливается в первоначальное состояние 1

Сигнал Данные приняты не проходит через элемент ИЛИ 48, так как длительность этого сигнала (меньше, чем время задержки первого элемента 46 задержки, т.е. в этот момент времени на втором входе элемента ИЛИ 48 находится определяющий потенциал 1.

Одновременно с этим отрицательный перепад сигнала с нулевого выхода триггера 4 диагностики производит запуск второго одновибратора 47. Од- новибратор 47 формирует отрицательный импульс, который через элемент И 10 устанавливает триггер 1 готовности вывода в исходное состояние О, а также поступает на четвертый вход блока 6 управления, устанавливая триггер прерывания в начальное состояние 1.

ВМ2 на основе сравнения переданной и принятой информации делает вывод о состоянии линии передачи информации .

Таким образом контроль работоспособности осуществляется без участия ВМ . В режиме опроса готовности ВМ2 .может работать в двух вспомогательных режимах.

При передаче информации из ВМ2 в ВМ1 с контролем правильности ее прохождения управляющая nporpat Ma ВМ2 анализирует состояние готовности.. Если ВМ1 готова к вводу информации , то она установила триггер 13 готовности ввода в состояние 1. При этом ВМ2 выставляет на информационном входе, устройства слово ин- . формации, которое через блок 1 поступает на информационный вход первого регистра 2 и передает по управ576518

ляющему входу устройства сигнал Диагностика. Далее продолжаются описанные процессы, но при этом управляющая программа ВМ1 производит 5 опрос состояния цепей первого выхода коммутатора 9, Опрос состояния цепей первой выходной шины коммутатора 9 производится канальным циклом Ввод,

10 Порядок выполнения этих операций следующий,

ВМ1 в адресной части цикла пере- . дает по шине ввода-вывода информации

адресное слово канала. Слово посту- 15 пает в .выходной 7 коммутатор, на. вход-выход коммутатора 45, с выхода которого передается на первый вход блока 6 управления. В блоке 6 управления поступает на информационный 20 вход регистра 16 состояния, первый вход узла 15 дешифрации адреса, первый вход дешифратора 14 управляющих сигналов. В адресных разрядах адресного слова записан адрес, присвоен- 25 ный ВМ2.

Адрес ВМ2 задается на этапе проектирования двухмашинного комплеква и формируется путем запайки nepeNbi- чек в гнезде 29 узла 15. По коду ад- 0 реса на выходе элемента И-НЕ 30 по- является сигнал Устройство выбрано который подается на информационный вход триггера 31.

.После установки адресного слрва ВМ1 по группе входов устройства вырабатывает сигнал СИЛ, поступающий на синхровходы триггеров 22 и 31 и вьтолняющий запись информации. После этого ВМ1 снимает адресно|е слово 0 и по группе входов устройства выра батывает сигнал Ввод. Сигнал ВвоД подается на второй вход дешифратора 23.

При опросе состояния цепей nepieo- 5 го информационного выхода коммутатор 9 в младших разрядах адресного слова ВМ1 записывает код, который вместе с сигналом Устройство выбрано приводит к появлению сигнала на 0 тре.тьем выходе дешифратора 2.3. Этот сигнал постулает на второй управляющий вход коммутатора 9 и разрушает прохождение информации, находящейся на его 3, 4, 6 и 7-ом информационных е входах в канал ВМ1 .. Одновременно с этим сигнал с третьего выхода дешифратора 23 через элемент И 24 и элемент задержки 25 поступает на пер9 .

вый вход канального передатчика 20, который формирует сигнал СИП, свидетельствующий о том, что данные ;помещены в канал, и передает его в BMi по группе выходов устройства. ВМ1 принимает сигнал СИП, данные снимает сигнал Ввод и по заднему фронту сигнала СИП снимает сигнал СИА, завершая тем самим канальный 1ЩКЛ Ввод,

На основании анализа принятых данных ВМ1 делает вывод о том, записана информация или нет в первый информационный регистр 2, Еспи информация записана , то ВМ произ- йодит цикл Ввод. На первом выходе деншфратора 23 появляется сигнал, 1которь й поступает на первый управляющий вход выходного коммутатора 7 который связан с первым входом коммутатора 44. При этом данные находящиеся на его втором входе, поступают на его первый вход-выход. Одновременно с этим триггер 11 готовнос ш вывода устанавливается в начальное нулевое состояние.

После того как по управляющему выходу устройства в ВМ2 поступает сигнал Данные введены, ВМ2 снимает информационной слово.

Параллельно с этим происходят процессы, описанш 1е для режима Ди- .агностика со стороны ВМ2, т.е. передаваемая информация принимается ВМ2 и контролируется на правильност прохождения.

Этот режит работы дает дополнительные возможности диагностики неисправностей. Так как в случае передачи известной обеим машинам информации, при неисправности одной из первых входной или выходной линии мозкно сразу локализовать неисправность.

При передаче информации без контроля управлякйцая .программа ВМ2 анализирует состояние управлякнцей выходной шины, а именно цепи готовности. Если ВМ готова к вводу информа щщ, то она установила триггер 3 готовности ввода в состояние 1. При этом НМ2 выстав яет на информа- да1ОЯном входе слово информации, которое через блок поступает на информационный вход первого регистра , и передает по уггравляющему входу сигнал Данные установлены. Сигнал Данные установлены через элемент

5765110

И 3 поступает на вход записи первого информационного регистра 2 и производит запись информации, находящейся на его информационном входе.

5 Одновременно с этим триггер 11 готовности вывода данных сигналом Данные установлены устанавливается в 1 состояние. ВМ1 с помощью канального цикла Ввод опрашивает

состояние цепей первого выхода коммутатора 9. При этом, если в первый информационный регистр 2 записана информация, ВМ1 производит ее ввод с помощью канального цикла Ввод,

5 описанного выше.

В режиме Диагностика со стороны ВМ2 устройство работает соедую- щим образом.

Контроль правильности прохожде20 ния информации происходит при помощи канальных циклов Вывод и Ввод . ВМ1 в адресной части цикла Вывод передает по входу-выходу устройства адресное слово и вырабатывает сиг25 нал СИА. Узел 15 дешифрации адреса депмфрует адрес и по сигналу СИА сигнал Выбор устройства запоминается в триггере 31 узла 15, а млад-, шие разряды адресного слова - в тригЗО гере 22 дешифра:тора 14 управляклцих сигналов. ВМ снимает адресное слово, помещает на вход-выход устройства данные и по группе входов устройства передает сигнал Вывод. Сиг5 нал Вывод поступает на третий вход дешифратора 23 узла 14. В соответствии с кодом, записаига 1м в младших разрядах адресного слова, на пятом выходе дешифратора 23 появляется сиг0 нал который через элемент И 26 поступает на вход записи второго информационного 12 регистра и производит запись информации, находящейся на его информационном входе.

5 Сигнал с пятого выхода дешифратора также поступает на элемент И 24, с выхода которого через элемент 25 задержки поступает на первый вход канального 20 передатчика, который

0 формирует сигнал СИП.

ВМ1, получив сигнал СИП, снимает сигнал Вывод, установленные данные и сигнал СИА. Информация, запи- . санная во второй регистр 2 через

5 первый коммутатор 43, поступает на его выход. Далее ВМ производит цикл Ввод. При этом код, записан-. ный в младших разрядах адресного ело-

11

ва, соответствует шестому выходу дешифратора 23 узла 14. Сигнал с шестого выхода дешифратора 23 через элемент НЕ 27 поступает на вход коммутатора 9 на первый вход первой группы элементов ИЛИ 51. Данные, находяпщеся на ее втором входе и поступающие туда с информационного .выхода устройства, подаются в канал ВМ1.

ВМ1 принимает переданную раньше информацию, анализируют ее и делают заключение о правильности прохождения информации через вход-выход устройства, выходной коммутатор 7, второй информационный регистр 12, коммутатор 9.

В режиме обмена информацией по прерываниям устройство работает следующим образом.

Инициатор обмена - вспомогательная машина. Этот режим обмена является для нее единственным режимом передачи информации. Обмен происходит при помощи описанного канального цикла Вывод, При этом код, передаваемый в младший разряд адресного слова соатветствует четвертому выходу дешифратора 23, узла 14, При появлении сигнала на четвер том выходе дешифратора 23 происходит запись информации во второй информационный регистр 12, и установка триггера 19 прерывания блока 6 в 1 состояние. При этом на втором выходе второго коммутатора 44 появляется сигнал прерывания программьт, поступающей в ВМ2,

При передаче информации с контролем правильности ее прохождения ВМ1 производит канальный цикл Ввод, При этом код, записанный в младших разрядах адресного слова соответствует шестому выходу дешифратора 23 узла 14, Сигнал с шестого выхода дешифратора 23 через элемент НЕ 27 поступает на третий управлякщий вход коммутатора 9, в котором следует на первый вход первой группы элементов ИЛИ 51 , При этом данные,, находя- щиеся на ее втором входе и поступающие туда с выхода второго информационного регистра 12 через первый коммутатор 43, поступают в канал ВМ1 ВМ1 принимает переданную ей информа- цию и на основе ее анализа делает заключение о правильности ее прохождения ,

20

25

0 s

to

15

25765112

ВМ2, получив сигнал прерывания, принимает переданные ВМ1 данные и передает по управляющему входу устройства сигнал Данные приняты, : который поступает на третий вход блока 6 управления и устанавливает триггер 19 прерывания в начальное О состояние,.

Инициатор обмена - основная машина, В ВМ1 принята векторная система прерывания. Адрес вектора прерывания при поступлении требования прерывания на ввод или вывод информации различен и записан в дешифраторе 41 адреса узла 17, При работе в режиме прерьшания ВМ1 во время канального цикла Вывод производит в регистр 16 состояния, разрещающие ВМ1 ввод или вывод информации в режиме прерывания. При этом на первый вход элемента И 34 узла I7 поступает потенциал, разрешающий или запрещающий работу ВМ по вводу информации в режиме прерывания, а на первый . элемент И 3.7 - по выводу информации ВМ2 передает требование прерывания на вывод информации сигналом Данные приняты, который через блок 1, элемент ИЛИ 48 блока 8 поступает на третий вход блока 6 управления и устанавливает триггер 35 требования прерьгеания в О состояние,

Сигнал требования прерывания с выхода триггера 35 через элемент И

37, триггер 38 предоставления прерывания, элемент И 40 поступает на второй вход канального передАтчи- ка 20, с выхода которого поступает в канал ВМ1.

Процессор ВМ1 удовлетворяет требования, вырабатьтая сигнал предоставления прерьгеания (ППР), Сигнал ППР поступает на второй Вход дешифратора 14 управляющих сигналов и первый вход узла 17. В узле 17 он через элемент НЕ 39 поступает на нулевой вход триггера 38 предоставления прерывания, который запоминает требования прерывания, С выхода элемента И 36 сигнал 1 поступает на единичный вход триггера 35, устанавливая его в состояние 1, Дешифратор 41 адреса помещает адрес вектора на первый выход узла 17 векторного перемещения, связанного с входом- выходом ВМ1 .;

в дешифраторе 14 управляющий сиг- ; нал ШТР поступает на четвертый вход

30

3S

40

5

13

лемента И 24, с выхода которого чеез элемент задержки 25 поступает i а, .первый вход канального передатчиа 20. Канадькый передатчик 20 форирует сигнал СИП, свидетельствующий том, что адрес помещен в канал. М1 принимает вектор прерывания, снимает сигнал ГЩР и переходит к обслуживанию подпрограммы прерывания о выводу информации.

При передаче информации в ВМ1 по прерываниям устройство работает слеующим образом,

ВМ2 выставляет слово информации, передает сигнал Данные установлены . Слово информации записывается в первые информационные регистр 2, триггер .11 готовности вывода устанавли- вается в 1 состояние, в блоке 6 управления триггер 32 требования прерывания устанавливается также состояние. Сигнал с выхода триггера 32 требования прерывания через элемент И 34 поступает на триггер 38, с первого единичного выхода .которого поступает на первый вход элемента И 40 и на второй вход дешифратора 41 .адреса, а с второго нулевого выхода - на второй вход элемента И 33, С прямого выхода элемента И 40.сигнал ТПР поступает на второй вход канального передатчика 205 с выхода которого поступает в канал ВМ1, Далее повторяются описанные процессы, но при этом формируется вектор прерыван1ля на ввод информации

Формула изобретения

I. Устройство для сопряжения разнотипных вычислитет ьных машин (ВМ), содержащее бпок управленияj выходной коммута.торз коммутатор контрольных сигналов, два информационных регистра, триггер готовности ввода, при- чем информационный вход-выход выходного коммутатора, первьга и второй информационные выходы коммутатор.а контродьньпс- сигналов и первый выход блока управления подключены к ин- .формационному входу-выходу первой БМ, первый информационный выход вы- згодного ко1-о.1утатора соединен с пер- з.ым информационным входом коммута- .тора контрольных сигналов и подключен к информационному входу второй ВМ, группа входов блока управления подключена к группе управляющих вы12

257651

ходов первой ВМ,

14

10

15

20

25

группа выходов блока управления подключена к группе управляющих входов ВМ, второй информационный выход выходного коммутатора подключен к управляющему входу второй 5М, при этом выход первого информационного регистра соединен с вторым информационным входом коммутатора контрольных сигналов и первым информационным входом выходного коммутатора, первый управляющий вход которого соединен с вторым выходом блока управления, третий выход которого соединен с единичным входом триггера готовности ввода, выход которого соединен с третьим информационным входом коммутатора контрольных сигна юв и вторым информационным входом выходного коммутатора, третий информационный выход выходного коммутатора соединен с информационным входом второго информационного регистра, нулевым входом триг- гера готовности ввода и первым входом блока .управления, четвертый выход которого сбединен с входом записи второго информационного регистра, выход которого соединен с третьим информационным входом выходного коммутатора, второй управляющий вход которого соединен с пятым выходом блока управления, третий информационный выход коммутатора контрольных сигналов соединен с четвертым информационным входом выходного коммутатора, отлич.агащееся тем, что, с целью повышения достоверности за счет контроля узлов устройства, в него введены блок ка- 40 нальных приемопередатчиков, блок формирования запросных сигналов, триггер диагностики, триггер готовности вывода, три элемента И, при- . чем первый информационный вход блока цар альных Приемопередатчиков подключен к информационному выходу второй БМ, второй информационный вход блока канальных приемопередатчиков подключен к управляющему, выходу второй ВМ, первый информационный выход блока приемопередатчиков соединен с информационным входом первого информационного регистра, вход записи которого соединен с выходом первого элемента И, первый вход которого соединен с вторым информационным выходом блока каналы-п 1х приемопередатчиков, третьим управляющим

30

35

45

50

55

15

входом выходного KOMhfyraTopa, вторы входом блока управления, первым входом второго элемента И, выход которого соединен с единичным входом триггера готовности вывода, единич- ньй выход которого соединен с пятым информационным входом.выходного коммутатора, шестой информационге 1Й вход которого соединен с третьим входом блока управления и с первым выходом запроса блока формирования запросных сигналов, вход разрешения которого соединен с единичным входом триггера диагностики и третьим информационным выходом блока канальных приемопередатчиков, четвертый информационный выход которого соединен со вторым входом второго элемента И и нулевым входом триггера диагностики, единичный выход которого соединен с вторым входом первого элемента И, первым входом запуска блока формирования запросных сигналов, первым управляющим входом коммутатора контрольных сигналов, четвертым управляющим входом выходного коммутатора, седьмой информационный вход которого соединен с вторым выходом запроса блока формирования запросных сигналов, второй вход запуска которого соединен с нулевым выходом триггера диагностики, четвертым информационным входом коммутатора контрольных сигналов, второй управляюрдий вход которого соединен с шестым выходом блока управления, четвертый вход которого соединен с третьим выходом запуска блока формирования запросных сигналов и первым входом третьего элемента И, выход которого соединен с нулевым входом триггера готовности вывода, нулевой выход которого соединен с пятым информационным входом кoм fryтaтopa контрольных сигналов, шестой и седьмой информационные входы которого соединены с седьмым и восьмым выходами блока управления соответствен но, девятый выход которого соединен с третьим управляющим входом комыу- тат.ора управляющих сигналов, четвертый выход запроса (5лока формирования запросных сигналов соединен с пятым входом блока управления, второй выход которого соединен с вторы входом третьего элемента И, причем блок управления содержит два дешифратора адреса, дешифратор команд.

257651

16

шесть триггеров, регистр состояния, группу канальных передатчиков, десять элементов И, два элемента НЕ, элемент задержки, причем информа- 5 ционный вход регистра состояния соединен с информационным входом первого дешифратора адреса, информационным входом первого триггера и является первым входом блока управления, 0 единичный вход второго триггера является вторым входом блока управления, нулевой вход третьего триггера соединен с первым входом первого элемента И и является тр етъин входом 5 блока управления, первый вход второго элемента И является четвёртым входом блока управления, второй .вход первого элемента И является пятым входом блока управления, выход 20 второго дешифратора адреса является первым выходом блока управления, первый выход дешифратора команд соединен с первым входом третьего элемента И и является вторым выходом блока управления, второй выход дешифратора команд соединен с вторым входом третьего элемента И, с входом записи регистра состояния и является третьим выходом блока управления, 0 выход четвертого элемента И являет- ся четвертым выходом блока управления, единичный выход четвертого триггера является пятым выходом блока управления, третий выход дешифрато- 5 ра команд соединен с третьим входом третьего элемента И и является шестым выходом блока управления, нулевой выход четвертого триггера является седьмым выходом блОка управле- 0 ния, выход регистра состояния соединен с первыми входами пятого и шестого элемента И и является восьмым выходом блока управления, выход первого элемента НЕ является девятым вы 5 ходом блока управления, вход второ- - го элемента НЕ. первые входы седьмого, восьмого, девятого элементов И, четвертый вход третьего элемента И, первый, второй входы дешифратора 0 команд, синхровходы первого и пятого триггеров образуют группу входов блока управления, выходы канальных передатчиков группы образуют группу выходов блока управления, при этом в блоке управления выход первого дешифратора адреса соединен с информационным входом пятого триггера, вьтуод которого соединен с третьим

17

входом дешифратора команд, четвертый вход которого соединен с выходом первого триггера, четвертЬш выход дешифратора команд соединен с пятым входом третьего элемента И, первым входом четвертого элемента И и вторым входом второго элемента И, выход KOTOpioro соединен с единичным входом четвертого триггера, нулевой вход которого соединен с выходом первого элемента И, второй вход четвертого элемента И соединен с пятым выходом дешифратора команд и шестым входом третьего элемента И, седьмой вход которого соединен с шестым выходом дешифратора команд и входом первого элемента НЕ, выход третьего элемента И соединен с входом элемента sajfiepjRKH, выхой которого соединен с первым информационным входом канальных передатчиков группы, второй информационный вход которых соединен с прямь1м выходом десятого элемента И,, инверсный выход которого соединен с вторым входом девятого элемента И, выход которого соединен с nepBfcjM входом второго дешифратора адреса, второй вход которого соединен с первым едииичным выходом шес- таго триггера и первым входом десятого элемента И, второй вход которого соединен с первым нулевым выходом шестого триггера, второй нулево ВЫХОД которого соединен с вторым вводом седьмого элемента И, выход которого соединен с нулевьш входом второго триггера, выход которого соединен с вторым входом пятого элемента И, выход которого, соединен с

5765118

первым единичным входом шестого триггера, второй.единичный выход которого соединен с вторым входом восьмого элемента И, выход которого соединен 5 с единичным входом третьего триггера, выход которого соединен с вторым входом шестого элемента И, выход которого соединен с вторым единичным входом шестого триггера, ну- 10 левой вход которого соединен с выходом второго элемента НЕ.

2. Устройство по п. 1, о т л и- чающееся тем, что блок мирования эапросньрс сигналов содержит два одновибратора, два элемента задержки, элемент ИЛИ, причем вход первого одновибратора является первым входом эапуска блока формирова2Q ння эапросных си налов, вход второго одновибратора соединен с входом первого элемента задержки и является вторьш входом запуска блока формирования запросных сигналов, первый

25 вход элемента ИЛИ является входом разрешения блока формирования запросных сигналов, выход элемента ИЛИ является первым выходом блока формирования запросных сигналов, выход

JQ первого одновибратора соединен с входом второго элемента задержки и является вторым выходом блока формирования запросных сигналов, выходы второго одновибратора и второго элемента задержки являются третьим и четвертым выходами блока формирования запросных сигналов, выход первого элемента задержки соединен с вторым входом элемента ИЛИ,

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1179312A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для контроля движения транспортных средств | 1987 |

|

SU1538178A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для сопряжения большой ЭВМ высокой производительности с микро-ЭВМ при построении локальных вычислительных сетей. Основной зйдачей изобретения является повьппение достоверности за счет контроля узлов устройства со стороны двух ЭВМ. Устройство содержит блок управления, выходной коммутатор, коммутатор контрольных сигналов, блок канальных приемо-. передатчиков, блок формирования запросных сигналов, два информационных регистра, триггер диагностики, триггеры готовности ввода и вывода, три элемента И. 1 з.п. ф-лы, 5 ип. (О Nd СП

| Устройство для связи центральной и периферийных цифровых вычислительных машин | 1976 |

|

SU661543A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-12-04—Подача