Изобретение относится к вычислительной технике и может быть использовано при проектировании многомашинных иерархических вычислительных систем.

Цель изобретения расширение функциональных возможностей за счет обеспечения возможности обмена информацией между разнотипными ЭВМ.

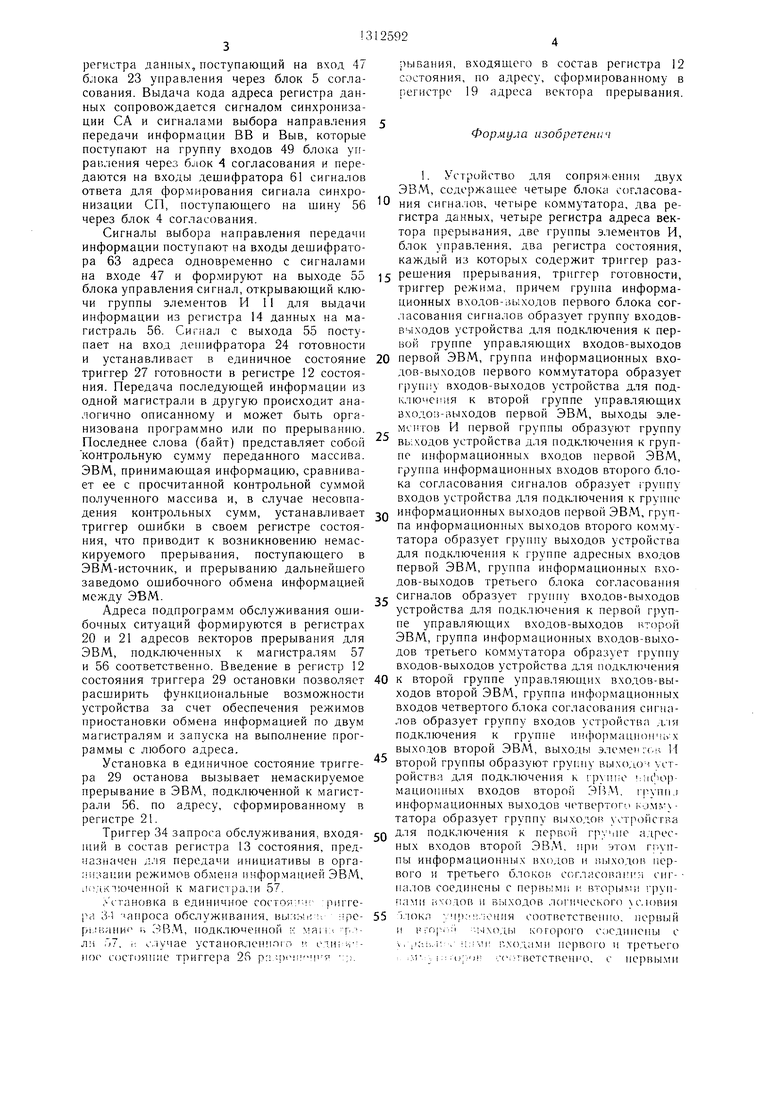

На фиг. 1 приведена схема устройства; на фиг. 2 схема блока управления.

Устройство содерж-ит блоки 1-5 согласования сигналов, коммутаторы 6-9, группы элементов И 10 и 11, регистры 12 и 13 состояния, регистры 14 и 15 данных, вход 16 блока 2, элементы ИЛИ 17 и 18, регистры 19-22 адреса вектора прерывания, блок 23 управления, дешифраторы 24 и 25 готовности.

Регистр 12 состояния содержит триггеры разрешения прерывания 26, готовности 27, режима 28, остановки 29 и ошибки 30.

Регистр 13 состояния содержит триггеры разре1пепия прерывания 31, готовпости 32, режима 33, запросы обслуживания 34 и ошибки 35.

Блок 23 управления имеет входы 36-45 логического условия и группы входов 46-49 логических условий, группы выходов 50, 51 логических условий, выходы 52-55, шипы 56 и 57 первой и второй ЭВМ, регистры 58 и 59 прерывания, дешифраторы 60 и 61 сигналов ответа и дешифраторы 62 и 63 адреса.

Устройство работает следующим образом. В первоначальный момент времени все последовательностпые элементы устройства приводятся в исходное состояние (цепи обнуления условно не показаны).

Сигнал от первой ЭВМ, подключенной, например, к магистрали 56, устанавливает в единичное состояние триггер 33 режима регистра 13 состояния, сообщая о своей готовности к приему информации: начальном адресе и объеме передаваемого или принимаемого массива данных.

Сигнал с выхода три1ч-ера 33 режима поступает в дешифратор 24 готовности и устанавливает в единичное состояние триггер 27 готовпости регистра 12 состояния, которое может быть считано в магистраль 57 через коммутатор 6.

При поступлении от второй ЭВ.М сигнала разре1пения прерывания через магистраль 57 триггер 26 разреп1ения прерывания в регистре 12 состояния устанавливается в единичное состояние. Наличие двух условий: единичное состояние триггеров готовности и разрешения нрерывания, вызывает формирование в регистре 58 прерывания сигнала ЭП, который через блок 1 согласования поступает в магистраль 57. Получив сигнал ЭП, вторая ЭВМ выставляет ответный сигнал РП, который через блок 1 согла сования поступает в блок управления и зы- зывает формирование сигналов ЗН, Г1Б, Г Р

0

5

0

5

0

5

0

в регистре нрерывания, а также сигналом с выхода 53 стробирует выдачу вектора прерывания, хранящегося в регистре 19 адреса вектора нрерывания, в магистраль 57 через ко: 1мутатор 7. При переходе на выполнение подпрограммы обработки прерывания вторая ЭВМ выставляет на линии магистрали 57 код адреса регистра 14 данных, ноступающий на вход 46 блока 23 управления через блок 2 согласования. Выдача кода адреса регистра данных сопровождается сигналами синхронизации СЗ выбора операции УО и У1, которые поступают на группу входов 48 блока 23 управления через блок 1 согласования и нередаются на входы дешифратора 60 сигналов ответа для формирования сигнала синхронизации СИ, поступающего в шипу 57 через блок 1 согласования.

Сигналы выбора операции УО и У1 поступают па входы ден1ифратора адреса одно- временно с сигналами па входе 46. Сигнал, сформированный на выходе 52 блока 23 управления, стробирует прием информации из магистрали 57 в регистр 14 данных через блок 3 согласования. Одновременно сигнал с выхода 52 поступает в дешифратор 25 г отовности,, в котором уже хранится информация об установленном в единичное состояние триггере 33 режима регистра 13 состояния. Наличие этих двух условий вызывает установку в единичное состояние триггера 32 готовности в регистре 13 состояния, которое может быть считано в шипу 56 через коммутатор 8.

При ноступлении от первой ЭВЛ, подключенной к магистрали 56, сигнала разрешения прерывания триггер 31 разрен ения прерывания в регистре 13 состояния устанавливается в единичное состояние.

Наличие двух условий: единичное состояние триггеров готовности и разре1нения ирерывания, вызывает формирование сигнала ТП в регистре 59 прерывания, который через блок 4 согласования поступает в магистраль 56. Первая ЭВМ формирует ответный сигнал ПП, который через блок 4 согласования поступает па группу входов 49 блока 23 управлепия.

Сигпал ПП поступает на вход дешифратора 61, в котором формируется сигнал синхронизации СП, выдаваемый на один из грунпы выходов 50 блока управления. Этот сигнал поступает па шину 56 через блок 4 согласовапия. Одновременно сигнал ПП поступает на вход регистра 59 ферывания, в котором формируется сигнал,поступающий на выход 54 блока управления и стро- б-ирующий выдачу вектора прерывания, хра- няп1,егося в регистре 22 адреса вектора ирерывания, в магистраль 56 через коммутатор 9.

При переходе па выполнение подпрограммы обработки прерывания первая ЭВЛ выставляет на линии niuHbi 5() код адреса

регистра данных, поступающий на вход 4/ блока 23 управления через блок 5 согласования. Выдача кода адреса регистра данных сопровождается сигналом синхронизации СА и сигналами выбора направления передачи информации ВВ и Выв, которые поступают на группу входов 49 блока уп- рав;1ения через блок 4 согласования и передаются на входы дешифратора 61 сигналов ответа для формирования сигнала синхронизации СП, поступающего на шину 56 через блок 4 согласования.

Сигналы выбора направления передачи информации поступают на входы дешифратора 63 адреса одновременно с сигналами на входе 47 и формируют на выходе 55 блока управления сигнал, открывающий ключи группы элементов И 11 для выдачи информации из регистра 14 данных на магистраль 56. Сигнал с выхода 55 поступает на вход ден ифратора 24 готовности и устанавливает в единичное состояние триггер 27 готовности в регистре 12 состояния. Передача последующей информации из одной магистрали в другую происходит аналогично описанному и может быть организована программно или по прерыванию. Последнее слова (байт) представляет собой контрольную сумму переданного массива. ЭВМ, принимающая информацию, сравнивает ее с просчитанной контрольной суммой полученного массива и, в случае несовпадения контрольных сумм, устанавливает триггер ощибки в своем регистре состояния, что приводит к возникновению немаскируемого прерывания, поступающего в ЭВМ-источник, и прерыванию дальнейшего заведомо ошибочного обмена информацией между ЭВМ.

Адреса подпрограмм обслуживания ошибочных ситуаций формируются в регистрах 20 и 21 адресов векторов прерывания для ЭВМ, подключенных к магистралям 57 и 56 соответственно. Введение в регистр 12 состояния триггера 29 остановки позволяет расширить функциональные возможности устройства за счет обеспечения режимов приостановки обмена информацией по двум магистралям и запуска на выполнение программы с любого адреса.

Установка в единичное состояние триггера 29 останова вызывает немаскируемое прерывание в ЭВМ, подключенной к магистрали 56, по адресу, сформированному в регистре 21.

Триггер 34 запроса обслуживания, входящий в состав регистра 13 состояния, пред- ИгЗЗ 1ачен для передачи инициативы в орга- ; за1;ии режимов обмена информацией ЭВМ, ;1;|ДК оченной к магис1ри,И 57.

Уп ановка в единичное состоя: - ригге- р 3-i «апроса обслуживания, Bbi:ib i: ;. :фе- ринани i ЭВЛА, подключепно : Maii:-. п лм Г;7, г. с.гучае установлсн Ю г. . еди; :-,- ио( состояние триггера 2vS pa ч) :;.

рывания, входящего в состав регистра 12 состояния, по адресу, сформированному в регистре 19 адреса вектора прерывания.

Формула изобретенпч

1. Устройство для сопряжения двух ЭВМ, содерм ащее четыре блока согласования сигна/юв, четыре коммутатора, два ре5

гистра данных, четыре регистра адреса вектора прерывания, две группы элементов И, блок управления, два регистра состояния, каждый из которых содержит триггер раз5 решения прерывания, триггер готовности, триггер режима, причем группа информационных в одов-15ыходов первого блока согласования сигналов образует группу входов- вь1ходов устройства для подключения к первой группе управляющих входов-выходов

0 первой ЭВМ, группа информационных входов-выходов первого коммутатора образует группу входов-выходов устройства для подключения к второй группе управляющих входо; -выходов первой ЭВМ, выходы элементов И первой группы образуют группу выходов устройства для подключения к группе информационных входов первой ЭВМ, группа информационных входов второго блока согласования сигналов образует группу входов устройства для подключения к группе

Q информационных выходов первой ЭВМ, группа информационных выходов второго коммутатора образует группу выходов устройства для подключения к группе адресных входов первой ЭВМ, группа информационных входов-выходов третьего блока согласования

с еигналов образует группу входов-выходов устройства для подключения к первой группе управляющих входов-выходов l тopoй ЭВМ, группа информационных входов-выходов третьего коммутатора образует группу входов-выходов устройства для подключения

0 к второй группе управляюп1их входов-выходов второй ЭВМ, группа информационных входов четвертого блока согласова}1ия сигналов образует группу входов устройства д.чя подключения к группе ин(|10рмацион о-х выходов второй ЭВМ, выходы элемеи л.; И

второй группы образуют группу выходом устройства для подключения к rpyin-io :;ц|,ор- мациопных входов второй ЭВМ, iTynnj информационных выходов четвертого ьомг. татора образует группу выходог устройства

Q для подключения к первой гручие адресных входов второй ЭВМ при этом гпуп- пы информацио}1ных входов и выходов первого и третьего блоков согласовшм-н сиг- палов соединены с первым -, и вторь1ми группами ;(--:(;дов и выходов логического условия

5 |локл ).: |;лоиия соответственно, первый

и Fi r;| r::i --.ЫХОД KOTOpOl O СОСМИ i ICinj С

,i. ;;.i . . i;:;N n г,.о,и1ми иервого И третьего : м J, i:; .ч.т-ветственио. с первыми

входами элементов И первой и второй групп соответственно, синхровходом второго блока согласования сигналов и синхровходом иор- вого регистра данных соответственно, первьи информационный выход иервого коммутатора соединен с синхровходом триггера раз решения ирерывания первого регистра состояния, выход которого соединен с первым информационным входом первого коммутатора и первым входом логического условия блока управления, второй вход .логического условия которого соединен с вторым информационным входом первог О коммутатора, выходом триггера готовности первого регистра состояния и с информационным входом первого регистра адреса вектора прерывания, выход которого соединен с первым информационным входом второго коммутатора, управляющий вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с управляющим входом четвертого коммутатора, первый информационный вход которого соединен с выходом второго регистра адреса вектора прерывания, второй информационный выход первого коммутатора соединен с синхровходом триггера режима первого регистра состояния, выход которого соединен с третьим информационным входом первого коммутатора, третьим входом логического условия блока управления и первым информационным входом третьего коммутатора, первый ин(})ормационный выход которого соединен с синхровходом три|тера разрешения прерывания второго регистра состояния, выход которого соединен с вторым информационным входом третьего коммутатора и с четвертым входом логического условия блока управления, пятый вход логического условия которого соединен с четвертым информационн1)1м входом первого коммутатора, третьим информационным входом третьего коммутатора и с. выходом триггера режима второго регистра состояния, синхровход которого соединен с вторым информационным выходом третьего коммутатора, четвертый информационный вход которого соединен с выходом триггера готовности второго регистра состояния и с шестым входом логического условия блока управления, третья группа входов логического условия которого соединена с группой информационных выходов второго блока согласования каналов и с группой информационных входов второго регистра данных, группа выходов которого соединена с вторыми входами элементов И второй группы, вторые входы элементов И первой группы соединены с группой выходов перво 0 регистра данных, группа информационных входов которого соединена с группой информационных выходов четвертого блока согласования сигналов, отличающееся тем, что, с целью расширени.я функциональных возможностей за счет обеспечения обмена ин0

формацией между разнотипными ЭВМ, в него введены два дсп1ифраго а готовности, .iBn э.сме1.га ИЛИ, пягьи блок согласования ciM 1-;алов. в нервый регистр состояния введены триггер 3;iiip(-a обслуживания

и триггер он1ибки, а во второй регистр состояния введены триггер сч тановки и триггер ошибки, причем группа информационных входов пятого блока согласования сигналов образует группу входов устройства

для подключения к второй группе адресных выходов второй ЭВМ, при этом группа информационн151х выходов пятого блока согласования сигналов соединена с четвертой группой входов логического условия блока управления, седьмой вход логического

5 условия которого соединен с пятым информационным входом первого коммутатора, первым входом первого элемента ИЛИ и с выходом триггера ошибки второго регистра состояния, синхровход которого соединен с третьим ин(|юрмациопным выходом третьего коммутатора, пятый информационный вход которого соединен с информационным входом второго регистра адреса вектора прерывания с восьмым входом логического условия блока управления, и с выходом триггера ошибки

5 первого регистра состояния, синхровход которого соединен с третьим информационным выходом первого коммутатора, шестой информационный вход которого соединен с девятым входом логического условия блока управления, выходом триггера останова

0 второго регистра состояния и с вторым входом первого элемента ИЛИ, выход которого соединен с информационным входом третьего регистра адреса вектора прерывания, выход которого соединен с вторым информационным входом второго коммута5 тора, четвертый информационный выход первого коммутатора соединен с синхровходом триггера запроса обслуживания первого регистра состояния, выход которого соединен с седьмым информационным входом первоQ го коммутатора, десятым входом логического условия блока управления, 1нестым информационным входом третьего коммутатора, первым входом второго элемента ИЛИ. выход которого соединен с информационным входом четвертого регистра адреса

5 вектора прерывания, выход которого соединен с вторым информационным входом четвертого коммутатора, первый выход блока управления соединен с первыми информационными входами первого и второго дишифра- торов готовности, вторые информационные

0 входы которых соединены с вторым выходом блока управления, третьи и четвертые информационные входы первого и второго дешифраторов готовности соединены с выходами триггеров режима первого и второго регистров состояния соответственно, выходы первого и второго депшфраторов готовности соединены с синхровходами триггеров готовности первого и второго регистров состоя5

ния соответственно, второй вход второго элемента ИЛИ соединен с выходом триггера готовности второго регистра состояния. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит два регистра прерывания, два дешифратора сигналов ответа, два дешифратора адреса, причем первый, второй, третий и четвертый информационные входы первого регистра прерывания являются четвертым, шестым, седьмым и девятым входами логического условия блока управления, первый информационный выход первого регистра прерывания является четвертым выходом блока управления, второй, третий, четвертый и пятый информационные выходы первого регистра прерывания и выход первого дешифратора сигналов ответа образуют вторую группу выходов логического условия блока управления, первый, второй, третий информационные входы первого дешифратора сигналов ответа и пятый информационный вход первого регистра прерывания образуют вторую группу входов блока управления, группа информационных входов первого дешифратора адреса образует четвертую группу входов логического условия блока управления, первые выходы второго и первого дешифраторов адреса являются первым и вторым выходами блока управления соответственно, первый информационный выход второго регистра прерывания является третьим выходом блока управления, первый, второй, третий информационные входы второго регистра прерывания

являются первым, вторым, восьмым входами логического условия блока управления, второй ннфо)мациоиный выход второго регистра прерын.шия и выход второго

дешифратора сигналов ответа обра:п ют первую груи11 выходов логического условия блока управления, первый, второй, третий информационные входы второго деши4)рато- ра сигналов ответа и первый информационный вход второго дешифратора адре0 са образуют первую группу входов логического условия блока управления, группа информационных входов второго дешифратора адреса образует третью группу входов логического условия блока управления, при

,. этом в блоке управления шестой и седьмой информационные входы первого регистра прерывания соединены с четвертым и пятым информационными входами второго регистра прерывания соответственно, шестой информационный вход которого соединен с

0 первым информационным входом второго дешифратора сигналов ответа, второй и третий информационные входы которого соединены с вторым и третьим информационными входами второго дешифратора адреса, второй вход которого соединен с управ5 ляющим входом второго дешифратора сигналов ответа, второй выход первого дешифратора адреса соединен с управляющим входом первого дешифратора сигналов ответа, первый и второй информационные входы которого соединены с первым и вто- рым информационными входами первого дешифратора адреса соответственно.

Редактор Н. Гунько Заказ 1844/48

Составитель С. Пестман

Техред И. ВересКорректор Л, Обручар

Тираж 673Иод|1ис1И)1

ВНИИПИ Государственного комитета СССР по Д1Ма.м инобретени и открытий

1 13035, Москва, Ж-35, Раушская наб.. л. 4;о Производственно-полиграфическое предприятие, г. жгород, ,i. Проектная, t

Фиг. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1984 |

|

SU1257651A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1312591A1 |

| Устройство для сопряжения двух магистралей | 1982 |

|

SU1111147A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для обмена информацией двух электронно-вычислительных машин | 1984 |

|

SU1231507A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании многомашинных иерархических вычислительных систем. Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности обмена информацией между разнотипными ЭВМ. Устройство содержит блок управления, четыре коммутатора, пять блоков согласования сигналов, два дешифратора готовности, два регистра состояния, два регистра данных, четыре регистра адреса вектора прерывания, две группы элементов И, два элемента ИЛИ. Устройство обеспечивает сопряжение разнотипных магистралей, работает в режимах приостановки и запуска и обеспечивает контроль правильности передаваемой информации. 1 3. п. ф-лы, 2 ил. со ьо СП со N3

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух магистралей | 1982 |

|

SU1111147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1986-01-14—Подача