(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Устройство для сопряжения двух магистралей | 1982 |

|

SU1111147A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения цифровой вычислительной машины с линиями связи | 1983 |

|

SU1166123A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании многомашин- ньт вычислительных систем. Целью изобретения является повышение быстродействия. Устройство содержит четыре блока согласования, блок управления, шесть коммутаторов, два регистра слова состояния, четьфе регистра адреса вектора прерьшания, два регистра данных, два счетчика адреса. 2 з.п. ф-лы, 7 ил.

4

О

сд

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании многомашинных вычислительных систем,

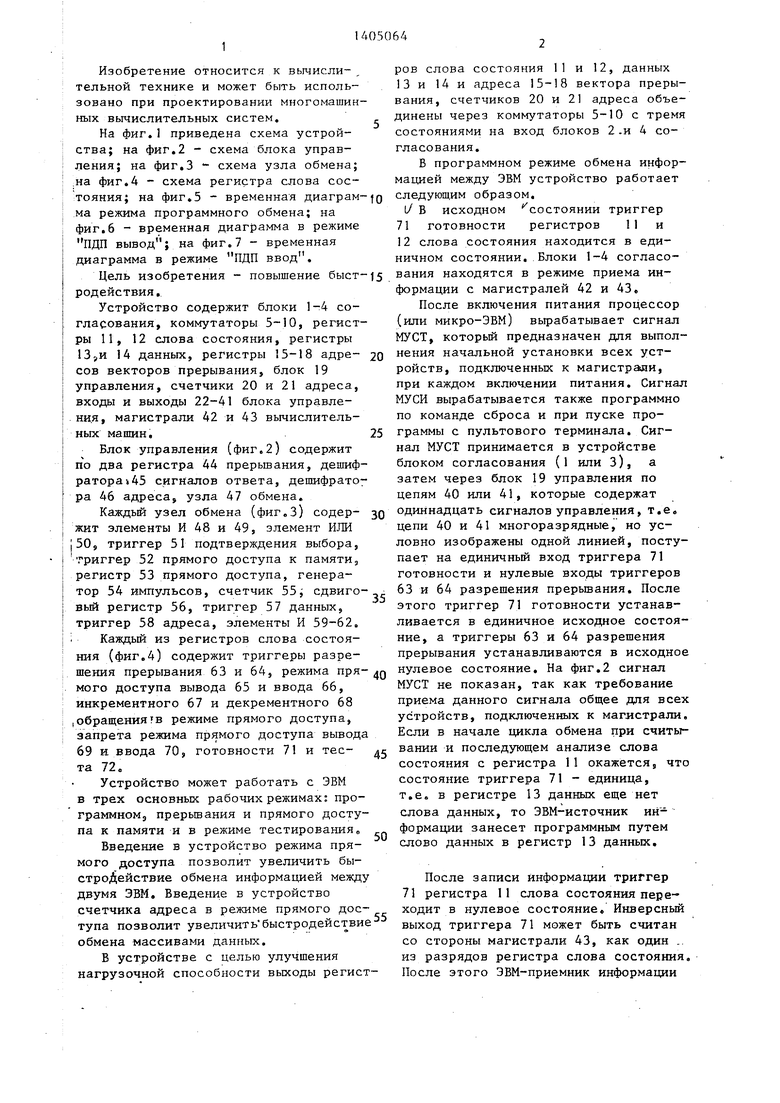

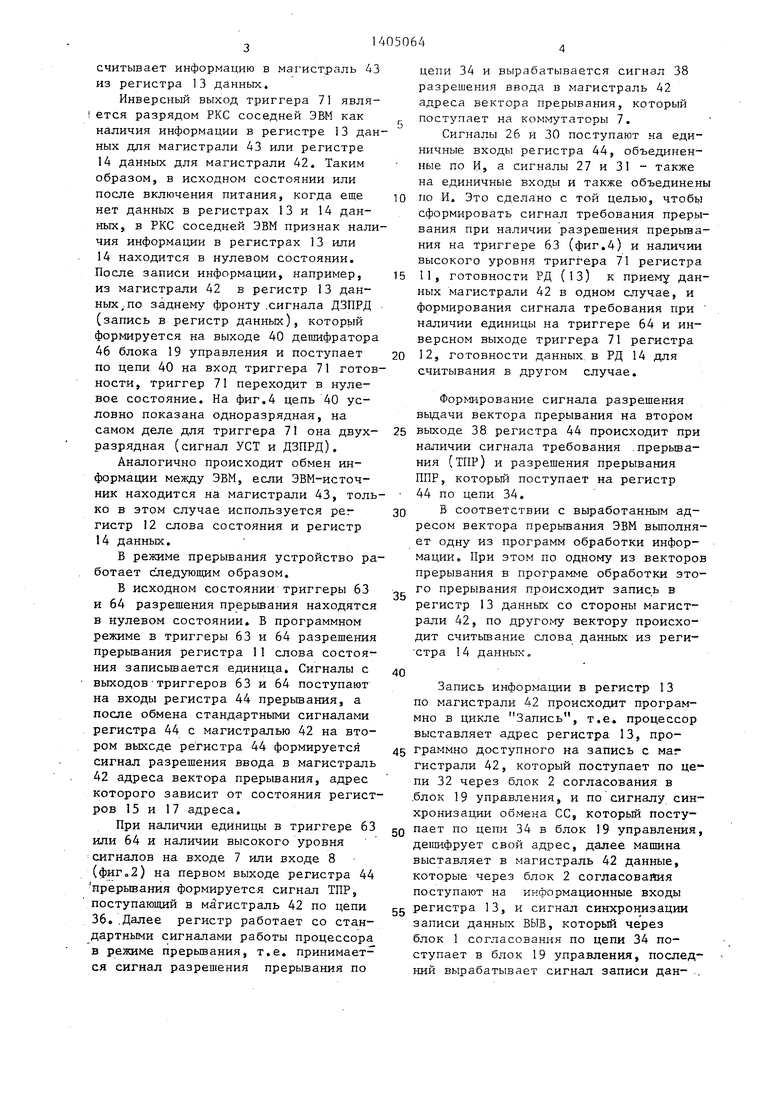

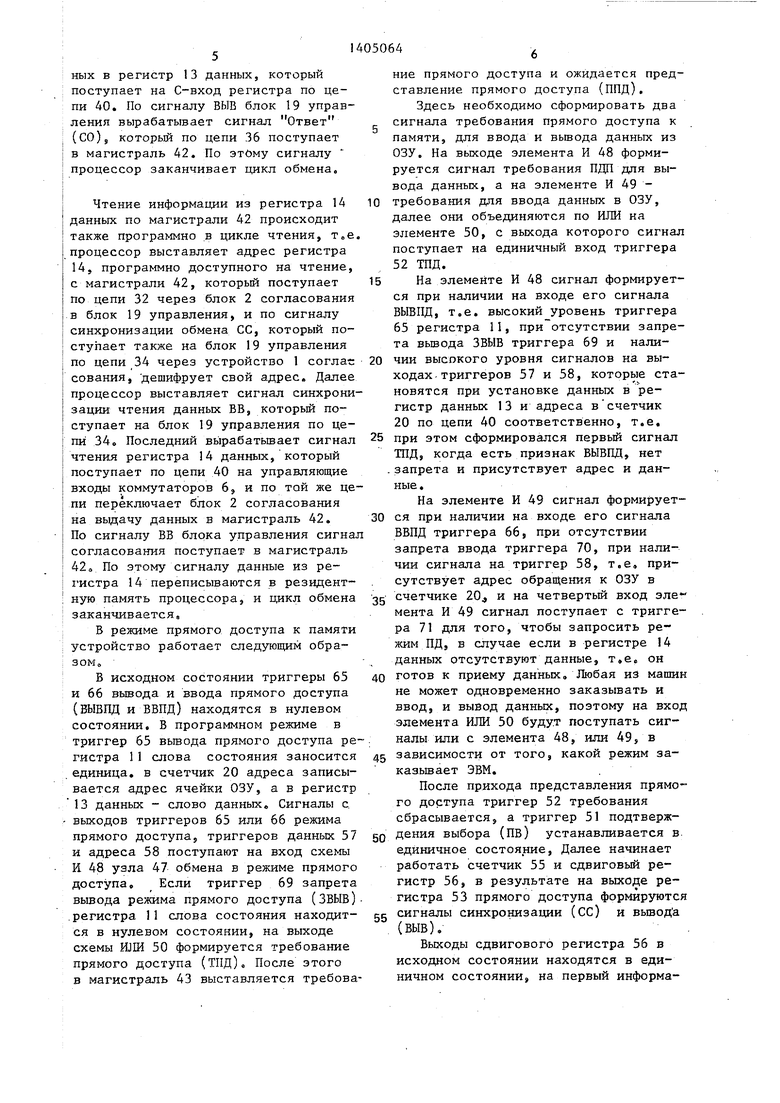

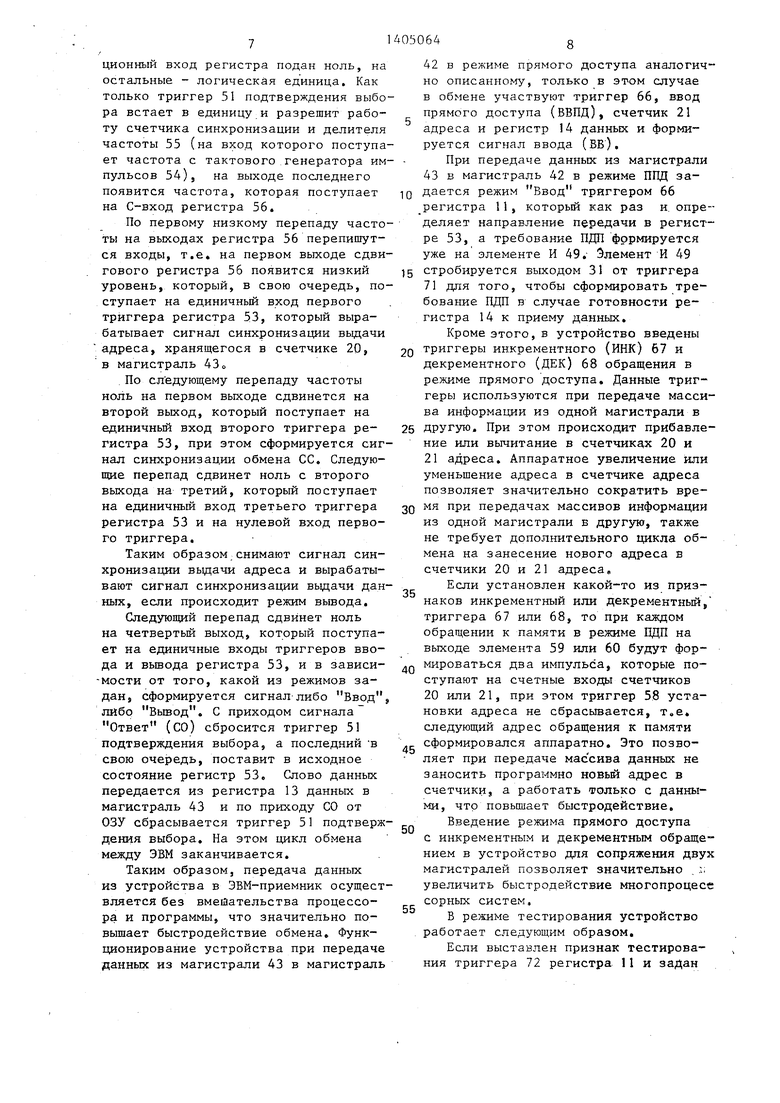

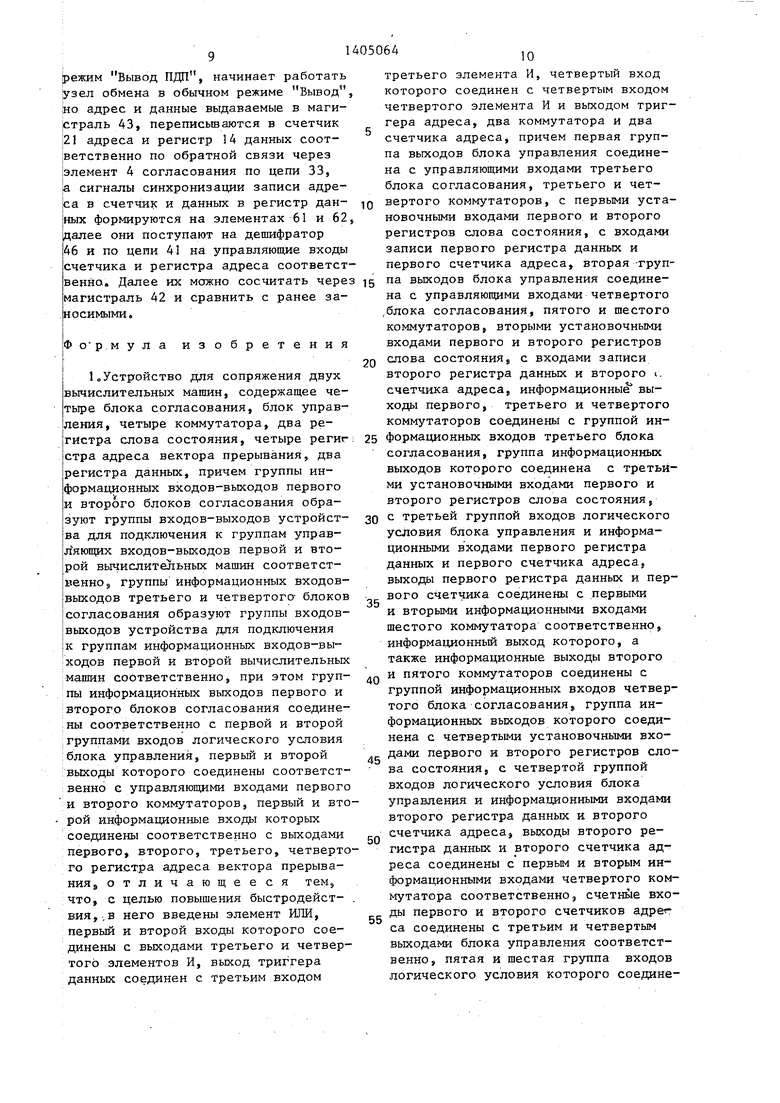

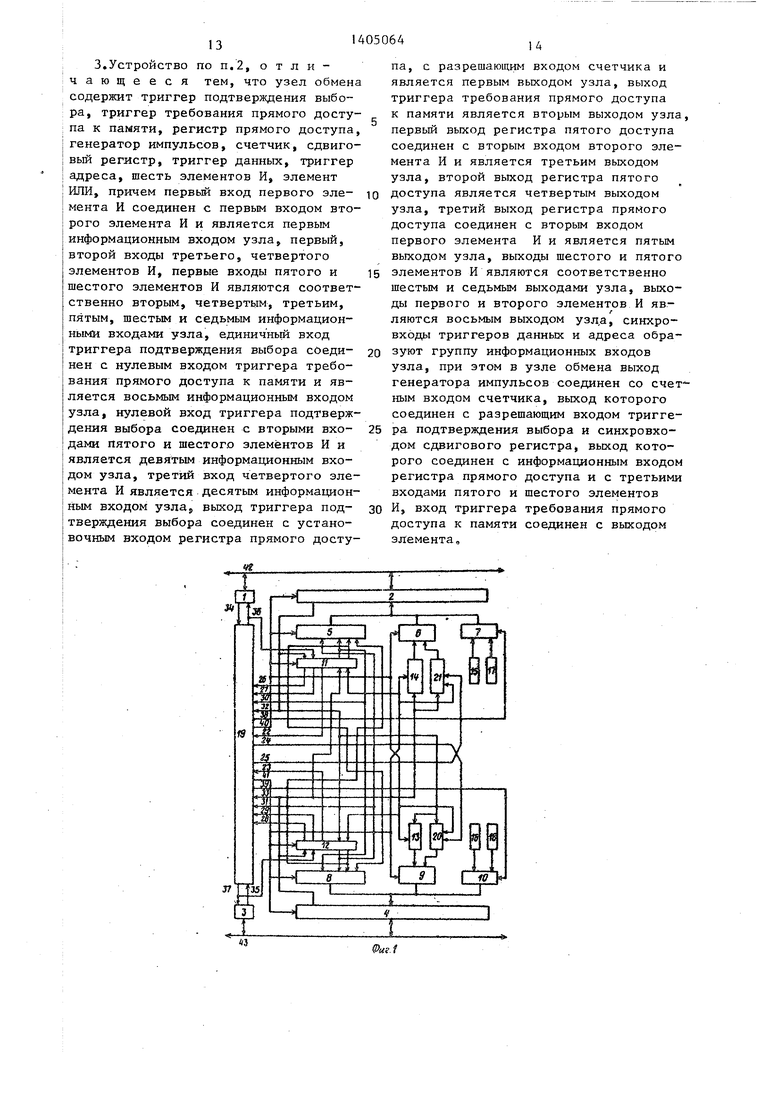

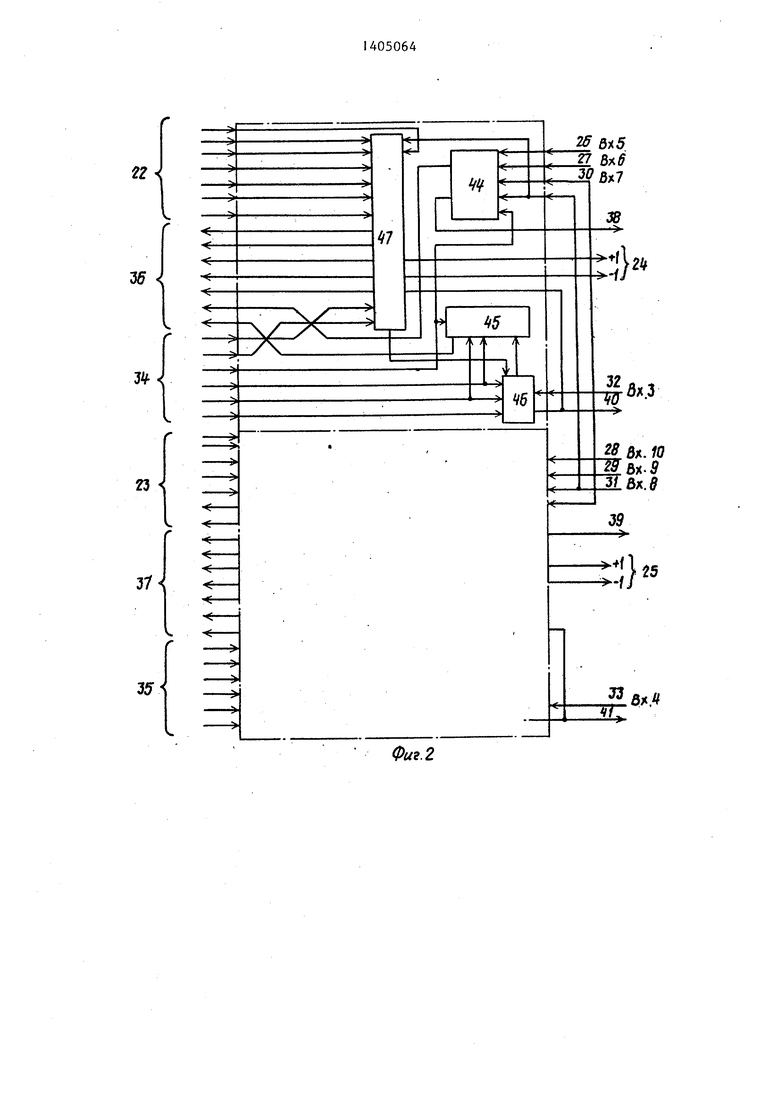

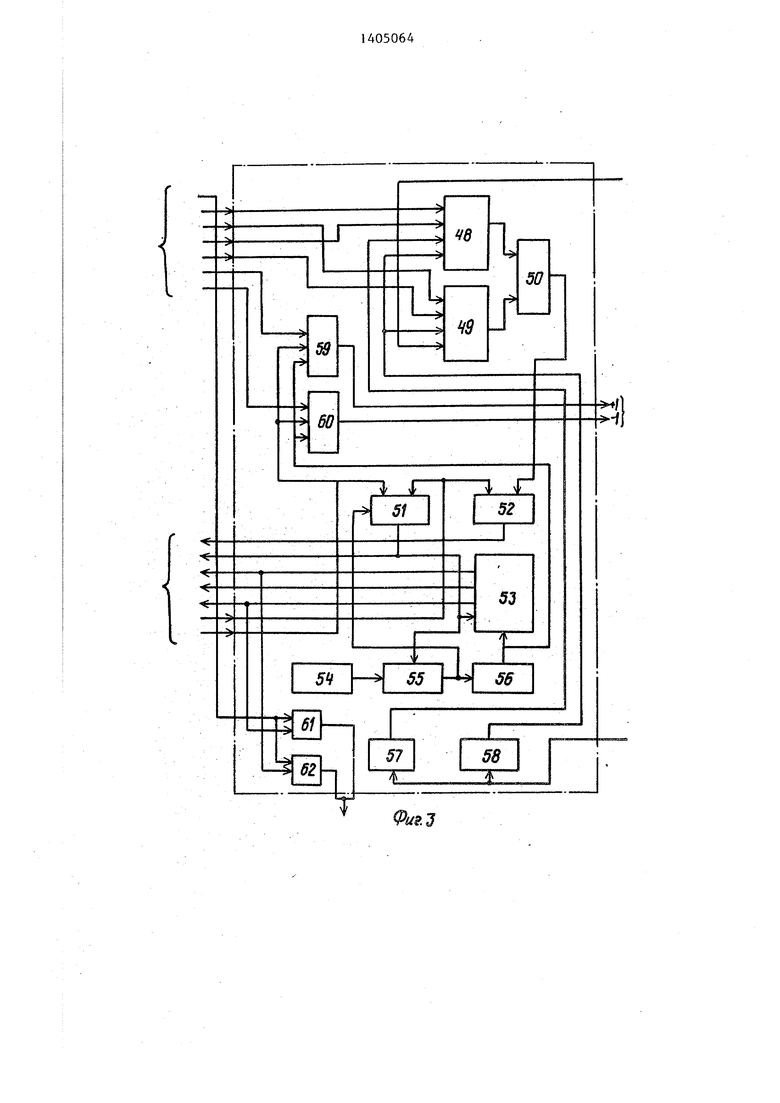

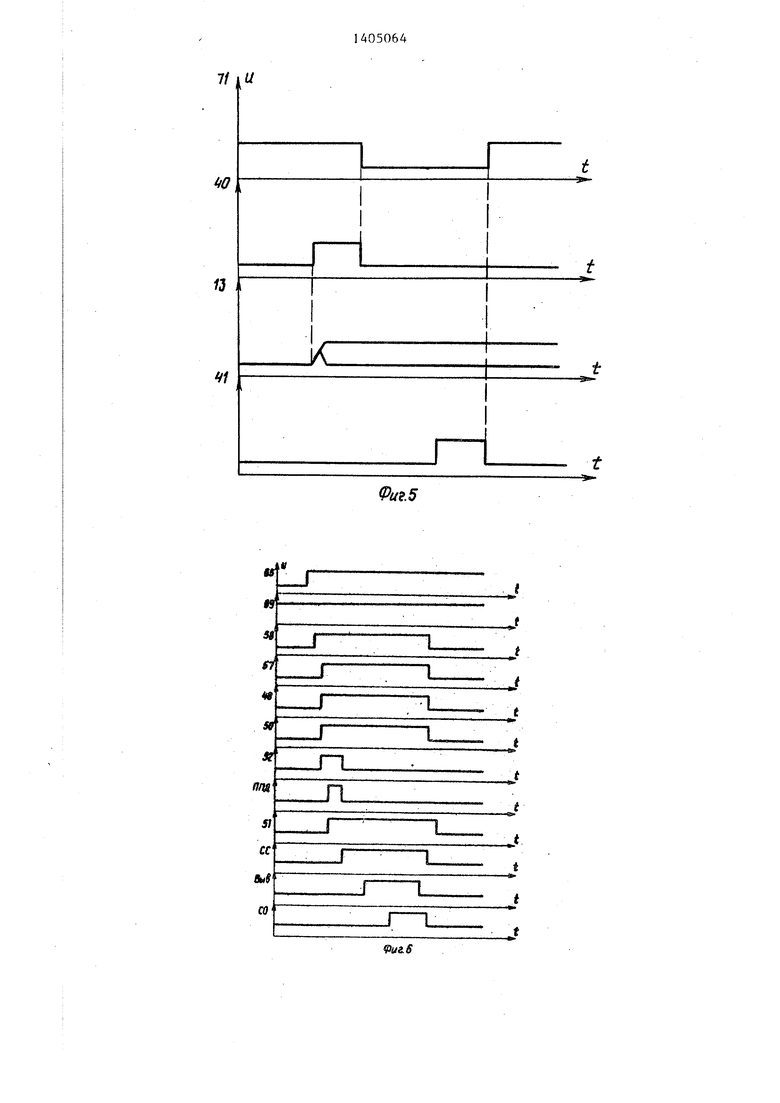

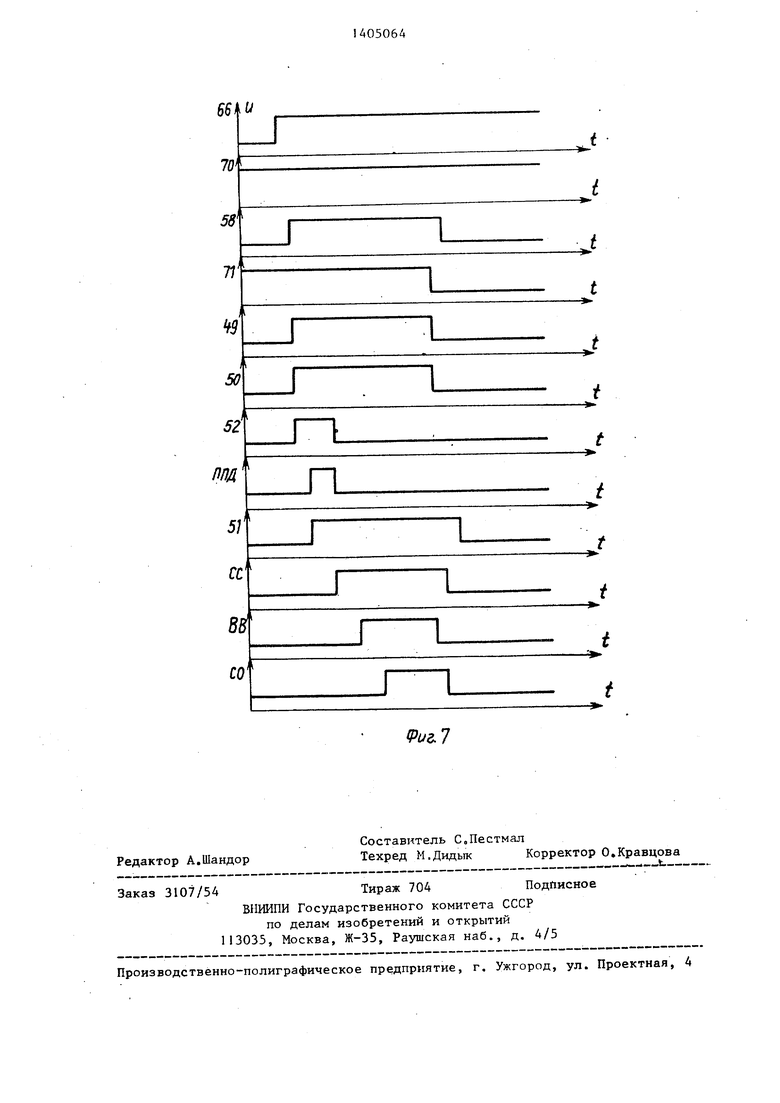

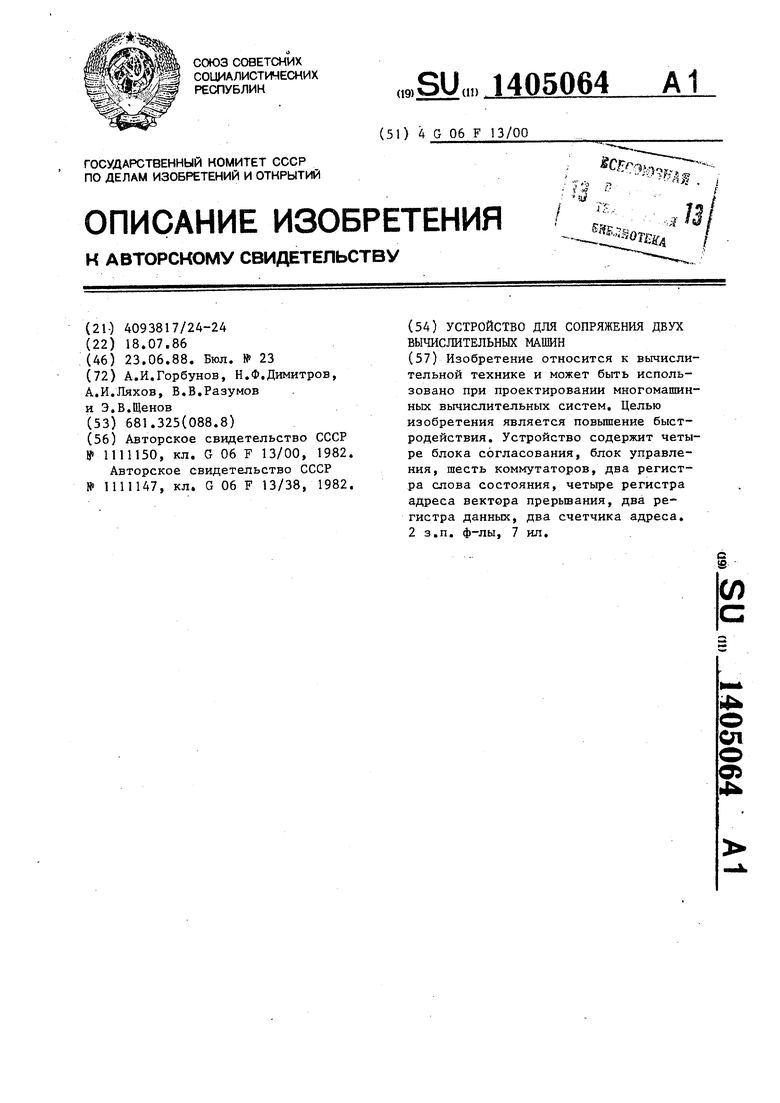

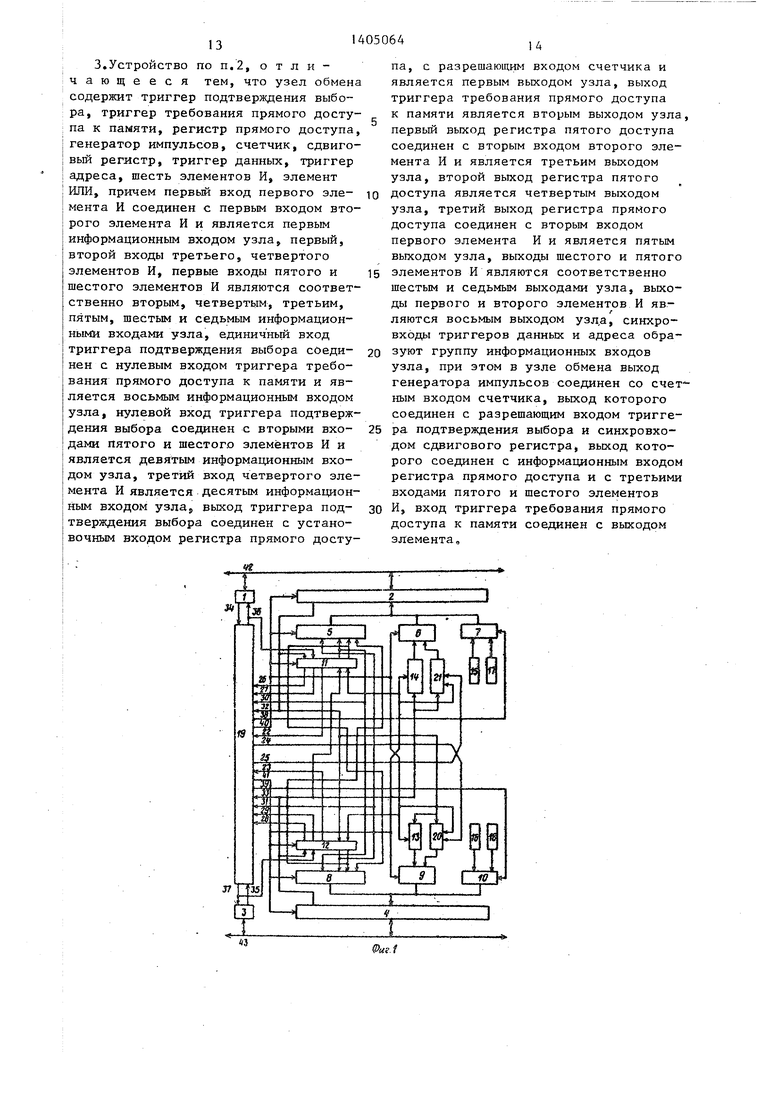

На фиг. приведена схема устройства; на фиг.2 - схема блока управления; на фиг.З - схема узла обмена; .на фиг.4 - схема регистра слова состояния; на фиг.З - временная диаграмма режима программного обмена; на фиг,6 - временная диаграмма в режиме ПДП вывод ; на фиг,7 - временная диаграмма в режиме ПДП ввод.

Цель изобретения - повышение быстродействия.

Устройство содержит блоки 1-4 согласования, коммутаторы 5-10, регистры 11, 12 слова состояния, регистры 13,и 14 данных, регистры 15-18 адре- сов векторов прерывания, блок 19 управления, счетчики 20 и 21 адреса, входы и выходы 22-41 блока управления, магистрали 42 и 43 вычислительных машин,

Блок управления (фиг,2) содержит по два регистра 44 прерьшания, дешифратора k 45 сигналов ответа, дешифратора 46 адреса, узла 47 обмена.

Каждьй узел обмена (фиг.З) содер- жит элементы И 48 и 49, элемент ИЛИ 1509 триггер 51 подтверждения выбора, триггер 52 прямого доступа к памятиj регистр 53 прямого доступа, генератор 54 импульсов, счетчик 55, сдвиговый регистр 56, триггер 57 данных, триггер 58 адреса, элементы И 59-62.

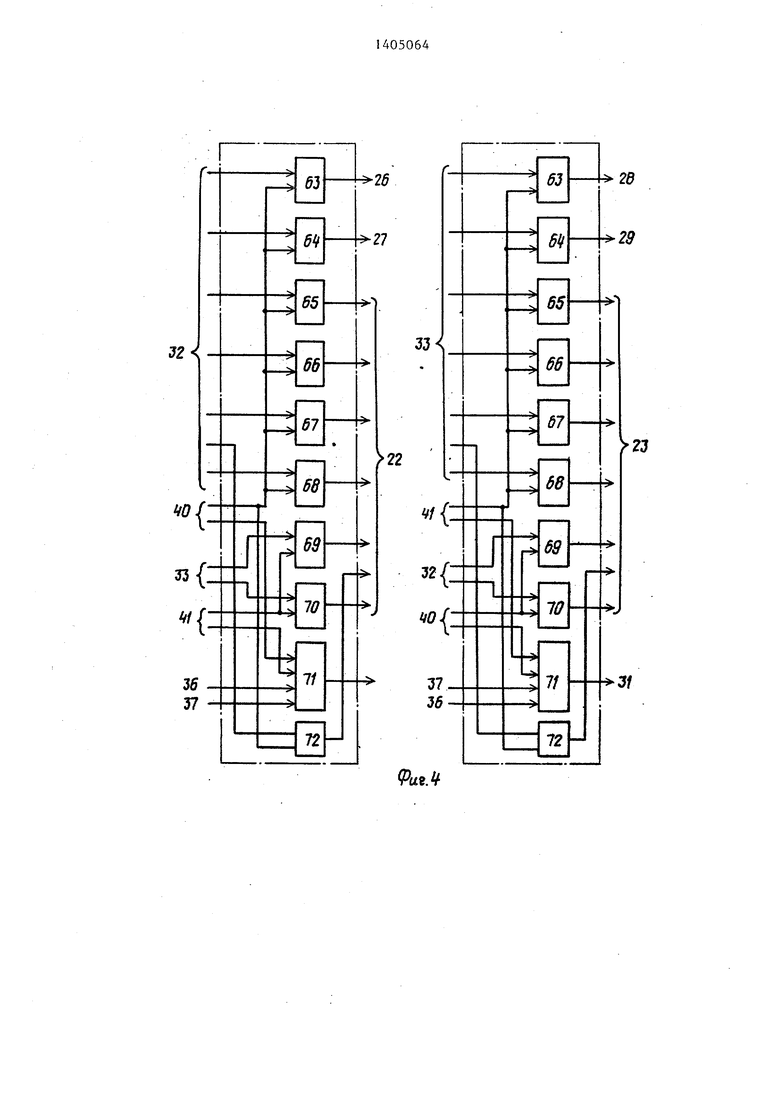

Каждый из регистров слова состояния (фиг.4) содержит триггеры разрешения прерывания 63 и 64, режима пря- мого доступа вывода 65 и ввода 66, инкрементного 67 и декрементного 68 I обращения гв режиме прямого доступа, запрета режима прямого доступа вывода 69 и ввода 70, готовности 71 и тес- та 72,

Устройство может работать с ЭВМ в трех основных рабочих режимах: программном, прерьшания и прямого досту

па к памяти и в режиме тестирования

Введение в устройство режима прямого доступа позволит увеличить бы- строДействие обмена информацией между двумя ЭВМ, Введение в устройство счетчика адреса в режиме прямого доступа позволит увеличить быстродействие обмена массивами данных,

В устройстве с целью улучшения нагрузочной способности выходы регист

д

5

0 5

о

д

5

0

ров слова состояния 11 и 12, данных 13 и 14 и адреса 15-18 вектора прерывания, счетчиков 20 и 21 адреса объединены через коммутаторы 5-10 с тремя состояниями на вход блоков 2.и 4 согласования.

В программном режиме обмена информацией между ЭВМ устройство работает следующим образом.

L/ В исходном состоянии триггер 71 готовности регистров 11 и 12 слова состояния находится в единичном состоянии. Блоки 1-4 согласования находятся в режиме приема информации с магистралей 42 и 43.

После включения питания процессор (или микро-ЭВМ) вырабатывает сигнал МУСТ, который предназначен для выполнения начальной установки всех устройств, подключенных к магистрали, при каждом включении питания. Сигнал МУСИ вырабатывается также программно по команде сброса и при пуске программы с пультового терминала. Сигнал МУСТ принимается в устройстве блоком согласования (1 или З), а затем через блок 19 управления по цепям 40 или 41, которые содержат одиннадцать сигналов управления, т.е. цепи 40 и 41 многоразрядные, но условно изображены одной линией, поступает на единичный вход триггера 71 готовности и нулевые входы триггеров 63 и 64 разрешения прерьшания. После этого триггер 71 готовности устанавливается в единичное исходное состояние, а триггеры 63 и 64 разрешения прерывания устанавливаются в исходное нулевое состояние. На фиг,2 сигнал МУСТ не показан, так как требование приема данного сигнала общее для всех устройств, подключенных к магистрали, Если в начале цикла обмена при считывании и последующем анализе слова состояния с регистра 11 окажется, что состояние триггера 71 - единица, т.е. в регистре 13 данных еще нет слова данных, то ЭВМ-источник информации занесет программным путем слово данных в регистр 13 данных.

После записи информации триггер 71 регистра 11 слова состояния переходит в нулевое состояние Инверсный выход триггера 71 может быть считан со стороны магистрали 43, как один .. из разрядов регистра слова состояния, После этого ЭВМ-приемник информации

считывает информацию в магистраль 43 из регистра 13 данных.

Инверсный выход триггера 71 является разрядом РКС соседней ЭВМ как наличия информации в регистре 13 данных для магистрали 43 или регистре 14 данных для магистрали 42, Таким образом, в исходном состоянии или после включения питания, когда еще нет данных в регистрах 13 и 14 данных, в РКС соседней ЭВМ признак наличия информации в регистрах 13 или 14 находится в нулевом состоянии. После записи информации, например, из магистрали 42 в регистр I3 данных,, по заднему фронту .сигнала ДЗПРД . (запись в регистр данных), который формируется на выходе 40 дешифратора 46 блока 19 управления и поступает по цепи 40 на вход триггера 71 готовности, триггер 71 переходит в нулевое состояние. На фиг,4 цепь 40 условно показана одноразрядная, на самом деле для триггера 7 она двухразрядная (сигнал УСТ и ДЗПРД),

Аналогично происходит обмен информации между ЭВМ, если ЭВМ-источник находится на магистрали 43, только Б этом случае используется per гистр 12 слова состояния и регистр 14 данных,

В режиме прерывания устройство работает следующим образом,

В исходном состоянии триггеры 63 и 64 разрешения прерьшания находятся в нулевом состоянии. В программном режиме в триггеры 63 и 64 разрешения прерьтания регистра 11 слова состояния записьшается единица. Сигналы с выходовтриггеров 63 и 64 поступают на входы регистра 44 прерьтания, а после обмена стандартными сигналами регистра 44 с магистралью 42 на втором выходе регистра 44 формируется сигнал разрешения ввода в магистраль 42 адреса вектора прерывания, адрес которого зависит от состояния регистров 15 и 17 адреса.

При наличии единицы в триггере 63 или 64 и наличии высокого уровня сигналов на входе 7 или входе 8 (фиГв2) на первом выходе регистра 44 прерывания формируется сигнал ТПР, поступающий в магистраль 42 по цепи 36. .Далее регистр работает со стандартными сигналами работы процессора в режиме прерьшания, т,е. принимается сигнал разрешения прерывания по

0

5

5

0

цепи 34 и вырабатывается сигнал 38 разрешения ввода в магистраль 42 адреса вектора прерывания, который поступает на коммутаторы 7,

Сигналы 26 и 30 поступают на единичные входы регистра 44, объединенные по И, а сигналы 27 и 31 - также на единичные входы и также объединены по И, Это сделано с той целью, чтобы сформировать сигнал требования прерывания при наличии разрешения прерьшания на триггере 63 (фиг,4) и наличии высокого уровня триггера 71 регистра

11,готовности РД (13) к приему данных магистрали 42 в одном случае, и формирования сигнала требования при наличии единицы на триггере 64 и инверсном выходе триггера 71 регистра

12,готовности данных, в РД 14 для считывания в другом случае.

Формирование сигнала разрешения выдачи вектора прерывания на втором выходе 38 регистра 44 происходит при наличии сигнала требования .прерьшания (ТПР) и разрешения прерывания ППР, которьш поступает на регистр 44 по цепи 34,

В соответствии с выработанным адресом вектора прерывания ЭВМ вьтолня- ет одну из программ обработки информации. При этом по одному из векторов прерывания в программе обработки этого прерывания происходит запись в регистр 13 данных со стороны магистрали 42, по другому вектору происхо.- дит считьюание слова данных из реги- стра 14 данных«

0

Запись информации в регистр 13 по магистрали 42 происходит программно в цикле Запись, т,е. процессор выставляет адрес регистра 13, про5 граммно доступного на запись с маг гистрали 42, который поступает по пи 32 через блок 2 согласования в .блок 19 управления, и по сигналу синхронизации обмена СС, который посту0 пает по цепи 34 в блок 19 управления, дешифрует свой адрес, далее машина выставляет в магистраль 42 данные, которые через блок 2 согласовайия поступают на информационные входы

g регистра 13, и сигнал синхрон изации записи данных ВЫВ, который через блок 1 согласования по цепи 34 поступает в блок 19 управления, последний вырабатывает сигнал записи дан- ,,

5

входы коммутаторов 6, пи переключает блок 2

ных в регистр 13 данных, который поступает на С-вход регистра по цепи 40, По сигналу ВЫВ блок 19 управления вырабатывает сигнал Ответ (со), который по цепи 36 поступает в магистраль 42. По этому сигналу процессор заканчивает цикл обмена.

Чтение информации из регистра 14 данных по магистрали 42 происходит также программно в цикле чтения, т,е процессор выставляет адрес регистра 14, программно доступного на чтение, с магистрали 42, который поступает по цепи 32 через блок 2 согласования в блок 19 управления, и по сигналу синхронизации обмена СС, который поступает также на блок 19 управления по цепи 34 через устройство 1 соглаг сования, дешифрует свой адрес. Далее процессор выставляет сигнал синхронизации чтения данных ВВ, которьш поступает на блок I9 управления по цепи 34о Последний вырабатьшает сигнал чтения регистра 14 данных, который поступает по цепи 40 на управляющие

и по той же це согласования на выдачу данных в магистраль 42. По сигналу ВВ блока управления сигнал согласования поступает в магистраль 42,, По этому сигналу данные из регистра 14 переписываются в резидентную память процессора, и цикл обмена заканчивается,

В режиме прямого доступа к памяти устройство работает следующим образом

В исходном состоянии триггеры 65 и 66 вывода и ввода прямого доступа (ВЫВПД и ВВПД) находятся в нулевом состоянии, В программном режиме в триггер 65 вывода прямого доступа регистра 1 1 слова состояния заносится единица, в счетчик 20 адреса записывается адрес ячейки ОЗУ, а в регистр 13 данных - слово данных. Сигналы с выходов триггеров 65 или 66 режима прямого доступа, триггеров данньк 57 и адреса 58 поступают на вход схемы И 48 узла 47 обмена в режиме прямого доступа. Если триггер 69 запрета вывода режима прямого доступа (ЗВЫВ) .регистра 11 слова состояния находится в нулевом состоянии, на выходе схемы И)Ш 50 формируется требование прямого доступа (ТПД), После этого в магистраль 43 выставляется требова

5

0

5

0

5

ние прямого доступа и ожидается представление прямого доступа (ППД),

Здесь необходимо сформировать два сигнала требования прямого доступа к памяти, для ввода и вьшода данных из ОЗУ. На выходе элемента И 48 формируется сигнал требования ПДП для вывода данных, а на элементе И 49 - требования для ввода данных в ОЗУ, далее они объединяются по ИЛИ на элементе 50, с выхода которого сигнал поступает на единичный вход триггера 52 ТПД.

На элементе И 48 сигнал формируется при наличии на входе его сигнала ВЫВПД, т.е. высокий уровень триггера 65 регистра 1I, при отсутствии запрета вьшода ЗВЫВ триггера 69 и наличии высокого уровня сигналов на выходах, триггеров 57 и 58, которые становятся при установке данньсс в регистр данных 13 и адреса в счетчик 20 по цепи 40 соответственно, т.е. при этом сформировался первый сигнал ТПД, когда есть признак ВЫВПД, нет запрета и присутствует адрес и данные .

На элементе И 49 сигнал формируется при наличии на входе его сигнала ВВПД триггера 66, при отсутствии запрета ввода триггера 70, при наличии сигнала на триггер 58, т.е. присутствует адрес обращения к ОЗУ в счетчике 20. и на четвертый вход эле

0

5

мента И 49 сигнал поступает с триггера 71 для того, чтобы запросить режим ПД, в случае если в регистре 14 данных отсутствуют данные, т.е., он готов к приему данных. Любая из машин не может одновременно заказывать и ввод, и вывод данных, поэтому на вход элемента ИЛИ 50 будут поступать сигналы или с элемента 48, или 49, в зависимости от того, какой режим заказывает ЭВМ,

После прихода представления прямого доступа триггер 52 требования сбрасывается, а триггер 51 подтверж- Q дения выбора (ПВ) устанавливается в единичное состояние. Далее начинает работать счетчик 55 и сдвиговый регистр 56, в результате на выходе регистра 53 прямого доступа формируются сигналы синхронизации (СС) и вьшод а

(выв),.

Выходы сдвигового регистра 56 в исходном состоянии находятся в единичном состоянии, на первый информа5

ционный вход регистра подан ноль, на остальные - логическая единица. Как только триггер 51 подтверждения выбора встает в единицу и разрешит работу счетчика синхронизации и делителя частоты 55 (на вход которого поступает частота с тактового генератора импульсов 54), на выходе последнего появится частота, которая поступает на С-вход регистра 56.

По первому низкому перепаду частоты на выходах регистра 56 перепишутся входы, т.е. на первом выходе сдвигового регистра 56 появится низкий уровень, который, в свою очередь, поступает на единичный вход первого триггера регистра 53, который вырабатывает сигнал синхронизации вьщачи адреса, хранящегося в счетчике 20, в магистраль 43

По следующему перепаду частоты ноль на первом выходе сдвинется на второй выход, который поступает на единичный вход второго триггера регистра 53, при этом сформируется сигнал синхронизации обмена СС. Следующие перепад сдвинет ноль с второго выхода на третий, который поступает на единичный вход третьего триггера регистра 53 и на нулевой вход первого триггера.

Таким образом снимают сигнал синхронизации выдачи адреса и вырабатывают сигнал синхронизации выдачи данных, если происходит режим вьшода.

Следующий перепад сдвинет ноль на четвертьй выход, который поступает на единичные входы триггеров ввода и вьшода регистра 53, и в зависи- -мости от того, какой из режимов задай, сформируется сигнал либо Ввод либо Вьтод. С приходом сигнала Ответ (со) сбросится триггер 51 подтверждения выбора, а последний в свою очередь, поставит в исходное состояние регистр 53. Слово данных передается из регистра 13 данных в магистраль 43 и по приходу СО от ОЗУ сбрасывается триггер 51 подтверждения выбора. На этом цикл обмена между ЭВМ заканчивается.

Таким образом, передача данных из устройства в ЭВМ-приемник осуществляется без вмешательства процессора и программы, что значительно повышает быстродействие обмена. Функционирование устройства при передаче данных из магистрали 43 в магистраль

42в режиме прямого доступа аналогично описанному, только в этом случае

в обмене участвуют триггер 66, ввод прямого доступа (ВВПД), счетчик 21 адреса и регистр 14 данньЕх и формируется сигнал ввода (ВВ ).

При передаче данных из магистрали

43в магистраль 42 в режиме ППД за- дается режим Ввод триггером 66

регистра 11, который как раз и. определяет направление передачи в регистре 53, а требование ИДИ формируется уже на элементе И 49.- Элемент И 49 5 стробируется выходом 31 от триггера 71 для того, чтобы сформировать требование ПДП в случае готовности регистра 14 к приему данных.

Кроме этого, в устройство введены Q триггеры инкрементного (ИНК) 67 и декрементного (ДЕК) 68 обращения в режиме прямого доступа. Данные триггеры используются при передаче массива информации из одной магистрали в 5 другую. При этом происходит прибавление или вычитание в счетчиках 20 и 21 адреса. Аппаратное увеличение или уменьшение адреса в счетчике адреса позволяет значительно сократить вре- Q мя при передачах массивов информации из одной магистрали в другую, также не требует дополнительного цикла обмена на занесение нового адреса в счетчики 20 и 21 адреса.

Если установлен какой-то из признаков инкрементный или декрементный, триггера 67 или 68, то при каждом обращении к памяти в режиме ПДП на выходе элемента 59 или 60 будут фор- д мироваться два импульса, которые поступают на счетные входы счетчиков 20 или 21, при этом триггер 58 установки адреса не сбрасывается, т.е. следующий адрес обращения к памяти сформировался аппаратно. Это позволяет при передаче мас сива данных не заносить программно новьй адрес в счетчики, а работать только с данными, что повышает быстродействие.

Введение режима прямого доступа с инкрементным и декрементным обраще нием в устройство для сопряжения двух магистралей позволяет значительно .;: увеличить быстродействие многопроцесе сорных систем,

В режиме тестирования устройство работает следующим образом.

Если выставлен признак тестирования триггера 72 регистра 11 и задан

5

5

0

5

режим Вывод ПДП, начинает работать |узел обмена в обычном режиме Вывод, Но адрес и данные выдаваемые в магистраль 43, переписьюаются в счетчик 121 адреса и регистр 14 данных соот- |ветственно по обратной связи через |элемент 4 согласования по цепи 33, |а сигналы синхронизации записи адре- |са в счетчик и данных в регистр дан- ных формируются на элементах 61 и 62, далее они поступают на дешифратор 46 и по цепи 41 на управляющие входы счетчика и регистра адреса соответственно. Далее их можно сосчитать через магистраль 42 и сравнить с ранее заносимыми.

Ф О р м ула изобретения

1 Устройство для сопряжения двух вычислительных машин, содержащее четыре блока согласования, блок управления, четыре коммутатора, два регистра слова состояния, четыре региг стра адреса вектора прерывания, два регистра данных, причем группы информационных входов-выходов первого и второго блоков согласования образуют группы входов-выходов устройства для подключения к группам управ- л яющих входов-выходов первой и второй вычислительных машин соответственно, группы информационных входов- выходов третьего и четвертого- блоков согласования образуют группы входов- выходов устройства ДО1Я подключения |к группам информационных входов-выходов первой и второй вычислительных :Машин соответственно, при этом группы информационных выходов первого и второго блоков согласования соединены соответственно с первой и второй группами входов логического условия блока управления, первый и второй выходы которого соединены соответственно с управляющими входами первого и второго коммутаторов, первый и второй информационные входаг которых соединены соответственно с выходами первого, второго, третьего, четвертого регистра адреса вектора прерывания отличающееся тем, что, с целью повышения быстродейст- ВИЯ,.в него введены элемент ИЛИ, первый и второй входы которого соединены с выходами третьего и четвертого элементов И, выход триггера данных соединен с Третьим входом

g

10

20

10

третьего элемента И, четвертый вход которого соединен с четвертым входом четвертого элемента И и выходом триггера адреса, два коммутатора и два счетчика адреса, причем первая группа выходов блока управления соединена с управляющими входами третьего блока согласования, третьего и четвертого коммутаторов, с первыми установочными входами первого и второго регистров слова состояния, с входами записи первого регистра данных и первого счетчика адреса, вторая -группа выходов блока управления соединена с управляющими входами четвертого блока согласования, пятого и шестого коммутаторов, вторыми установочньми входами первого и второго регистров слова состояния, с входами записи второго регистра данных и второго s, счетчика адреса, информационные выходы первого, третьего и четвертого коммутаторов соединены с группой ин25 формационных входов третьего блока согласования, группа информационных выходов которого соединена с третьими установочными входами первого и второго регистров слова состояния, с третьей группой входов логического условия блока управления и информационными в ходами первого регистра данных и первого счетчика адреса, выходы первого регистра данных и первого счетчика соединены с первыми и вторыми информационными входами шестого коммутатора соответственно, информационный выход которого, а также информационные выходы второго

.„ и пятого коммутаторов соединены с группой информационных входов четвертого блока согласования, группа информационных выходов которого соединена с четвертыми установочными входами первого и второго регистров слова состояния, с четвертой группой входов логического условия блока управления и информационными входами второго регистра данных и второго счетчика адреса, выходы второго регистра данных и второго счетчика адреса соединены с первым и вторым информационными входами четвертого коммутатора соответственно, счетные входы первого и второго счетчиков адрег са соединены с третьим и четвертым выходами блока управления соответственно, пятая и шестая группа входов логического условия которого соедине30

35

45

50

55

ны с группами выходов первого и второго регистров слова сост ояния соответственно, третья группа выходов блока управления соединена с группой информационных входов первого блока согласования и пятыми установочными входами первого регистра слова состояния, первый и второй выходы которого соединены с первым и вторым входами логического условия блока управления соответственно, третий вход логического условия которого соединен с третьим выходом первого регистра слова состояния, с первым информационным входом третьего коммутатора и первым информационным входом пятого коммутатора, четвертая группа выходов блока управления соединена с группой информационных входов второго блока согласования и пятьм установочным входом второго регистра слова состояния, первый и второй выходы которого соединены с четвертым и пятым входами логического условия блока управления соответственно, шестой вход логического условия которого соединен с третьим выходом второго регистра слова состояния, с вторым информационным входом пятого i комйутатора и с вторым информационным входом третьего коммутатора, третий информационный вход которого соединен с четвертым выходом первого регистра слова состояния и третьим информационным входом пятого коммутатора, четвертый информациоиньй вход которого соединен с четвертым выходом второго рег;истра состояния и четвертым информационным входом третьего коммутатора.

2,Устройство по п.1, о т л и - чающееся тем, что блок управления содержит два узла обмена, два регистра прерывания, два дешифратора сигналов ответа, два дешифратора, причем первый, второй, третий, четвертый, пятьш, шесто.й и седьмой информационные входы первого и второго узлов обмена образуют соответственно пятую и шестую группу входов логичес кого условия блока, первьй, второй, третий, четвертый, пятый выходы первого и второго узлов обмена, первые выходы первого н второго регистров прерывания и выходы первого и второго дешифраторов сигналов ответа образуют соответственно третью и четвертую группу выходов блока, восьмой.

10

15

20

25

30

35

40

45

50

55

девятый информационные входы первого и второго узлов обмена, упр.авляю- щае входы первого и второго дешифраторов сигналов ответа, соединенные соответственно с первыми установочными входами первого и второго регистров прерывания, первые и вторые информационные входы первого и второго дешифраторов сигналов ответа, соединенные соответственно с первыми и вторыми информационными входами первого и второго дешифраторов адреса, третьи информационные входы-первого и второго дешифраторов адреса образуют соотп ветственно первую и вторую группы входов логического условия блока, груп-- пы выходов первого и второго дешифраторов адреса, соединенные соответственно с группами информационных входов первого и второго узлов обмена, образуют первую и вторую группы выходов блока, группы информационных входов первого и второго дешифраторов адреса образуют соответственно третью и четвертую группы входов логическо - го условия блока, вторые и третьи установочные входы первого и второго регистров обмена являются соответственно первым, вторым, четвертым, пятым входами логического условия блока, четвертьй установочный вход первого регистра прерьшания соединен с четвертым установочным входом второго регистра прерывания, с де.сятым информационным входом второго узла обмена и является третьим входом логического условия блока, пятый установочный вход первого регистра прерывания соединен с пятым установочным входом второго регистра прерывания, с десятым информационным входом пер- вого узла обмена и является шестым входом логического условия блока, вторые выходы первого и второго регистров прерывания являются первым и вторым выходами блока соответственно, шестой и седьмой выходы первого и второго узлов обмена образуют третий и четвертый выходы блока соответственно, при этом в блоке управления восьмые выходы первого и второго узлов обмена соединены с четвертыми информационными входами первого и второго дешифраторов адреса соответстг венно, выходы которых соединены с третьими информационными входами первого и второго дешифраторов сигналов отв.ат.а соответственно.

па, с разрешающим входом счетчика и является первым выходом узла, выход триггера требования прямого доступа к памяти является вторым выходом узла, первый выход регистра пятого доступа соединен с вторым входом второго элемента И и является третьим выходом узла, второй выход регистра пятого доступа является четвертым выходом узла, третий выход регистра прямого доступа соединен с вторым входом первого элемента И и является пятым выходом узла, выходы шестого и пятого элементов И являются соответственно шестым и седьмь м выходами узла, выходы первого и второго элементов И являются восьмым выходом узла, синхро- входы триггеров данных и адреса образуют группу информационных входов узла, при этом в узле обмена выход генератора импульсов соединен со счетным входом счетчика, выход которого соединен с разрешающим входом тригге- 5 ра подтверждения выбора и синхровхо- дом сдвигового регистра, выход которого соединен с информационным входом регистра прямого доступа и с третьими входами пятого и шестого элементов И, вход триггера требования прямого доступа к памяти соединен с выходом элемента.

0

0

22

35

1

351

6x5 П. Bxtf

Ik

Bx.W

вх.5

ЖВх.

Фиг.2

9мЛ

n

r-i

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Устройство для сопряжения двух магистралей | 1982 |

|

SU1111147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-23—Публикация

1986-07-18—Подача