Изобретение относится к области микроэлектроники, в частности к технологии изготовления изоляции элементов сверхбольших интегральных схем.

Известен способ изготовления боковой диэлектрической изоляции элементов интегральных схем типа "Изопланар", включающий вытравливание предварительно осажденного на подложку эпитаксиального слоя в местах изоляции на 60% толщины и термическое заращивание образованных в слое углублений двуокисью кремния с использованием для маскирования комбинаций диэлектрических пленок, например, над изолируемыми областями структуры.

Недостатками этого способа изготовления изоляции элементов интегральных схем являются

большая площадь, занимаемая окисной изоляцией (40-80% пощади кристалла), что уменьшает плотность компоновки элементов интегральных схем;

трудность получения воспроизводимых характеристик транзисторных структур с пристеночными р-n-переходами из-за эффекта "птичий клюв" в окисной изоляции, который влияет на пристеночный профиль базы, кроме того, при травлении эмиттерных окон в пленке двуокиси кремния наблюдается растравливание окисной изоляции как на изолированных областях, так и на границе раздела между изолируемой областью окисной изоляцией, что приводит к закорачиванию р-n-перехода между коллектором и эмиттером;

большая длительность формирования окисной изоляции (например для формирования двуокиси кремния толщиной 1,5-2,0 мкм при температуре 1000оС в парах воды необходимо 12-20 ч при нормальном давлении и 6-6 ч при давлении 1,5-2,0 атм).

Известен способ изготовления изоляции интегральных схем, включающий травление канавок в эпитаксиальном, скрытых слоях и частично в подложке, причем вытравленные канавки заполняют двуокисью кремния путем пиролиза моносилана, после чего двуокись стравливают до получения планарности с изолируемыми областями.

Известен также способ изготовления изоляции элементов интегральных схем, включающий формирование в эпитаксиальном слое канавок, окисление их стенок, заполнение канавок поликристаллическим кремнием, частичное удаление поликристаллического кремния до планарности с изолируемыми областями, а также частичное окисление поликристаллического кремния в канавках.

Вышеуказанным двум способам присущи следующие недостатки:

трудность получения воспроизводимых характеристик транзисторных структур с пристеночными р-n-переходами из-за растравливания двуокиси кремния на границе раздела изолируемой и изолирующей областей;

при окислении поликристаллического кремния в изолируемых областях возникают повышенные напряжения, приводящие к образованию дислокаций и дефектов упаковки, а значит к повышенным токам утечки транзисторных структур и снижению выхода годных интегральных схем.

Наиболее близким техническим решением к данному изобретению является способ изготовления изоляции интегральных схем, включающий формирование в кремниевой подложке сплошного скрытого слоя, наращивание эпитаксиального слоя, осаждение маскирующих пленок, формирование в них окон, вытравливание в эпитаксиальном, скрытом слоях и части подложки канавок, формирование в канавках диэлектрического покрытия, удаление его со дна канавок, противоканальное подлегирование дна канавок, осаждение слоя поликристаллического кремния, удаление его с изолируемых областей и канавок, окисление поликристаллического кремния в канавках.

К недостаткам данного способа относится недостаточная планарность поверхности структуры над канавками, возникающая из-за невертикальности их стенок и характеризуемая впадиной над канавками после снятия с изолируемых областей поликристаллического кремния и последующего окисления, причем глубина впадин достигает до 15% толщины канавок.

При формировании двухуровневой разводки на впадинах возникают обрывы пленок фоторезиста и металлической разводки, что снижает выход годных интегральных схем.

Целью изобретения является повышение выхода интегральных схем за счет улучшения планарности.

Поставленная цель достигается тем, что в способе изготовления изоляции интегральных схем, включающем формирование в кремниевой подложке сплошного скрытого слоя, наращивание эпитаксиального слоя, осаждение маскирующих пленок, формирование в них окон, вытравливание в эпитаксиальном, скрытом слоях и части подложки канавок, формирование в канавках диэлектрического покрытия, удаление его со дна канавок, противоканальное подлегирование дна канавок, осаждение слоя поликристаллического кремния, удаление его с изолируемых областей и канавок, окисление поликристаллического кремния в канавках, на маскирующих пленках дополнительно осаждают пленку фосфоро-или боросиликатного стекла, а после осаждения слоя поликристаллического кремния изготовленную структуру отжигают в инертной среде при температуре 950-1050оС в течение 20-40 мин с последующим удалением легированного фосфором или бором слоя поликристаллического кремния.

Достижение положительного эффекта в большой степени зависит от режимов отжига структуры после осаждения слоя поликристаллического кремния. При температуре отжига больше 1050оС и времени отжига больше 40 мин непланарность структуры увеличивается до 0,5-13 мкм, что недопустимо. Уменьшение температуры отжига менее 950оС приводит к увеличению времени обработки структуры при повышенной температуре, что ухудшает электрофизические характеристики. Уменьшение времени отжига менее 20 мин не гарантирует смыкание легированных областей поликристаллического кремния над канавками, что ухудшает планарность структур.

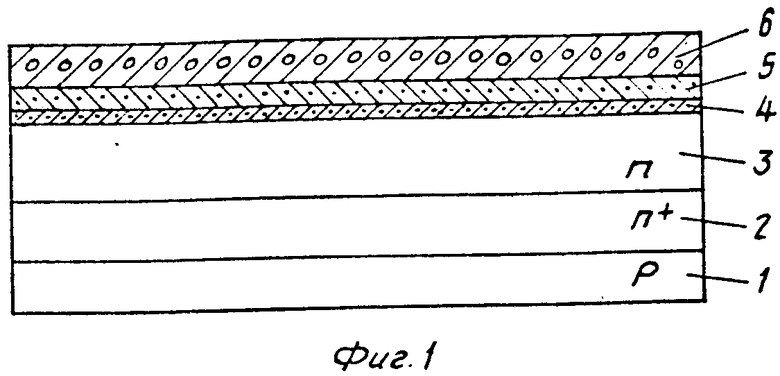

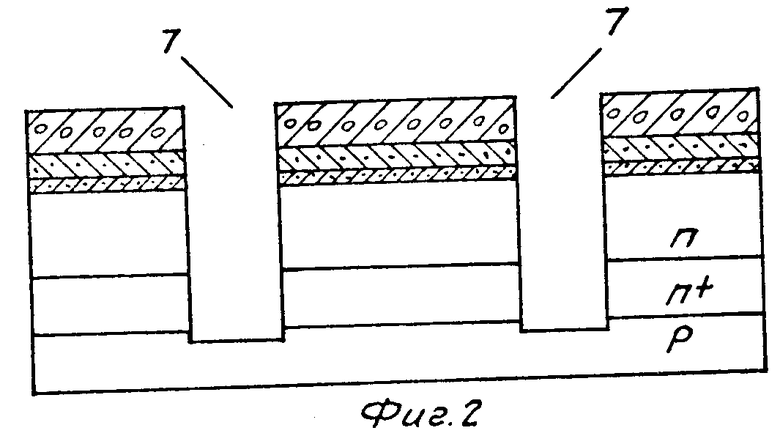

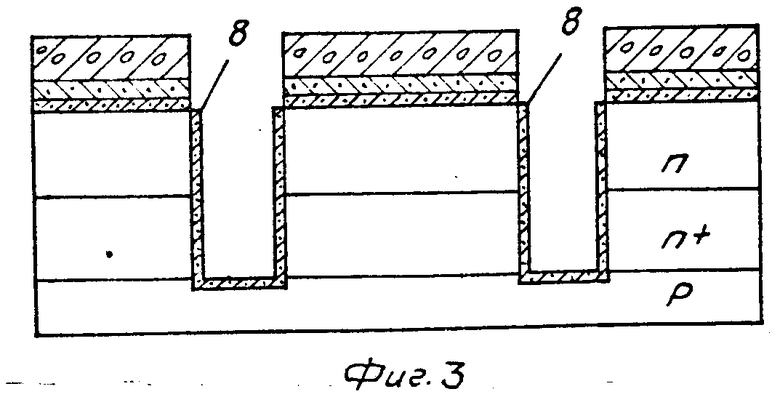

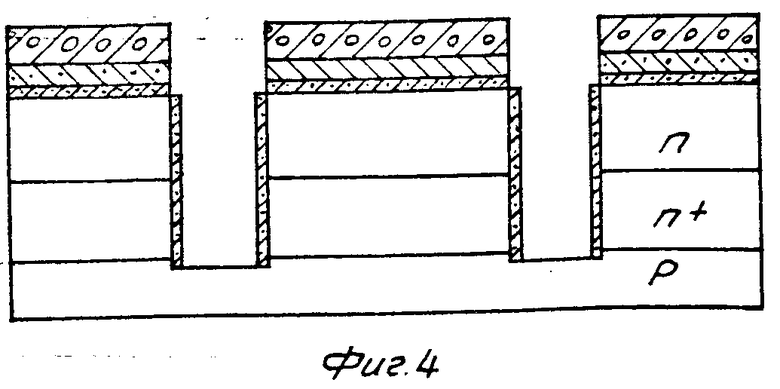

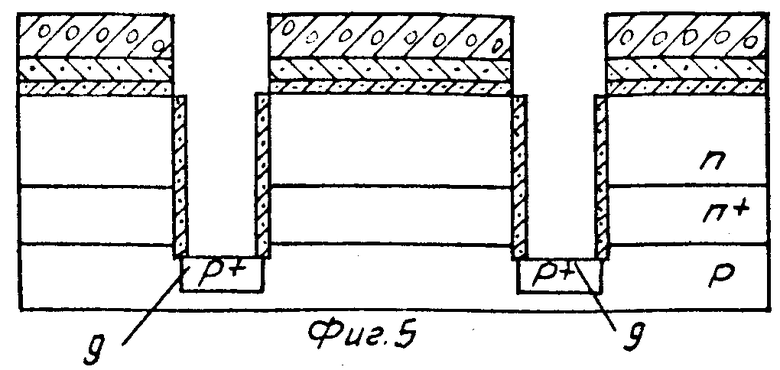

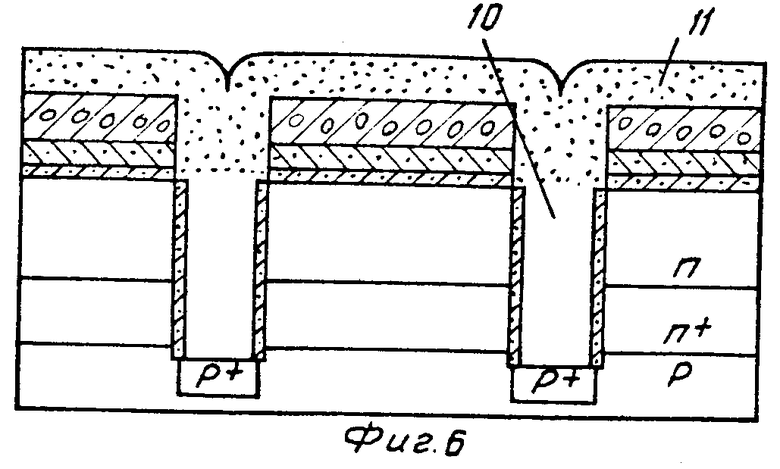

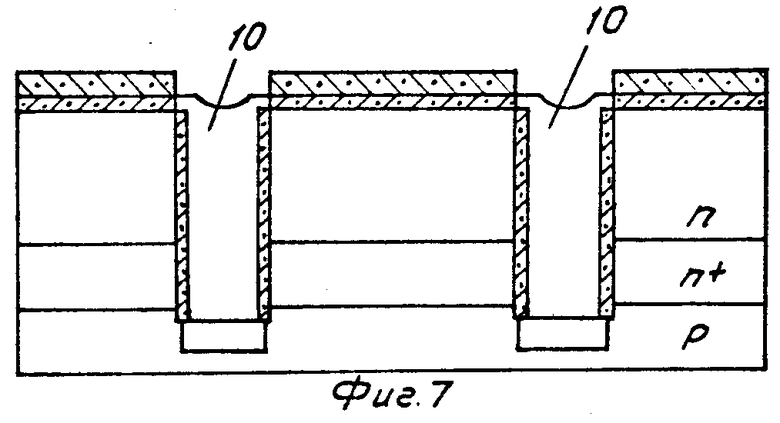

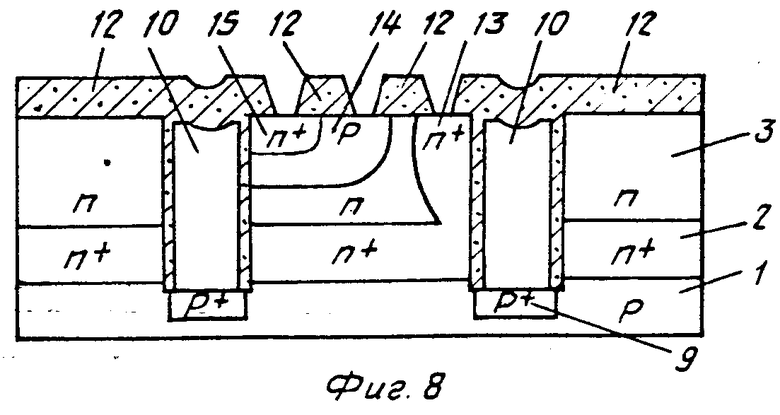

На фиг. 1 показана структура интегральной схемы в виде подложки со сформированными скрытым и эпитаксиальным слоями, а также с нанесенными пленками двуокиси кремния, нитрида кремния и легированного силикатного стекла; на фиг.2 структура после вытравливания канавок; на фиг.3 структура после формирования в канавках диэлектрического покрытия; на фиг.4 структура после удаления диэлектрического покрытия со дна канавок; на фиг.5 структура после противоканального подлегирования дна канавок; на фиг.6 структура после осаждения слоя поликристаллического кремния и отжига структуры; на фиг.7 структура после удаления слоя легированного поликристаллического кремния; на фиг.8 структура изготовленного транзистора интегральной схемы.

Структура содержит монокристаллическую кремниевую подложку р-типа проводимости 1, сплошной скрытый слой n+-типа проводимости 2, эпитаксиальный слой n-типа проводимости 3, пленку двуокиси кремния 4, пленку нитрида кремния 5, пленку легированного силикатного стекла 6, канавку 7, диэлектрическую пленку 8, область противоканального подлегирования 9, слой нелегированного поликристаллического кремния 10, слой легированного поликристаллического кремния 11, пленку двуокиси кремния 12, область коллектора 13, область базы 14, область эмиттера 15.

П р и м е р. На монокристаллической кремниевой подложке 1 р-типа проводимости с удельным сопротивлением 1-10 Ом·см формируют скрытый слой 2 с поверхностным сопротивлением 25-35 Ом/□ и глубиной 2-3 мкм, Наращивают эпитаксиальный слой кремния 3 n-типа проводимости с удельным сопротивлением 0,8-1,5 Ом см и толщиной 1,2-3 мкм. Термически окисляют эпитаксиальный слой с получением пленки двуокиси кремния толщиной 500-600  и осаждают пленку нитрида кремния 5 толщиной 1500-1800

и осаждают пленку нитрида кремния 5 толщиной 1500-1800  методом вакуумного пиролиза. Методом пиролиза в потоке газа-ноcителя оcаждают пленку фоcфороcиликатного стекла толщиной 0,5-1,0 мкм с содержанием фосфора 8-10 мас. (фиг.1) возможно также использование боросиликатного стекла с концентрацией бора 16-18 мас.

методом вакуумного пиролиза. Методом пиролиза в потоке газа-ноcителя оcаждают пленку фоcфороcиликатного стекла толщиной 0,5-1,0 мкм с содержанием фосфора 8-10 мас. (фиг.1) возможно также использование боросиликатного стекла с концентрацией бора 16-18 мас.

Методом фотолитографии в пленках двуокиси кремния, нитрида кремния и стекла с помощью плазмохимического травления вскрывают контурные окна, через которые также плазмохимическим методом вытравливают канавки 7 глубиной 4,2-7,0 мкм. Затем методом термического окисления на стенках и дне канавок формируют пленку двуокиси кремния 8 толщиной 500-600  .

.

Методом плазмохимического травления пленки двуокиси кремния удаляют со дна канавок и формируют противоканальные р+-области 9 имплантацией ионов бора с энергией 50 кэВ и дозой (3,0-3,2)х1014 см-2 (фиг.2-4).

На структуру осаждают слой поликристаллического кремния 10 при температуре 620оС и давлении 70-80 Па пиролизом моносилана. Толщина слоя 10 составляет 0,5-1,5 мкм и зависит от ширины канавок 7 (1,0-3,0 мкм). Затем структуру отжигают при температуре 1000оС в потоке аргона или азота с расходом 100-150 л/ч в течение 30-40 мин, при этом участки поликристаллического кремния, лежащие над пленкой фосфоросиликатного стекла и граничащие с ней, легируются фосфором до поверхностного сопротивления 20-50 Ом/□ а поликристаллический кремний, лежащий в канавках, не подвергается легированию (фиг.5). Легированный поликристаллический кремний удаляют в травителе состава HF:HNO3: H2O (1:9:10), который обеспечивает селективность травления по отношению к нелегированному поликристаллическому кремнию в отношении 5:1 при скорости травления легированного поликристаллического кремния 350-400  /c, а нелегированного 70-80

/c, а нелегированного 70-80  /c. После этой операции стравливают пленку фосфоросиликатного стекла в травителе состава Н:H2O (1:10) (фиг.6).

/c. После этой операции стравливают пленку фосфоросиликатного стекла в травителе состава Н:H2O (1:10) (фиг.6).

Термически окисляют поликристаллический кремний до сглаживания рельефа по всей поверхности структуры, после чего формируют коллекторную 13, базовую 14 и эмиттерную 15 области транзистора (фиг.7-8).

По сравнению с известными способами данный способ позволяет улучшить планарность поверхности структуры в области изоляции канавок до 0,1-0,25 мкм. После стравливания легированного слоя поликристаллического кремния селективно по отношению к нелегированному и после окисления поликристаллического кремния поверхность структуры имеет сглаженный рельеф, что упрощает процессы фотолитографии, металлической разводки, при этом повышается выход годных интегральных схем как при формировании структур транзисторов, так и при формировании двухуровневой разводки.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1986 |

|

SU1340500A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1982 |

|

SU1060066A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1983 |

|

SU1178269A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1983 |

|

SU1108966A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1984 |

|

SU1195862A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1981 |

|

SU1072666A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ, включающий формирование в кремниевой подложке сплошного скрытого слоя, наращивание эпитаксиального слоя, осаждение маскирующих пленок, формирование в них окон, вытравливание в эпитаксиальном, скрытом слоях и части подложки канавок, формирование в канавках диэлектрического покрытия, удаление его с дна канавок, противоканальное подлегирование дна канавок, осаждение слоя поликристаллического кремния, удаление его с изолируемых областей и канавок, окисление поликристаллического кремния в канавках, отличающийся тем, что, с целью повышения выхода годных интегральных схем за счет улучшения планарности, на маскирующих пленках дополнительно осаждают пленку фосфоро- или боросиликатного стекла, а после осаждения слоя поликристаллического кремния изготовленную структуру отжигают в инертной среде при температуре 950 - 1050oС в течение 20 - 40 мин с последующим удалением легированного фосфором или бором слоя поликристалличекого кремния.

СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ, включающий формирование в кремниевой подложке сплошного скрытого слоя, наращивание эпитаксиального слоя, осаждение маскирующих пленок, формирование в них окон, вытравливание в эпитаксиальном, скрытом слоях и части подложки канавок, формирование в канавках диэлектрического покрытия, удаление его с дна канавок, противоканальное подлегирование дна канавок, осаждение слоя поликристаллического кремния, удаление его с изолируемых областей и канавок, окисление поликристаллического кремния в канавках, отличающийся тем, что, с целью повышения выхода годных интегральных схем за счет улучшения планарности, на маскирующих пленках дополнительно осаждают пленку фосфоро- или боросиликатного стекла, а после осаждения слоя поликристаллического кремния изготовленную структуру отжигают в инертной среде при температуре 950 - 1050oС в течение 20 40 мин с последующим удалением легированного фосфором или бором слоя поликристалличекого кремния.

Авторы

Даты

1996-04-10—Публикация

1982-10-20—Подача