Изобретение относится к микроэлектронике, в частности к технологии изготовления высоковольтных мощных интегральных схем с диэлектрической изоляцией.

Известен способ изготовления высоковольтных мощных интегральных схем с диэлектрической изоляцией [1] , включающий формирование раздельных канавок на поверхности кремниевой монокристаллической пластины, создание на полученном рельефе сильнолегированного n-слоя, окисление рельефа, фотолитографию на полученном окисле в месте нахождения мощных высоковольтных транзисторов, эпитаксиальное наращивание на рельеф подложки, удаление монокристаллической пластины до вскрытия дна разделительных канавок, формирование в полученных структурах высоковольтных транзисторов и схем их управления.

Недостатком этого способа является то, что в кармане под высоковольтный транзистор формируется сильнолегированный n-слой толщиной от 7 до 20 мкм, что требует увеличения глубины травления канавок на такую же величину, что усложняет процесс травления и наращивания подложки за счет применения специальных режимов нанесения поликремния.

Наиболее близким техническим решением является способ изготовления высоковольтных мощных интегральных схем с диэлектрической изоляцией [2] , включающий формирование первого защитного покрытия на кремниевой монокристаллической пластине, первую фотолитографию по защитному покрытию под разделительные канавки, травление разделительных канавок, удаление защитного покрытия, формирование на полученном рельефе сильнолегированного n-слоя, окисление рельефа, вторую фотолитографию полученного окисла в местах нахождения мощных высоковольтных транзисторов, эпитаксиальное наращивание комбинированной монокристаллической кремниевой подложки, удаление монокристаллической пластины до появления дна разделительных канавок, формирование в полученной структуре мощных высоковольтных транзисторов в местах второй фотолитографии изолирующего окисла и схемы их управления.

Недостатком этого способа является то, что в кармане под высоковольтный транзистор формируется сильнолегированный n-cлой, что требует увеличения глубины травления канавок, увеличение глубины травления кремния снижает разрешающую способность, а следовательно, и плотность упаковки элементов схемы; увеличенная глубина канавок повышает бой структур, что снижает выход годных.

Целью изобретения является увеличение выхода годных за счет уменьшения глубины разделительных канавок.

Указанная цель достигается тем, что в данном способе перед нанесением защитного покрытия на кремниевой пластине проводят маскирование областей, соответствующих расположению мощных высоковольтных транзисторов, путем нанесения пленки нитрида кремния и фотолитографии по нитриду кремния, а затем на пластины наносят защитное покрытие на основе оксида кремния, проводят фотолитографию и травление разделительных канавок, удаляют оксид кремния, а перед эпитаксиальным наращиванием удаляют маскирующие участки нитрида кремния селективным травлением.

Новая последовательность операций позволяет исключить нанесение сильнолегированного n-слоя в месте нахождения высоковольтных мощных транзисторов, что позволяет уменьшить глубину травления канавок на 6-20 мкм. Уменьшенная глубина канавок повышает плотность упаковки элементов, что повышает выход годных.

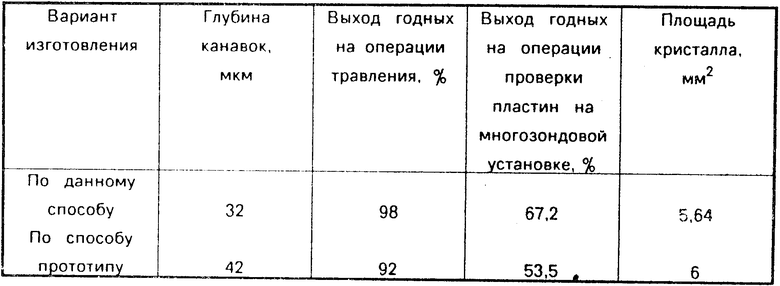

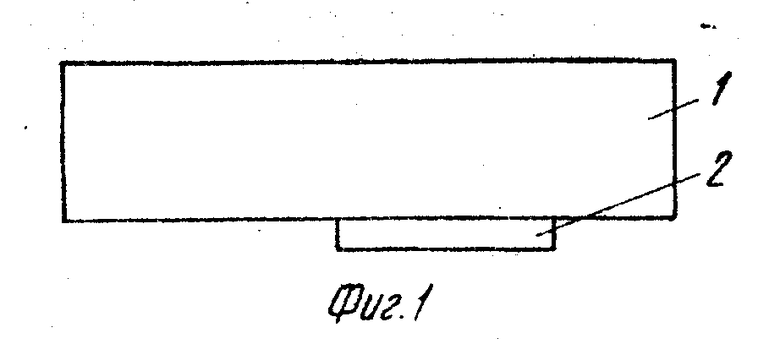

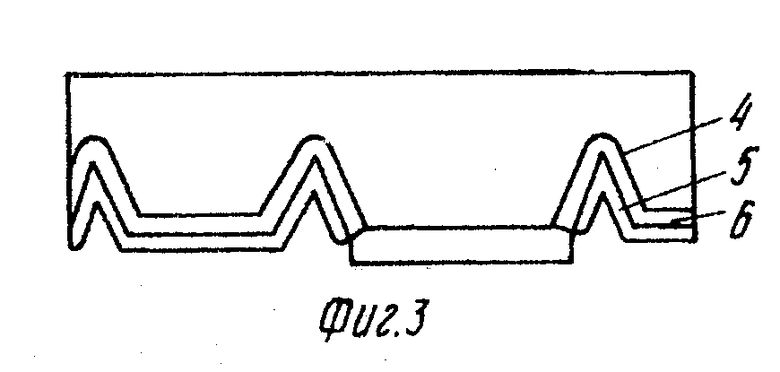

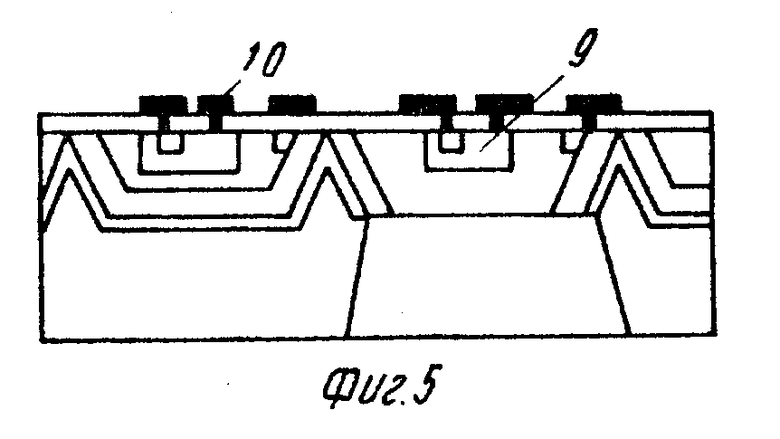

На фиг. 1 показана исходная монокристаллическая кремниевая подложка с нанесенной пленкой нитрида кремния; на фиг. 2 - структура после формирования защитного покрытия на основе двуокиси кремния; на фиг. 3 - структура после формирования рельефа и высоколегированного слоя n-типа, а также диэлектрической пленки на основе двуокиси кремния; на фиг. 4 - структура после эпитаксиального наращивания; на фиг. 5 - сформированная транзисторная структура с диэлектрической изоляцией.

Принятые обозначения: кремниевая монокристаллическая пластина 1, пленка 2 нитрида кремния, защитное покрытие 3 на основе пленки двуокиси кремния, разделительные канавки 4, диэлектрическая пленка 5 на основе двуокиси кремния, высоколегированный слой 6 n-типа проводимости, слой 7 поликристаллического кремния, слой 8 монокристаллического кремния монокристалл 9 подложки, монокристалл 10 подложки.

Данный способ был использован при изготовлении базового матричного кристалла высоковольтных источников питания.

П р и м е р. На пластину монокристаллического кремния (фиг. 1) n-типа проводимости методом разложения моносилана в атмосфере азота при температуре 850-900оС осаждают пленку нитрида кремния толщиной 0,18-0,2 мкм. С помощью метода фотолитографии эту пленку удаляют, оставляя лишь участки, соответствующие расположению мощных высоковольтных транзисторов.

Затем поверхность пластины окисляют при температуре 1150оС, последовательно подавая в зону окисления в течение 15 мин сухой кислород, 35 мин пары воды и 20 мин снова сухой кислород. При этом пленка двуокиси кремния толщиной 0,65±0,05 мкм растет в местах, не защищенных участками пленки нитрида кремния (фиг. 2).

В пленке двуокиси кремния методом фотолитографии вскрывают окна и вытравливают разделительные канавки глубиной 30±2 мкм для получения локальных выводов скрытого высоколегированного слоя (фиг. 3). Травление канавок производят в травителе, состоящем из трех частей 25% -ного водного раствора щелочи и одной части изопропилового спирта, при температуре 70-75оС, который не воздействует на пленку нитрида кремния.

После стравления пленки двуокиси кремния в буферном травителе, состоящем из плавиковой кислоты и воды (1: 5), в течение 10-12 мин, который практически не воздействует на нитрид кремния (за указанное время травления пленки двуокиси кремния нитрид кремния стравливается на 0,005-0,01 мкм), на немаскированных участках подложки введением фосфора или мышьяка формируют высоколегированные скрытые слои n-типа вдоль стенок канавок. Одновременно с формированием скрытых слоев получают пленку термической двуокиси кремния толщиной 0,65±0,05 мкм по режиму получения пленки. При этом пленка двуокиси кремния образуется на участках, незащищенных пленкой нитрида кремния.

Далее пленку нитрида кремния удаляют кипячением в концентрированной ортофосфорной кислоте в течение 50-60 мин, в которой пленка двуокиси кремния не травится, и наращивают эпитаксиально слой кремния. В местах, покрытых окислом, вырастает поликристалл, а в местах мощных транзисторов - монокристалл (фиг. 4). Далее механической обработкой формируют кремниевую структуру с диэлектрической изоляцией.

Следует отметить, что в процессе наращивания подложки ее легируют сурьмой до уровня 0,05-0,01 Ом˙см.

В сформированных областях с полной диэлектрической изоляцией формируют низковольтные транзисторные структуры, а в области монокристаллического кремния мощный высоковольтный проходной транзистор (фиг. 5).

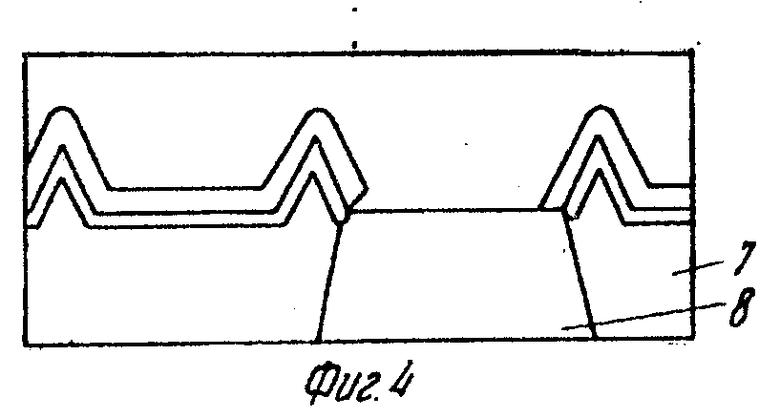

Сравнение данного способа с базовым объектом - прототипом показало, что глубина травления при рабочем напряжении мощного транзистора 100 В уменьшается на 10 мкм, что позволяет сэкономить 6% площади кристалла, а это дает экономический эффект за счет экономии затрат на травление кремния, заращивание канавок, а также экономию площади кристалла.

Сравнительные данные по выходу годных приведены в таблице. (56) 1. Патент США N 4286280, кл. H 01 L 27/04, 1981.

2. Sugawara I. Novol DI intelligent power IC technology using VICS. Int. Electron Devices Meet. Waschington, D. C. dec 6-9, 1987, New. Jork. n. I. 198 c, pp. 762-765.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1983 |

|

SU1108966A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1991 |

|

RU2024108C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1111634A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ СТРУКТУР | 1993 |

|

RU2102817C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1986 |

|

SU1340500A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1981 |

|

SU1116919A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1989 |

|

SU1702826A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1989 |

|

SU1702825A1 |

Использование: микроэлектроника, технология изготовления высоковольтных интегральных схем с диэлектрической изоляцией. Для увеличения выхода годных за счет уменьшения глубины разделительных канавок выполняется следующая последовательность технологических операций: максированные нитридом кремния на поверхности кремниевой монокристаллической пластины n-типа областей, соответствующих расположению многих высоковольтных транзисторов, нанесение защитного покрытия, фотолитография по защитному покрытию, вытравливание разделительных канавок, удаление защитного покрытия, формирование на полученном рельефе высоколегированного слоя n-типа проводимости, формирование диэлектрической пленки на основе оксида кремния, формирование на поверхности пластины областей монокристаллического кремния, соответствующих расположению мощных высоковольтных транзисторов, удаление селективным травлением участков нитрида кремния, эпитаксиальное наращивание кремниевой подложки с монокристаллическими и поликристаллическими участками, удаление монокристаллической кремниевой пластины до покрытия дна разделительных канавок, формирование в полученной структуре мощных высоковольтных транзисторов в областях с боковой диэлектрической изоляцией и низковольтных транзисторов в областях с полной диэлектрической изоляцией. 5 ил. , 1 табл.

СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ, включающий нанесение на кремниевую монокристаллическую пластину n-типа проводимости защитного покрытия, фотолитографию по защитному покрытию, вытравливание разделительных канавок, удаление защитного покрытия, формирование на полученном рельефе высоколегированного слоя n-типа проводимости, формирование диэлектрической пленки на основе оксида кремния, формирование на поверхности пластины областей монокристаллического кремния, соответствующих расположению мощных высоковольтных транзисторов, эпитаксиальное наращивание кремниевой подложки с монокристаллическими и поликристаллическими участками, удаление монокристаллической кремниевой пластины до вскрытия дна разделительных канавок, формирование в полученной структуре мощных высоковольтных транзисторов в областях с боковой диэлектрической изоляцией и низковольтных транзисторов в областях с полной диэлектрической изоляцией, отличающийся тем, что, с целью увеличения выхода годных за счет уменьшения глубины разделительных канавок, перед нанесением защитного покрытия на кремниевой пластине проводят маскирование областей, соответствующих расположению мощных высоковольтных транзисторов, путем нанесения пленки нитрида кремния и фотолитографии по нитриду кремния, а формирование на поверхности пластины областей монокристаллического кремния, соответствующих расположению мощных высоковольтных транзисторов, проводят селективным стравливанием нитрида кремния.

Авторы

Даты

1994-04-30—Публикация

1990-03-12—Подача