Изобретение относится к микроэлектронике, а именно к изготовлению интегральных схем высокой степени интеграции.

Целью изобретения является повышение плотности компоновки элементов интегральных схем за счет уменьшения межэлектродных расстояний и уменьшение числа фотолитографических операций за счет последовательного травления второго слоя поликристаллического кремния и диэлектрической пленки без применения фотолитографии.

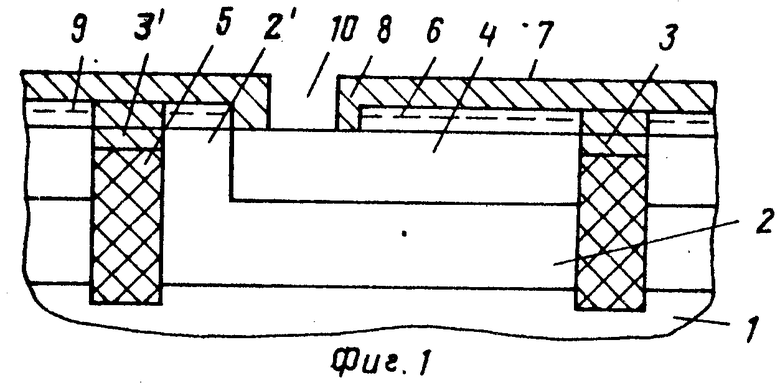

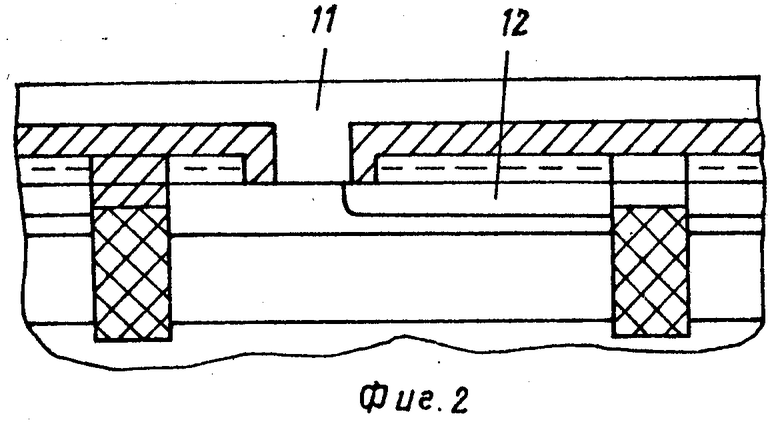

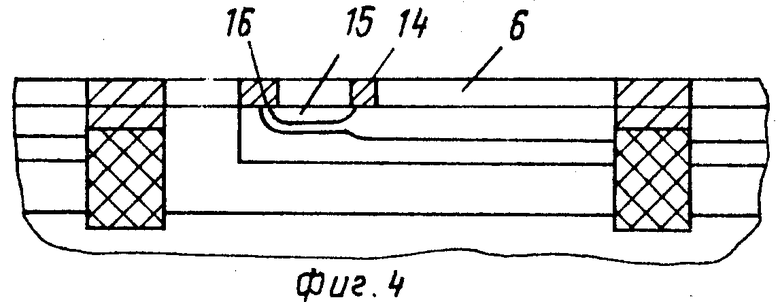

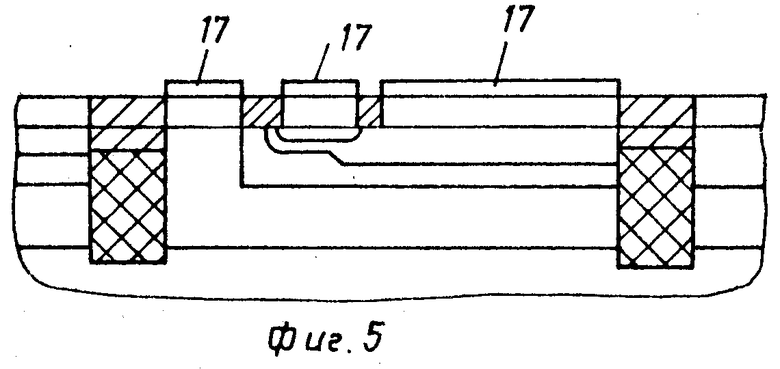

Сущность изобретения поясняется на фиг.1-5.

Перечень позиций: кремниевая подложка 1, скрытый легированный слой 2, 2, локальные участки окисла кремния 3, 3', эпитаксиальный слой кремния 4, область комбинированной изоляции 5, первый слой поликристаллического кремния 6, окисел кремния 7, изолирующие области 8 на вертикальных участках первого слоя поликристаллического кремния, легированная область р-типа 9 в первом слое поликристаллического кремния, окно 10 в пленке окисла кремния и первом слое поликристаллического кремния, второй слой поликристаллического кремния 11, область пассивной базы 12, окно для введения во второй слой поликристаллического кремния легирующих примесей 13, вертикальные изолирующие области 14, эмиттер 15, активная база 18, контакты на основе силицида платины 17.

П р и м е р. В кремниевой подложке р-типа проводимости (ρv удельное сопротивление подложки 0,1-10 Ом.см) формируют (например ионным легированием сурьмы с последующим термическим отжигом) сплошной скрытый n-слой с параметрами ρs (поверхностное сопротивление) 30-50 Ом/□ хj (глубина) 2-3,5 мкм. Наращивают эпитаксиальный слой n-типа проводимости с параметрами ρv (удельное сопротивление) 0,8-1,5 Ом.см, hэп (толщина эпитаксиального слоя) 0,8-1,2 мкм. Эпитаксиальный слой маскируют диэлектриком (SiO2-Si3N4) и с применением фоторезисторной маски плазмохимическим травлением травят эпитаксиальный слой, n+- скрытый слой и частично подложку. Производят окисление канавки (h 30-60 нм) и формируют пленку нитрида кремния при пониженном давлении толщиной 100-150 нм. Ионно-химическим травлением удаляют нитрид кремния с планарных поверхностей и канавку заполняют поликремнием, полученным при пониженном давлении. Далее плазмохимическим травлением удаляют поликристаллический кремний с меза-областей и под защитой диэлектрика SiO2-Si3N4, расположенного в меза-областях, удаляют дополнительно поликремний из канавки на глубину 300 нм и осуществляют окисление поликремния при Т 1123 К и Р 10 атм на толщину 250-300 нм. Осаждают первый слой поликремния толщиной 300 нм, маскируют его нитридом кремния толщиной 100-150 нм и под защитой фоторезистора в Si3N4 вскрывают окна в местах комбинированной изоляции и осуществляют селективное окисление первого слоя поликремния при Т 1123 К и Р 10 атм. Удаляют нитрид кремния, ионным легированием вводят бор с Е 60 кэВ и D 3,75.1013см-2 в первый слой поликремния и осаждают окисел кремния толщиной 500 нм. Под защитой фоторезиста плазмохимическим травлением удаляют окисел кремния и первый слой поликремния и осаждают окисел кремния из паров дихлорсилана и закиси азота при Т 1123 К при пониженном давлении, толщиной 500 нм. Далее ионно-реактивным травлением удаляют окисел кремния со дна вытравленного окна и осаждают второй слой поликремния толщиной 600-700 нм до получения ровной поверхности по всей площади структур. Плазмохимическим травлением травят второй слой поликремния до верхнего уровня первого слоя поликремния. Проводят ионное легирование бором с Е 60 кэВ и D 6,25·1013 cм-2 и мышьяком с Е 75 кэВ и D 9,4·1015 см-2 второго слоя поликремния, оставшегося в окне. Осуществляют термический отжиг в инертной среде при Т 1273 К в течение 30 мин. Получают следующие параметры транзисторной структуры: xjδн 300 нм, ρs= 650 Ом/□ (активная база); xjэ= 200 нм, ρsэ= 35-50 Ом/□, xjδн 350-400 нм, ρs= 80-90 Ом/□ (пассивная база). Далее плазмохимическим травлением удаляют окисел кремния до верхнего уровня второго слоя поликремния, осаждают покрытие из платины толщиной 50 нм, осуществляют формирование пленки силицида платины при Т 783 К и последующим удалением платины селективным травлением с окисных участков формируют самосовмещенный слой разводки на поликремниевых электродах. Толщина окисла кремния между поликремниевыми электродами эмиттер-база, эмиттер-коллектор составляет 500 нм и задается толщиной осаждаемого окисла кремния, которая может составлять 200-600 нм в вытравленном окне под активную базу и эмиттер.

30-60 нм) и формируют пленку нитрида кремния при пониженном давлении толщиной 100-150 нм. Ионно-химическим травлением удаляют нитрид кремния с планарных поверхностей и канавку заполняют поликремнием, полученным при пониженном давлении. Далее плазмохимическим травлением удаляют поликристаллический кремний с меза-областей и под защитой диэлектрика SiO2-Si3N4, расположенного в меза-областях, удаляют дополнительно поликремний из канавки на глубину 300 нм и осуществляют окисление поликремния при Т 1123 К и Р 10 атм на толщину 250-300 нм. Осаждают первый слой поликремния толщиной 300 нм, маскируют его нитридом кремния толщиной 100-150 нм и под защитой фоторезистора в Si3N4 вскрывают окна в местах комбинированной изоляции и осуществляют селективное окисление первого слоя поликремния при Т 1123 К и Р 10 атм. Удаляют нитрид кремния, ионным легированием вводят бор с Е 60 кэВ и D 3,75.1013см-2 в первый слой поликремния и осаждают окисел кремния толщиной 500 нм. Под защитой фоторезиста плазмохимическим травлением удаляют окисел кремния и первый слой поликремния и осаждают окисел кремния из паров дихлорсилана и закиси азота при Т 1123 К при пониженном давлении, толщиной 500 нм. Далее ионно-реактивным травлением удаляют окисел кремния со дна вытравленного окна и осаждают второй слой поликремния толщиной 600-700 нм до получения ровной поверхности по всей площади структур. Плазмохимическим травлением травят второй слой поликремния до верхнего уровня первого слоя поликремния. Проводят ионное легирование бором с Е 60 кэВ и D 6,25·1013 cм-2 и мышьяком с Е 75 кэВ и D 9,4·1015 см-2 второго слоя поликремния, оставшегося в окне. Осуществляют термический отжиг в инертной среде при Т 1273 К в течение 30 мин. Получают следующие параметры транзисторной структуры: xjδн 300 нм, ρs= 650 Ом/□ (активная база); xjэ= 200 нм, ρsэ= 35-50 Ом/□, xjδн 350-400 нм, ρs= 80-90 Ом/□ (пассивная база). Далее плазмохимическим травлением удаляют окисел кремния до верхнего уровня второго слоя поликремния, осаждают покрытие из платины толщиной 50 нм, осуществляют формирование пленки силицида платины при Т 783 К и последующим удалением платины селективным травлением с окисных участков формируют самосовмещенный слой разводки на поликремниевых электродах. Толщина окисла кремния между поликремниевыми электродами эмиттер-база, эмиттер-коллектор составляет 500 нм и задается толщиной осаждаемого окисла кремния, которая может составлять 200-600 нм в вытравленном окне под активную базу и эмиттер.

Таким образом, данное изобретение позволяет реализовать транзисторную структуру с повышенной степенью интеграции с использованием одного фотошаблона за счет безмасочного селективного травления второго слоя поликремния и окисла кремния, маскирующего горизонтальные поверхности первого слоя поликремния. По предлагаемому способу плотность компоновки элементов ИС (при ширине меза-области 400 нм) увеличивается по сравнению с прототипом в 1,6 раза. Так, по данному способу транзисторная структура занимает площадь 10·4 40 мкм, а по прототипу 17 x 4 68 мкм. По сравнению с прототипом (для получения транзисторной структуры используется 4 фотошаблона) данный способ уменьшает количество фотошаблонов на три. Следует отметить, что в прототипе существует перекрытие базовых электродов эмиттерными, что увеличивает емкость р-n-перехода эмиттер-база, в предлагаемом способе это перекрытие отсутствует.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1984 |

|

SU1195862A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1983 |

|

SU1178269A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1981 |

|

SU1072666A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1982 |

|

SU1060066A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1981 |

|

SU952051A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ P-N-ПЕРЕХОДАМИ | 1984 |

|

SU1215550A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНЫХ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1983 |

|

SU1135378A1 |

Изобретение относится к микроэлектронике, а именно к способам изготовления интегральных схем высокой степени интеграции. Целью изобретения является повышение плотности компоновки элементов интегральных схем за счет уменьшения межэлектродных расстояний и уменьшения числа фотолитографических операций за счет последовательного травления второго слоя поликристаллического кремния и диэлектрической пленки без применения фотолитографии. В способе изготовления интегральных транзисторов формируют в кремниевой подложке первого типа проводимости скрытый слой второго типа проводимости, наращивают эпитаксиальный слой второго типа проводимости и формируют комбинированную изоляцию. Затем охлаждают первый слой поликристаллического кремния, пленку нитрида кремния, прокисляют первый слой поликристаллического кремния и формируют пассивную базу, после чего формируют диэлектрическую пленку, окна под эмиттер, снова формируют диэлектрическую пленку и ионно-реактивным травлением удаляют ее с донных участков кремния, последующее осаждение второго слоя поликристаллического кремния производят до планарности всей рабочей поверхности полупроводниковой структуры, после чего травят второй слой поликристаллического кремния до выравнивания его поверхности с поверхностью первого слоя поликристаллического кремния в эмиттерном окне. Затем формируют области активной базы и эмиттера, стравливают диэлектрическую пленку с горизонтальной поверхности первого слоя поликристаллического кремния, формируют контакты. Данный способ позволяет реализовать транзисторную структуру с повышенной степенью интеграции с использованием одного фотошаблона за счет безмасочного селективного травления второго слоя поликристаллического кремния и окисла кремния. 5 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ, включающий формирование в кремниевой подложке первого типа проводимости скрытого слоя второго типа проводимости, формирование эпитаксиального слоя второго типа проводимости, формирование комбинированной изоляции, осаждение первого слоя поликристаллического кремния, формирование пленки нитрида кремния, локальное прокисление первого слоя поликристаллического кремния, формирование пассивной базы ионным легированием первого слоя поликристаллического кремния примесью, обеспечивающей перовый тип проводимости, формирование диэлектрической пленки, формирование окон под эмиттер травлением диэлектрика и первого слоя поликристаллического кремния до кремния с помощью маски из фоторезиста, формирование диэлектрической пленки, ионно-реактивное травление диэлектрической пленки с донных участков кремния, осаждение второго слоя поликристаллического кремния, формирование областей активной базы и эмиттера путем ионного легирования второго слоя поликристаллического кремния примесями, обеспечивающими первый и второй тип проводимости с последующей термообработкой, травление вторго слоя поликристаллического кремния и диэлектрической пленки для контактов, осаждение покрытия из платины, формирование пленки силицида платины, селективное травление платины, отличающийся тем, что, с целью повышения плотности компоновки элементов интегральных схем за счет уменьшения межэлектродных расстояний и уменьшения числа фотолитографических операций для изготовления интегральных транзисторов за счет последовательного травления второго слоя поликристаллического кремния и диэлектрической пленки без применения фотолитографии, осаждение второго слоя поликристаллического кремния производят, обеспечивая планарность всей рабочей поверхности полупроводниковой структуры, его травление осуществляют, выравнивая поверхность второго слоя поликристаллического кремния с поверхностью первого слоя, затем формируют области активной базы и эмиттера, после чего диэлектрическую пленку стравливают с горизонтальной поверхности первого слоя поликристаллического кремния.

| IEEE, Solid-State Circuits, v.SC-15, n 5, 1980, p.801-809 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНЫХ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1983 |

|

SU1135378A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1996-04-27—Публикация

1985-09-16—Подача