(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ УСЛОВНОГО МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Устройство для определения вероятностных характеристик фазы случайного процесса | 1985 |

|

SU1300510A2 |

| Устройство для измерения вероятностных характеристик фазы случайного сигнала | 1985 |

|

SU1320822A1 |

| Устройство для определения условного математического ожидания | 1981 |

|

SU1003097A1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ ПОСТЕПЕННЫХ ОТКАЗОВ ЭЛЕКТРОННЫХ ПРИБОРОВ | 1971 |

|

SU428361A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1981 |

|

SU945819A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ СРЕДНИХ ЗНАЧЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1969 |

|

SU243279A1 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| Устройство для оценки достоверности результатов измерений | 1981 |

|

SU970428A2 |

1

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано при создании приборов для измерения статистических характеристик фаз квазигармонических сигналов.

Известно устройство для измерения условного математического ожидания, содержащее последовательно соединенные аналого-цифровой преобразователь, схему совпадения, временной селектор, счетчик импульсов и делитель частоты, а также генератор импульсов опроса, триггер, узел сравнения и переключатели, причем один вход узла сравнения подключен к источнику случайного сигнала, стационарно связанного с исследуемым, второй вход - к источнику напряжения, относительно которого определяется условное математическое ожидание, а выход соединен с единичным входом триггера и через первый переключатель с входом временного селектора, нулевой вход триггера соединен с генератором импульсов опроса, а единичный выход триггера соединен через второй переключатель с управляющим входом схемы совпадения.

Наиболее близким по технической сущности к заявляемому является устройство, содержащее последовательно соединённые аналого-цифровой преобразователь, . временной селектор и счетчик импульсов в одном канале и последовательно соединенные схему сравнения, временной селектор, делитель частоты и триггер в другом, причем выход схемы сравнения соединен с управляющим входом аналого-цифрового преобразователя и через кнопочный переключа10тель с нулевым входом триггера, выход которого соединен с одними из входов двух временных селекторов 2.

Однако известное устройство не обеспечивает измерения условных вероятностных 15 характеристик случайной сигнала.

Целью изобретения является расщирение функциональных воз.можностей за счет определения условного математического ожидания случайной фазы сигнала в диапазоне частот.

20

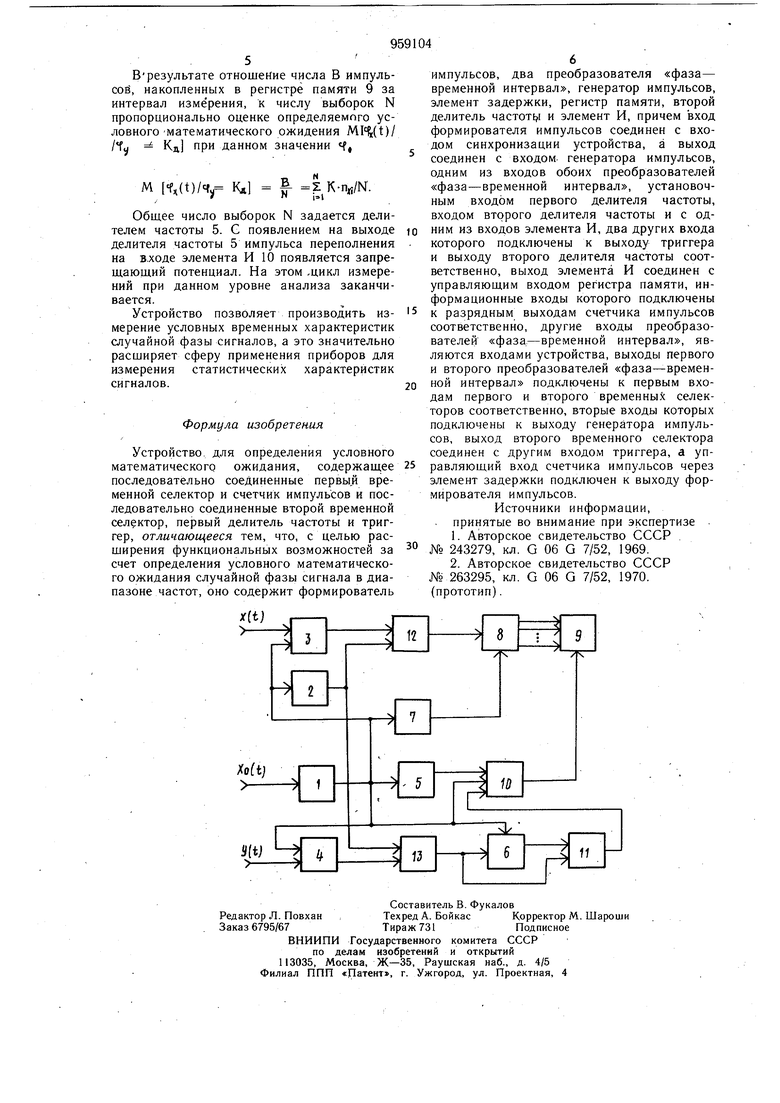

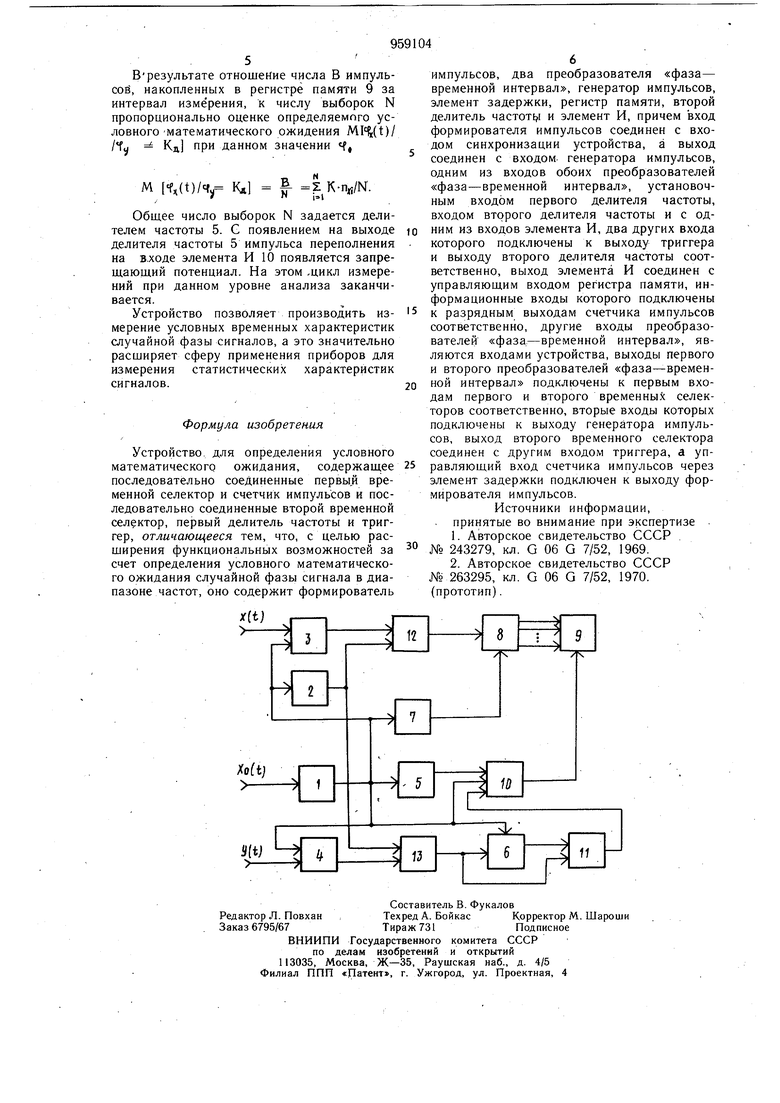

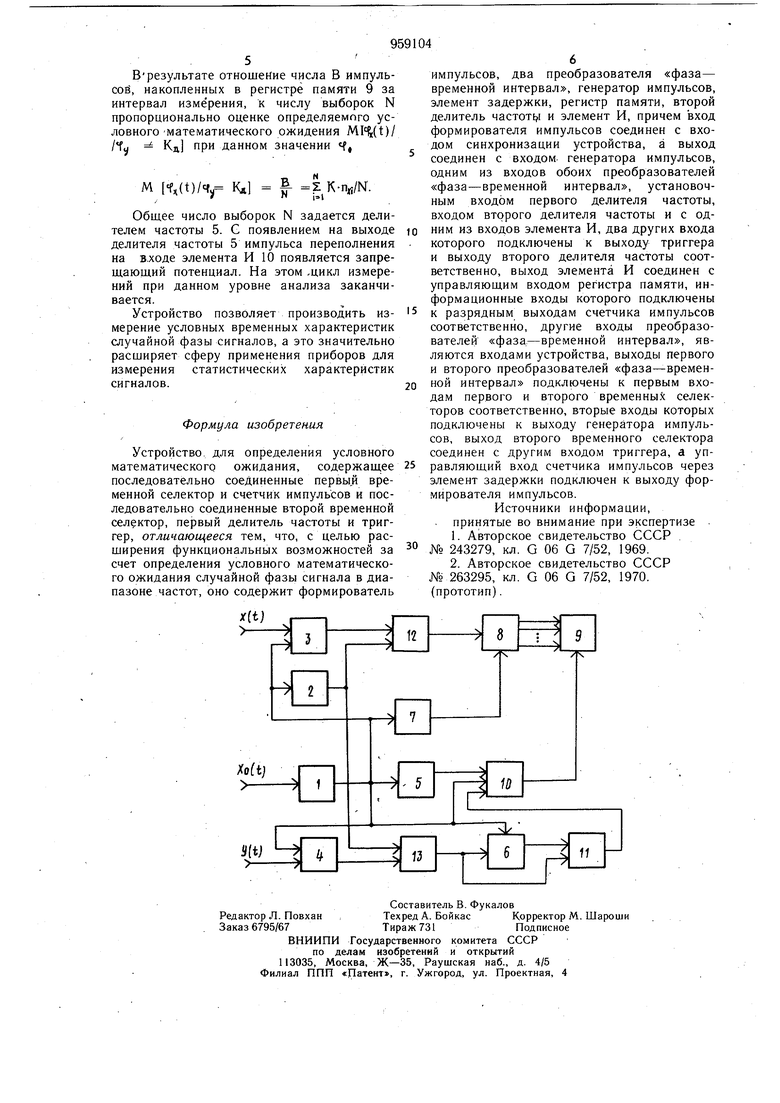

Поставленная цель достигается тем, чТо в устройство, содержащее последовательно соединенные первый временной селектор и счетчик импульсов и последовательно соединенные второй временной слектор, первый делитель частоты и триггер, введены формирователь импульсов, два преобразователя «фаза-временной интервал, генератор импульсов, элемент задержки, регистр памяти, второй делитель частоты и элемент И, причем вход формирователя импульсов соединен с входом синхронизации устройства, а выход соединен со входом генератора импульсов, одним из входов обоих эвателей «фаза-временной интерпреобразователейвал, установочным входом первого делителя частоты, входом второго делителя частоты и с одним из входов элемента И, два других входа которого подключены к выходу триггера и выходу второго делителя частоты соответственно, выход элемента И соединен с управляющим входом регистра памяти, информационные входы которого подключены к разрядным выходам счетчика импульсов соответственно, другие входы преобразователей «фаза-временной, интервал являются входами устройства выходы первого и второго преобразователей «фаза-временной интервал подключены к первым входам первого и второго временных селекторов соответственно, вторые входы которых подключены к выходу генератора импульсов, выход второго временного слектора соединен с другим входом триггера, а управляюш.ий вход счетчика импульсов через элемент задержки подключен к выходу формирователя импульсов. На чертеже представлена схема устройства. Устройство содержит формирователь 1 импульсов, на вход которого подается сигнал от источника опорного сигнала, генератор импульсов 2, преобразователи 3, 4 «фаза-временной интервал (ПФВИ), делители 5, 6 частоты, элемент 7 задержки, счетчик 8 импульсов, регистр памяти 9, управляющии вход которого подключен к выходу элемента И 10, триггер 11, селекторы 12, 13. Устройство работает следующим образом. Сигналы с исследуемыми стационарно св занными флуктуирующими фазами поступают соответственно на входы двух ПФВИ 3 и 4. Сигнал опорной частоты поступает на формирователь импульсов 1, который формирует короткие импульсы в момент, например, положительных переходов опорного сигнала через нулевое значение. Выходные сигналы ПФВИ 3 и 4 открывают временные селекторы 12 и 13 на время txi и Tyf. Интервалы времени t,,; и1и; заполняются квантующими импульсами, поступающими от генератора 2 импульсов. Количество импульсов в пачках п и п, , формируемых на выходах временных селекторов 12 и 13 в выбранном масштабе, определяет значение фазы в момент времени ti ,4y(ti) ч (ti) , где К - масштабный коэффициент. Здесь К -р- 36010 (F- частота опорного сигнала; f - частота следования импульсов с выхода умножителя частоты). Импульсы с выхода временного селектора 12 поступают на вход счетчика импульсов 8, на вход установки в нуль которого поступают импульсы с выхода форми , . „ -г -.-рователя 1 через элемент задержки 7(). Таким образом, счетчик 8 подсчитывает количество импульсов . Импульсы с выхода временного селектора 13 поступают на вход установки в нуль триггера 11 непосредственно, а на другой вход (вход установки в единицу) триггера 11 через делитель частоты 6. Коэффициент деления Кд делителя частоты 6 выбирается в соответствии с выбранным уровнем анализа, относительно которого определяется условное математическое ожидание. Если количество импульсов в пачке на выходе временного селектора 13 равно коэффициенту деления делителя 6 (Кп,,; Кд) то на выходе делителя частоты 6 появляется импульс, который поступает на вход триггера 11, на входе которого формируется разрешающий потенциал, и с приходом импульса с выхода формирователя 1 на выходе элемента И 10 (при наличии разрешающего потенциала на выходе делителя частоты 5) появляется импульс, разрешающий перезапись кода счетчика 8 в регистр памяти 9. Указанный импульс с выхода формирователя 1 устанавливает в исходное (нулевое) положение делитель частоты 6 и через время ад 4г счетчик импульсов 8. Время, за которое делитель частоты б устанавливается в исходное положение, должно быть достаточным для осуществления перезаписи числа Кпх|из счетчика 8 в регистр памяти 9. В исходное состояние триггер 11 возвращается первым импульсом генератора 2, проходящим через селектор 13 в следующем цикле работы. Если Кпу; Кд , то на выходе делителя частоты Б импульс не появляется, и импульс в выходе формирователя 1 возвращает делитель частоты 6 в исходное (нуле) состояние, а перезапись кода со счетчика 8 в регистр памяти 9 не происходит и счетчик 8 обнуляется, Если , то на выходе делителя частоты 6 появляется импульс, который приводит к тому, что на выходе триггера II появляется разрешающий потенциал для элемента И 10, однако импульс, порядковый номер которого равен К-Пц;- Кд+1, с выхода временного селектора 13 возвращает триггер 11 в исходное состояние еще до появления очередного импульса с выхода формирователя 1 и, таким образом, в данном случае перезаписи кода со счетчика 8 в регистр памяти 9 также не происходит.

Врезультате отношение числа В импульсой, накопленных в регистре памяти 9 за интервал измерения, к числу выборок N пропорционально оценке определяемого условного математического ожидения Ml(t)/ L Кд при данном значении Ч

м f,(t)/4jp К f z К-ПЙ/N.

Общее число выборок N задается делителем частоты 5. G появлением на выходе делителя частоты 5 импульса переполнения на влоде элемента И 10 появляется запрещающий потенциал. На этом ,цикл измерений при данном уровне анализа заканчивается.

Устройство позволяет производить измерение условных временных характеристик случайной фазы сигналов, а это значительно расширяет сферу применения приборов для измерения статистических характеристик сигналов.

Формула изобретения

Устройство, для определения условного математического ожидания, содержащ,ее последовательно соединенные первый временной селектор и счетчик импульсов и последовательно соединенные второй временной селектор, первый делитель частоты и триггер, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения условного математического ожидания случайной фазы сигнала в диапазоне частот, оно содержит формирователь

импульсов, два преобразователя «фазавременной интервал, генератор импульсов, элемент задержки, регистр памяти, второй делитель частоту и элемент И, причем вход формирователя импульсов соединен с входом синхронизации устройства, а выход соединен с входом генератора импульсов, одним из входов обоих преобразователей «фаза-временной интервал, установочным входом первого делителя частоты, входом второго делителя частоты и с одним из входов элемента И, два других входа которого подключены к выходу триггера и выходу второго делителя частоты соответственно, выход элемента И соединен с управляющим входом регистра памяти, информационные входы которого подключены к разрядным выходам счетчика импульсов соответственно, другие входы преобразователей «фаза-временной интервал, являются входами устройства, выходы первого и второго преобразователей «фаза-временной интервал подключены к первым входам первого и второго временный селекторов соответственно, вторые входы которых подключены к выходу генератора импульсов, выход второго временного селектора соединен с другим входом триггера, а управляющий вход счетчика импульсов через элемент задержки подключен к выходу формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-15—Публикация

1980-12-15—Подача