1

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано при создании приборов для измерения вероятностных характеристик.

Цель изобретения - повьшение быстродействия .

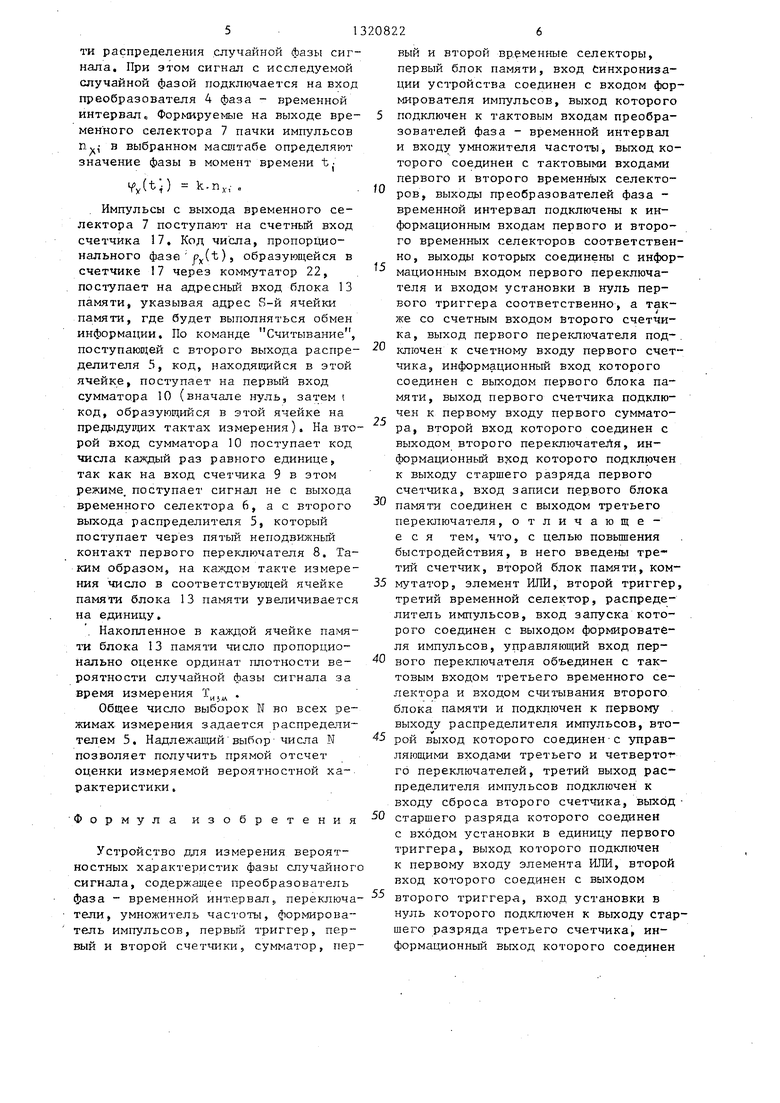

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит формирователь 1 импульсов, умножитель 2 частоты, преобразователи 3 и 4 фаза - временной интервал, распределитель 5 импульсов, временные селекторы 6 и 7, переключатель 8, счетчик 9, сумма- .тор 10j переключатель 11, блоки 12 и 13 памяти, переключатели 14 и 15, временной селектор 16, счетчик 17, триггер 18, элемент ИЛИ 19, триггер 20, счетчик 21, коммутатор- 22.

Общее число выборок N задается распределителем 3, С появлением на первом выходе распределителя 5 сигнала код, соответствующий оценке математического ожидания, из блока 13 памяти переписывается в блок 12 памяти. На этом цикл измерения математического ожидания заканчивается.

Значение среднеквадратичного отклонения измеряется в положении 2. переключателей. При этом импульсы, образующиеся на выходе временного се лектора 6, поступают в счетчик 9j в .который перед каждым измерением в до полнительном коде вводится значение оценки математического ожидания по команде управляющего сигнала Считывание из блока 12 памяти, поступающей с третьего выхода распределителя 5, При этом код разности, формируемый в счетчике 9 и пропорциональный значению приращения фазы Jif(t,) V(t;) - ) поступает на второй вход сумматора 10, где суммирует ся с кодом, поступающим на первый вход сумматора с выхода блока 13 памяти (аналогично указанному).

Суммирование выполняется без учета знака разности (контакт 2 второ го переключателя 11 разомкнут). По истечении N выборок в соответствующей ячейке памяти блока 13 памяти накапливается число А 2рК6(ч х) (к° эффициент определяется видом распределения вероятностей исследуемой фазы).

Если теперь на вход преобразовате ля 3 подать напряжение реализации

208222

второго случайного процесса и цикл измерений повторить, предварительно выставив время измерения (объем выборки) в распределителе 5, равным

5 N , то в соответствукяцей ячейке памяти блока 13 в конце цикла измерения получают непосредственно отнощение оценок среднеквадратичес- ких отклонений процессов, т.е. (ч 0 п6(,.

При измерении условного математц- ческого ожидания и функции регрессии переключатели ставятся в положение 4. К преобразователям 3 и 4 под ключаются сигналы с исследуемыми стационарно связанными флуктуирукщими фазами. Сигнал опорной частоты поступает на формирователь 1 импульсов. Выходные сигналы преобразователей 3 и 4 открывают временные селекторы 6 и 7 на время Г и Т,- , которые заполняются квантующими импульсами, поступающими с умножителя 2 частоты.

Количество импульсов в пачках п„. 25

и в выбранном масщтабе определяет значение фазы в момент времени .

cf(t. ) k-n. и (i.) k Hy,. .

Импул1 сы с выхода врет енного се- лектора 6 поступают на счетный вход счетчика 9, на вход начальной установки которого поступает с блока 12 памяти перед каждым тактом измерения код нуля (т.е. счетчик 9 сбрасывает- ся в нуль).

Импульсы с выхода временного селектора 7 поступают на счетньй вход счетчика 17. Код числа, пропорционального фазе Vy(tj)j образующийся в счетчике 17 через коммутатор 22, поступает на адресньй вход блока 13 памяти, указывая адрес V-й ячейки памяти, где будет выполняться обмен информации. По команде Считывание, поступающей с второго выхода распределителя 5, код, находящийся в этой ячейке, поступает на первый вход сумматора 10 (вначале нуль, а затем код, образующийся в этой ячейке памяти на преДь1ду1цих тактах измерения). На второй вход сумматора 10 поступает код числа, пропорциональный значеьшю фазы t/x ) ° счетчика 9, Код результата суммирования, полученный на выходе сумматора 10, записывается опять в V-тую-ячейку памяти блока 13 памяти по команде, поступающей на вход

45

55

31320822

Запись блока 13 памяти с третьего выхода распределителя 3.

Таким образом, по истечении И выборок в каждой ячейке блока 13 памяти накапливается число, пропорциональное оценке условного математического ожидания, т.е. ординате функции регрессии.

При измерении функции корреляции переключатели находятся в положении 3, Импульсы с выхода временного селектора 7 поступают на нулевой вход триггера 18 непосредственно, а на единичный вход триггера 18 - через счетчик 17. Коэффициент пересчета счетчика 17 выбирается в соответствии с выбранным уровнем анализа, оптимальное значение которого в смысле минимума продолжительности измерения.

JO

f5

рого равен п,; -и + выхода временного селектора 7 возвращает триггер 18 в исходное состояние еще до появления очередного импульса с второго выхода распределителя 5. Вре менной селектор 16 закрывается. Счетчик 17 перед каждым тактом измерения устанавливается в исходное состояние сигналом с третьего выхода распределителя 5,

Шаг измерения корреляционной функ ции определяется интервалом следования импульсов с второго выхода распределителя 5. Объем счетчика 21 опре деляется числом ординат корреляционной функции, подлежащих определению.

Код, сформированный в счетчике 21, равный аргументу корреляционной функции fif(, через коммутатор 22 (

например, для нормального распределе- ; равляющий вход коммутатора 22 в этом ния случайной фазы равно т( ч) tl, 4 liSCv). Если количество импульсов в пачке на выходе временного селектора 7 равно коэффициенту пересчета счетчика 17

(п . k), то на выходе счетчика 17 появляется сигнал, устанавливающий триггер 18 в положение, при котором на его выходе формируется разрешаю - щий потенциал, который через элемент ИЛИ 19 поступает на управляющий вход временного селектора 16,

На информационньй вход временного селектора 16 поступает импульс с второго выхода распределителя 5 в конце каждого такта измерения, которьш че- 35 на управляющем входе сумматора 10 с рез временной селектор 16 поступает подвижного контакта третьего пере- на счетный вход счетчика 21 и единич- ключателя 11. В дальнейшем устройстрежиме соединен с третьим выходом распределителя 5 через четвертьш переключатель 15) поступает на адресный вход блока 13 памяти.

Импульсы с выхода временного селектора 6 поступают на вход счетчика 9 , в котором перед каждым измерением устанавливается код, соответствующий оценке математического ожидания. Суммирование в сумматоре 10 в этом случае выполняется с учетом знака кода разности )f;(t; + Т ), поступающей с выхода счетчика 9 в соответствии .с подготовительным сигналом

ный вход триггера 20, Последний перебрасывается, создавая через элемент ИЛИ 19 разрешающий потенциал на входе временного селектора 16, Как только на выходе счетчика 21 появляется сигнал переполнения, триггер 20 перебра- сывает.ся в исходное нулевое состояние.

Селектор 16 закрывается до тех пор, пока на выходе триггера 18 не появляется разрешающий потенциал, соответствующий случаю Пу; k. Если n,,, то на выходе счетчика 17 сиг нал не появляется. Если k + 1, то на выходе счетчика 17 появляется сигнал, который приводит к тому, что на выходе триггера 18 появляется разрешающий потенциал, который через элемент ИЛИ 19 поступает ка управляющий вход временного селектора 16. Однако импульс, порядковый номер кото

рого равен п,; -и + выхода временного селектора 7 возвращает триггер 18 в исходное состояние еще до появления очередного импульса с второго выхода распределителя 5. Временной селектор 16 закрывается. Счетчик 17 перед каждым тактом измерения устанавливается в исходное состояние сигналом с третьего выхода распределителя 5,

Шаг измерения корреляционной функции определяется интервалом следования импульсов с второго выхода распределителя 5. Объем счетчика 21 определяется числом ординат корреляционной функции, подлежащих определению.

Код, сформированный в счетчике 21, равный аргументу корреляционной функции fif(, через коммутатор 22 (уп

равляющий вход коммутатора 22 в этом

равляющий вход коммутатора 22 в этом

на управляющем входе сумматора 10 с подвижного контакта третьего пере- ключателя 11. В дальнейшем устройстрежиме соединен с третьим выходом распределителя 5 через четвертьш переключатель 15) поступает на адресный вход блока 13 памяти.

Импульсы с выхода временного селектора 6 поступают на вход счетчика 9 , в котором перед каждым измерением устанавливается код, соответствующий оценке математического ожидания. Суммирование в сумматоре 10 в этом случае выполняется с учетом знака кода разности )f;(t; + Т ), поступающей с выхода счетчика 9 в соответствии .с подготовительным сигналом

45

во работает так же, как и при измерении функции регрессии, Накоплен- ное в каждой ячейке блока 13 памяти число за цикл измерения пропорционально оценке ординат функции корреляции .

Если на вход устройства в этом режиме измерения подключить два сигнала x(t) и y(t) со стационарно связанными флуктуирующими фазами, то за интервал измерения Т, получают в каждой ячейке блока 13 памяти оценку произведения нормированной функции корреляции (взаимной) на отношение среднеквадратических отклонений первого и второго процессов u(t) H i/(t)

6 ,, , . d-v

т--Ч/

50

55

,

(г) .

bu

В положении переключателей 5 получают оценку плотности вероятноети распределения случайной фазы сигнала. При этом сигнал с исследуемой случайной фазой подключается на вход преобразователя 4 фаза - временной интервал. Формируемые на выходе временного селектора 7 пачки импульсов

в выбранном масштабе определяют

значение фазы в момент времени t V(t;) k.n.,- „

Импульсы с выхода временного селектора 7 поступают на счетный вход счетчика 17. Код чи сла, пропорционального фaзe j7(t), образующейся в счетчике 17 через коммутатор 22, поступает на адресный вход блока 13 памяти, указывая адрес S-й ячейки памяти, где будет выполняться обмен информации. По команде Считывание, поступаюо ей с второго выхода распре делителя 5, код, находя гщйся в этой ячейке, поступает на первый вход сумматора 10 (вначале нуль, затем i код, образующийся в этой ячейке на предыдущих тактах измерения). На второй вход сумматора 10 поступает код числа каждый раз равного единице, так как на вход счетчика 9 в этом режиме, поступает сигнал не с выхода временного селектора 6, а с второго выхода распределителя 5, который поступает через пятый неподвижный контакт первого переключателя 8, Таким образом, на каждом такте измерения число в соответствующей ячейке памяти блока 13 памяти увеличивается на единицу.

Накопленное в каждой ячейке памяти блока 13 памяти число пропорционально оценке ординат плотности вероятности случайной фазы сигнала за время измерения Т .

Общее число выборок N во всех режимах измерения задается распредепи- телем 5. Надлежащий выбор числа N позволяет получить прямой отсчет оценки измеряемой вероятностной характеристики.

ормула изобретения

Устройство для измерения вероятостных характеристик фазы случайного игнала, содержащее преобразователь аза - временной инт.ервал, переключаели, умножитель частоты, формироваель импульсов, первый триггер, перый и второй счетчики, сумматор, пер-

о Ю

t5

20

25

30

35

40

45

50

55

вый и второй временные селекторы, первый блок памяти, вход Синхронизации устройства соединен с входом формирователя импульсов, выход которого подключен к тактовым входам преобразователей фаза - временной интервал и входу умножителя частоты, выход которого соединен с тактовыми входами первого и второго временных селекторов, выходы преобразователей фаза - временной интервал подключены к информационным входам первого и второго временных селекторов соответственно, выходы которьгх соединены с информационным входом первого переключателя и входом установки в нуль первого триггера соответственно, а также со счетным входом Второго счетчика, выход первого переключателя под-. ключен к счетному входу первого счет чика, информационный вход которого соединен с выходом первого блока памяти, выход первого счетчика подключен к первому входу первого сумматора, второй вход которого соединен с выходом второго переключателя, ин- формационньш БТСОД которого подключен к выходу старшего разряда первого счетчика, вход записи первого блока памяти соединен с выходом третьего переключателя, отличающееся тем, что, с целью повьшения быстродействия, в него введены третий счетчик, второй блок памяти, коммутатор, элемент ИЛИ, второй триггер, третий временной селектор, распределитель импульсов, вход запуска которого соединен с выходом формирователя импульсов, управляющий вход первого переключателя объединен с тактовым входом третьего временного селектора и входом считывания второго блока памяти и подключен к первому . выходу распределителя импульсов, второй выход которого соединен-с управляющими входами третьего и четвертот- го переключателей, третий выход распределителя импульсов подключен к входу сброса второго счетчика, выход старшего разряда которого соединен с входом установки в единицу первого триггера, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго триггера, вход установки в нуль которого подключен к выходу старшего разряда третьего счетчика, информационный выход которого соединен

7 13208228

с первым информационным входом комму-ционный вход которого соединен с вы- татора, второй информационный входходом сумматора, третий вход которо- которого подключен к информационномуго подключен к выходу второго блока выходу второго счетчика, выход эле-памяти и объединен с информационным мента ИЛИ соединен с информационным 5входом первого блока памяти, вход входом третьего временного селектора,считывания которого объединен с вхо- выход которого подключен к счетномудом записи второго блока памяти и входу третьего счетчика и входу ус-соединен с третьим выходом распреде- тановки в единицу второго триггера,лителя импульсов, информационные вхо- выход четвертого переключателя соеди- Оды первого и второго преобразователей нен с управляющим входом коммутатора,фаза -временной интервал являются вхо- выход которого подключен к адресномудами задания первого ивторого случай- входу второго блока памяти-, информа-ных процессов устройства соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения вероятностных характеристик фазы случайного процесса | 1985 |

|

SU1300510A2 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для вычисления параметров диаграмм разрежения индикаторов при исследовании сердечно-сосудистой системы | 1982 |

|

SU1157547A1 |

| Устройство для измерения корреляционногоОТНОшЕНия дВуХ СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU851420A2 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Многофункциональный цифровой коррелометр | 1979 |

|

SU826361A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТНЫХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU432512A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано при создании приборов для измерения вероятностных характеристик. Целью изобретения является повьшение быстродействия. Устройство содержит формирователь 1 импульсов, умножи- тель 2 частоты, преобразователи 3 и 4 фаза - временной интервал, распределитель 3 импульсов, временные селекторы 6 и 7, переключатель 8, счетчик 9, сумматор 10, переключатель 11, блоки 12 и 13 памяти, переключатель 14, переключатель 15, вре менной селектор 16, счетчик 17, триггер 18, элемент ИЛИ 19, триггер 20, счетчик 21, коммутатор 22. Устройство позволяет получить оценки условного и безусловного математических ожиданий, среднеквадратического от. клонения, функции регрессии, корреляционных функций и плотности распределения вероятностей. 1 ил. i (Л со ГчЭ О сх ND ГО

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1987-06-30—Публикация

1985-07-17—Подача