Изобретение относится к импульсной технике и может быть использовано при передаче и обработке информации.

Известно устройство декодирования троичного кода, содержащее блок фильт ров сигнальных признаков, блок синхронизации, блок взаимного запрета, два декомбинатора и блок элементов

или СП .

Недостаток данного устройства -невысокая надежность работы из-за; большого объема-оборудования.

Наиболее близким по технической сущности к изобретению является декодирующее устройство, содержащее блок фильтров, вход которого соединен с входной шиной, а выходы - с входами блока синхронизации и 1ерез блок запрета с входами счетчика контроля ошибок и первого преобразователя, выходы которого подключены к первым входам блока;элементов ИЛИ, выходы которого соединены с послёдовательными входами блока памяти, последовательные выходы которого подключены к вторым входам блока элементов ШШ и входам элемента И, параллельные выходы блока памяти соединены с входами декодера,- разрешающий вход которого подключен к выходу счетчика контроля ошибок, а выходы соединены с выходными шинами, первый, второй, и третий выходы блока синхронизации соединены соответственно с входами разрешения счетчика контроля ошибок и элемента И и с тактовым входом блока памяти t23 .

Недостатком известного устройства является невысокая надежность функционирования, обусловленная невозможностью коррекции искаженного сигнального признака кода и большим числом

оборудования.

I .

-Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в декодирующее устройство, содержащее блок фильтров, вход которого соединен с входной шиной, а выходы с выходами блока синхронизации и через блок запрета с входами счетчика контроля опшбок и-первого преобразователя, выходы которого подключены к первым входам блока элементов ИЛИ, выходы которого соединены с последовательЦ ными входами блока памяти, последовательные выходы которого подключены к вторым входам блока элементов ИЛИ

и входам элемента И, параллельныевыходы блока памяти соединены с входами декодера, разрешающий вход которого подключен к выходу счетчика контроля ошибок, а выходы соединены с выходными шинами, первый, второй и третИй выходы блока синхронизации соединены соответственно с входами блока разрешения счетчика контроля ошибок и элемента И и с тактовым входом блока памяти, введены соединенные последовательно блок сумматоров, элемент памяти, второй преобразователь и коммутатор, причем выходы первого преобразователя подключены к первым входам блока сумматоров,- вторые входы которого соединены с соответствующими выходами элемента памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, при этом выходы коммутатора подключены к третьим входам блока элементов ИЛИ, а разрешающий вход соединен с выходом элемента И.

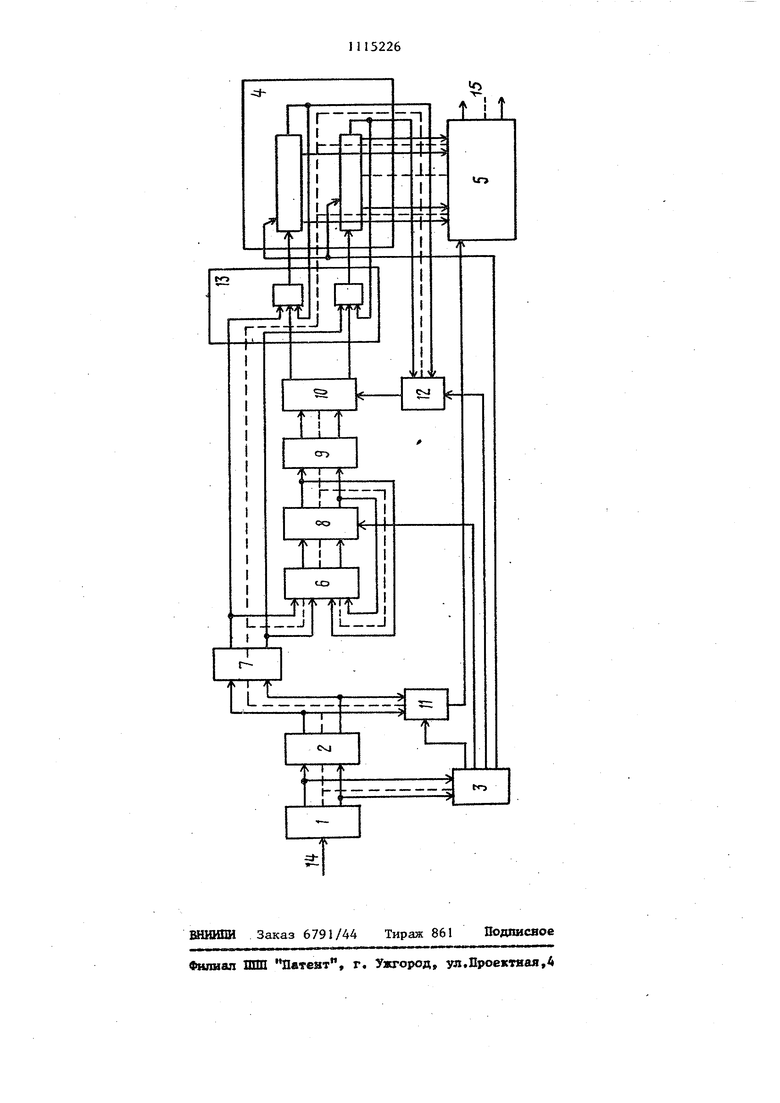

На чертеже представлена функциональная схема предлагаемого декодирующего устройства.

Устройство содержит блок 1 фильтров блок 2 запрета, блок 3 синхронизации, блок 4 памяти, декодер 5, блок 6 сумматоров, первый преобразователь 7, элемент 8 памяти, второй преобразователь 9, коммутатор 10, счетчик 11 контроля ошибок, элемент И 12, блок 13 элементов ИЛИ, входную (вход) 14 и выходные 15 шины (выходы).

Вход 14 устройства подключен к входу блока 1 фильтров, выходы которого подключены к входам блока 3 синхронизации и блока 2 запрета, выходы которого соединены с входами счетчика 11 контроля ошибок и первого преобразователя 7. Выходы первого преобразователя 7 подключены к первым входам блока 13 элементов ИЛИ, выходы которого соединены с последовательными входами блока 4 памяти, соответствующие последовательные выходы которого подключены к вторым входам блока 13 элементов ИЛИ и .входам элемента И 12. Параллельные выходы блока 4 памяти ;. подключены к информационным входам декодера 5,разрешающий вход которого соединен с выходом счетчика 11 контроля опшбок.

Первый, второй и третий выходы блока 3 синхронизации подключены соответственно к разрешающим входам счетчика 11 контроля ошибок элемента И 12 и к тактовому входу блока 4 памяти. Блок 6 сумматоров, элемент 8 памяти, второй преобразователь 9 и ком мутатор 10 соединены последовательно причем выходы первого преобразователя 7 подключены к первым входам блока 6 сумматоров, вторые входы которо го соединены с выходами элемента 8 памяти, управляющий вход которого подключен к четвертому выходу блока 3 синхронизации. Выходы коммутатора 10 подключены к третьим входам блока 13 элементов ИЛИ, а разрешаюпщй вход - к выходу элемента И 12. Блок 6 сумматоров представляет собой набор сумматоров, предназначенных для по следоват9Л1 ного суммирования по молулю К-1 чисел, которые соответствуют номерам сигнальных признаков кода. На элементе 8 памяти реа лизуется- последовательное суммирование по модулю К-1. Вычисление суммы производится числом, которое является дополнением к числу К-1. Для вычисления прямого числа исполвзуется второй преобразователь 9. . Устройство работает следукщим образом. На вход блока 1 фильтров сигнальных признаков поступает кодовая комбинация шины 14, подлежащая декодированию Элементы кодовой комбинации вьщеляются блоком 1 фильтров и поступают на входы блока 3 синхронизации и блока 2 запрета. С (К-1) - выходов блока 2 запрета импульсы первым преобразователем 7 преобразуются в двоичный код с номером принятого сигнального признака и через блок 13 элементов ИЛИ записываются в блок 4 памяти. В блоке 6 сумматоров производится последовательное вычисление суммы по модулю К-1 поступающих двоичных чисел. Промежуточный результат суммы записывает ся в элемент 8 памяти в моменты времени поступления импульсов с блока 3 синхронизации. С выхода элемента 8 памяти результат суммы по модулю К-I в дополнительном к (К-1)коде поступает на вход первого преобразователя 9, который вычисляет сумму по модулю (К-1) в прямом коде. При одиночной ошибке в коде полученное число является номером искаженного сигнального признака кода.Место ошибки в коде определяется элементом И 12, который формирует импульс на входе коммутатора 10. По данному сигналу коммутатор 10 осуществляет восстановление искаженного элемента,кода в блоке 4 памяти. В случае уничтожения двух или более сигнальных признаков кода сбрасывает счетчик 11 контроля ошибок и не разрешает производить общее декодирование декодером 5. После окончания приема кода блок 3 синхронизации по третьему выходу осу;- ществляет тактирование блока 4 памяти. Б случае одиночной ошибки в коде в блоке 4 памяти находится значение О сигнального признака,которое обнаруживается элементом И 12 на очередном тактовом импульсе блока 3 синхронизации. В этом случае импульс с выхода элемента И 12 поступает на управлянлций вход коммутатора 10, который производит коррекцию искаженного сигнального признака. После п тактов блока синхронизации 3 происходит восстановление информагши в блоке 4 памяти.Импульс с первого выхода блока 3 синхронизации, который поступает на вход счетчика 11 контроля ошибок, осуществляет декодирование принятой кодовой комбинации на декодере 5. Таким образом, введение блока сумматоров, элемента памяти, второго преобразователя и коммутатора позволяет произвести обнаружение и коррекцию одиночной ошибки в кодах с основанием больше двух, что повьш1ает надежность функционирования декодирующего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1978 |

|

SU785993A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| Устройство для ввода информации | 1984 |

|

SU1259240A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО,содержащее блок фильтров, вход которого соединен с входной шиной, а выходы с входами блока синхронизации и через блок запрета с входами счетчика конт роля ошибок и первого преобразователя, выходы которОго подключены к первым входам блока элементов ИЛИ, выходы которого соединены с последовательными входами блока памяти, последовательные выходы которого подключены к вторым входам блока элементов ИЛИ и входам элементов И, параллельные выходы блока памяти соединены с дами декодера, разрешающий вход которого подключен к выходу счетчика конт-. роля ошибок, а выходы соединены с выходными шинами, первый, второй и третий выходы блока синхронизации соединены соотвественно с входами разрешения счетчика контроля ошибок и элемента И и с тактовым входам блока памяти, отличающееся тем, что, с целью повышения надежности, в устройство введены соединенные последовательно блок сумматоров,элемент памяти, второй преобразователь и S коммутатор, причем выходы первого (/) С преобразователя подключены к первым входам блока сумматоров, вторые входы которого соединены с соответствующими выхода элемента памяти, управляющий вход которого подключен к четвертому выходу блока синхронизации, при этом выходы коммутатора подключены к третьим входам блока элементов ШШ, а разрешающий вход соединен с вьрсодом элемента И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Помехоустойчивость цифровых систем передачи телеметрической информации.Л.,Энергия, 1971, с.186-188 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1984-09-23—Публикация

1982-05-18—Подача