Изобретение относится к радиотехнике и может использоваться для передачи дискретной информации.

Цель изобретения - увеличение объема передаваемой информации.

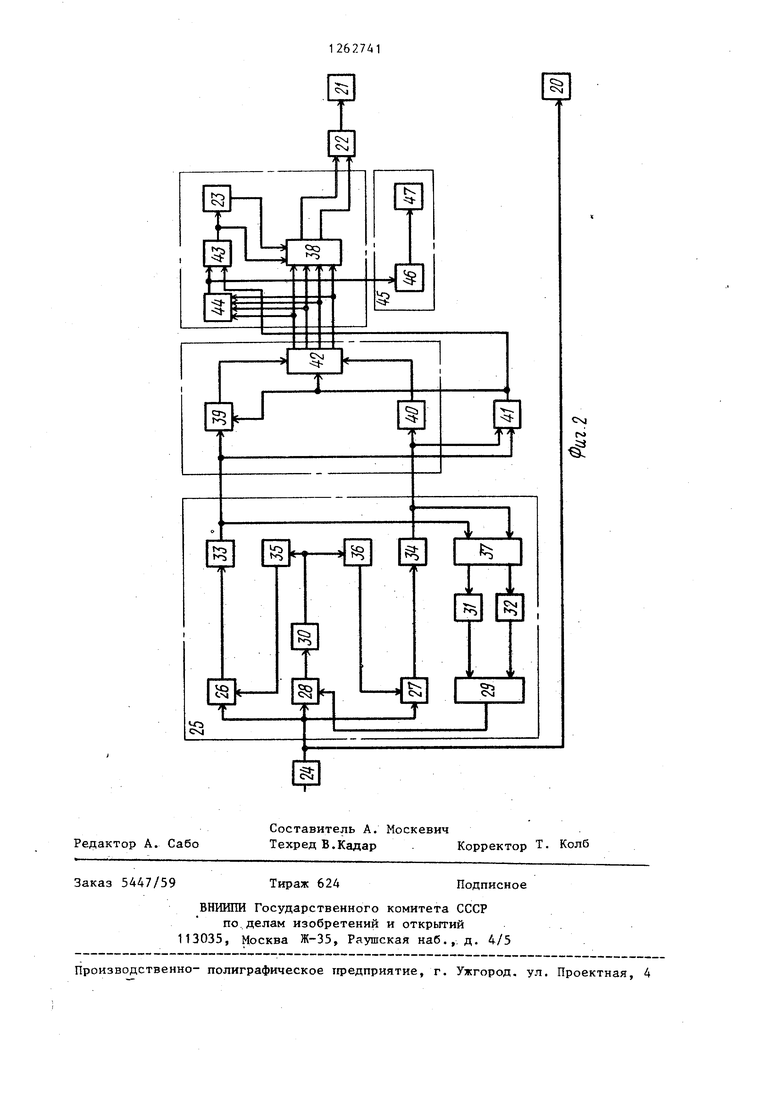

На фиг. 1 предстайлена структурная электрическая схема передающей стороны системы передачи дискретной информации; на фиг. 2 - структурная электрическая схема приемной стороны системы передачи дискретной информации.

Система передачи дискретной информации содержит на передающей стороне (фиг. 1) источник 1 сигналов служебной связи, источник 2 дискретной информации, блок 3 синхронизации первый счетчик 4, инвертор 5, формирователь 6 синхросигнала кодовых групп, формирователь 7 синхросигнала линейных посылок, блок 8 сдвига, последовательный регистр 9, параллельный регистр 10, блок 11 памяти, блок 12 запрета, преобразователь 13 основания кода, второй счетчик 14, частотньй модулятор 15, фильтр 16 верхних частот, блок 17 стробирования, первьш и второй сумматоры 18 и 19, а на приемной стороне содержит (фиг. 2) приемник 20 сигналов служебной связи, приемник 21 дискретной информации, формирователь 22 двоичного сигнала, блок 23 восстановления границ информационных посылок, усилитель 24 промежуточной частоты, корреляционньй приемник 25, состоящий из двух перемножйтелёй 26 и 27, управляемого фазовращателя 28, формирователя 29 сигнала ошибки, элемента задержки 30, двух интеграторов 31 и 32, двух фильтров 33 и 34 нижних частот, двух фазовращателей 35 и 36 и блока 37 селекции, преобразователь 38 основания сигнала, первьй и второй решающие блоки 39 и 40, блок 41 восстановления границ линейных посылок, декодер 42, блок 43 восстановления границ кодовых групп, блок 44 контроля, регистратор 45 ошибок, СОСТОЯЩИЙ из счетчика 46 и блока 47

индикации.

Система передачи дискретной информации работает слёдуюпрвд образом.

Преобразование двоичного основания в четвертичное осуществляется в соответствии со следующей таблицей.

В таблице рядом с каждой четвертичной кодовой группой указано значение цифровой суммы в данной группе, вычисленное как алгебраическая сумма амплитуд импульсов в кодовой группе при условии, что символам 0,1,2,3 кода поставлено в соответствие нормированное напряжение -3, -1, +1, +3.

Над каждой из трех колонок кодовых групп указано значение цифровой суммы на границе кодовых групп, хранящейся в блоке 11 памяти на передающей стороне (фиг. 1) к моменту поступления следующей двоичной группы, состоящей из трех символов, с выхода источника 2 дискретной информации, синхронизируемого блоком 3 синхронизации, и записываемой в последовательньш регистр 9 инверсной двоичной тактовой частотой с вьпсода инвертора 5. Три символа, записанные в последовательном регистре 9, переписываются инверсным кодовым синхросигналом с второго выхода формирователя 6 синхросигнала кодовых групп в параллельный регистр 10 и хранятся там в течение времени, равного трем двоичным тактовым интервалам. На вторую группу входов преобразователя 13 основания кода с выхода блока 11 памяти поступает значение предшествующей цифровой суммы на границе кодовых групп, представленное в двоичном виде, а на первьй вход - кодовый синхросигнал с первого выхода формирорзателя 6, который также подается через формирователь 7 и блок 8 на первый счетчик 4. Причем нуль в кодовом синхросигнале соответствует первому четвертичному С1тмволу на выходе преобразователя 13, а единица второму, и четыре его выхода соответ ствуют шинам четыре:: символов О, 1 , 2 и 3, Так,если ЦС -2 (соответствует сигналу 100 на выходе блока 11 памяти), то в соответствии с таблицей приходящая двоичная группа, например 011, кодируется группой из левой колонки таблицы в данном случае 32, которая на выходе первого сумматора 18 представляется двумя импульсами с амплитудами +3+1. Подсчитанная в первом счетчике 4 цифро вая сумма (для группы 32 цифровая сумма равна +4) складывается во втором счетчике -140 предыдущим значением (в нашем примере - 2 +4) и результата +2 (двоичное представле:ние 001) записывается в блок 11 па-, мяти (в случае разрешения с блока 12 запрета инверсным кодовым синхросигналом с второго выхода формирователя 6 синхросигнала кодовых групп). Следующая двоичная группа, например 001 должна кодироваться группой из правой колонки таблицы (в данном случае 02 с цифровой суммой в кодовой группе - 2) и т.д. Таким образом при пос туплении сигнала с преобразователя 1 на вькоде первого сумматора 18 получают четьфехуровневый балансный сигнал, прошедший через блок 17 стробирования, в энергетическом спектре которого отсутствуют постоянная составляющая, а мошность низкочастотных составляющих незначительна. Поэтому четьфехуровневый сигнал на выходе фильтра 16 верхних частот практически не искажается, а мощность помех в канале служебной связи на выходе:- , второго сумматора 19 пренебрежимо мала. Суммарный сигнал с выхода второго сумматора 19 по команде с источ ника 1 поступает на вход частотного модулятора 15 и далее в радиотракт. На приемной стороне (фиг. 2э) сиг нал с выхода усилителя 24 промежуточ.ной частоты поступает на управляемый фазовращатель 28 корреляционного приемника 25, создающий начальный сдвиг фаз между сигналами, приходяшдми на первый и второй перемножители 26 и 27. После перемножения и интегрирования в обоих фильтрах 33 и 34 нижних частот на их выходах формируются двоичные сигналы. Выходы фильтров 33 и 34 ни:кних частот подк.пючены к входам блока 37 селекции, который выделяет напряжения квадратурных составляющих,.находящихся в первом или третьем квадрантах сигнала фазоразностной модуляции (ФРМ). Выбор первого или третьего квадранта определяется тем, что в этих квадрантах знаки квадратурных составляющих одинаковы, что позволит однозначно определить величину и знак сигнала ошибки. Выходы блока 37 селекции соединены с входами интегратора 31 и 32, которые формируют напряжения, подаваемые на формирователь 29, пропорциональные средним значениям напряжений квадратурных составляющих при передаче сигнала ФРМ в первом или третьем квадрантах. Сигнал ошибки с выхода формирователя 29 подается на вход управляемого фазовращателя 28, который компенсирует сдвиг фаз, возникающий между поступающими на первый и второй перемножители 26 и 27 напряжениями и, тем самым, исключает уменьшение помехоустойчивости приема вследствие , действия нестабильности частоты несущей. Сигналы управления на перемножители 26 и 27 поступают через элемент 30 задержки и фазовращатели 35 и 36. С выходов фильтров 33 и 34 нижних частот сигналы поступают соответственно на первые входы решающих блоков, на вторые входы которых поступает тактовый синхросигнал, выделенный из сигналов с выходов фильтров 33 и 34 нижних частот в блоке 41 восстановления границ линейных посыпок. Двоичные последовательности с выходов первого и второго решающих блоков 39 и 40 преобразуются в декодере 42 в четьфе двоичных последовательности, соответствующие символам О, 1, 2 и 3 четвертичного основания, которые поступают на соответствующие входы преобразователя 38 основания кода и блока 44 контроля. С выхода блока 44 сигналы, пройдя блоки 43 и 23, поступают на другие входы преобразователя 38. На выходе преобразователя 38 формируются два цифровых потока, полученных в результате обратного пре- образования четвертичных символов в двоичные в соответствии с таблицей. Эти два цифровых потока, пройдя флр.мирователь 22, поступают в приемник 21. Нормальная работа преобразователя 38 основания сигнала обеспечивается двумя импульсными последователь ностями, следующими на границах кодовых групп и на границах информационных посылок. Первая из последовательностей создается в блоке 43 восстановления границ кодовых групп, а вторая - в блоке 23 восстановления границ информационных посылок. Причем сигналы служебной связи с выхода усилителя 24 поступают в приемник 20 сигналов служебной связи. Под нарушениями правил четвертичного кодирования в коде ЗВ20 (см. таблицу) понимаются превышения граничных значений цифровой суммы (ЦС +2 и ЦС -2), которые возникают при наличии ошибочных символов в принимаемом сигнале. При этом все единичные ошибки; в принимаемом сигнале приводят к превышению гранич|ных значений цифровой суммы. Для контроля и регистрации нарушений граничных значений служит регистратор 45. При этом подсчет превышений .граничных значений цифровой суммы в счетчике 46 и индикация в блоке 47 позволяет контролировать все ошибки возникающие в принимаемом сигнале, Формула изобретения 1. Система передачи дискретной информации, содержащая на передающей стороне первый сумматор, источник дискретной информации и блок син хронизации, выход которого подключен к входу формирователя синхросигнала кодовых групп, первый выход которог подключен к входу формирователя син хросигнала линейных посылок и к одн му входу преобразователя основания кода, а на приемной стороне - усили тель промежуточной частоты, регистр тор ошибок и блок восстановления границ линейных посьшок, выход кото рого подключен к управляющему входу первого решающего блока и первому входу блока восстановления границ код вых групп, выход которого соединен с входом блока восстановления границ информационных посылок и с одним входом преобразователя основания си нала, другой вход и выходы которого соединены соответственно с выходом блока восстановления границ информационных посылок и входами формирователя двоичного сигнала, выход которого подключен к входу приемника дискретной информации, отличающая с я тем, что, с целью увеличения объема передаваемой информации, в ней на передающей стороне введены блок стробирования, источник сигналов служебной связи, второр сумматор, фильтр верхних частот,блок сдвига, частотный модулятор, последовательный регистр, инвертор, два счетчика, блок памяти, параллельный регистр и блок запрета , выход которого подключен к одному входу блока памяти, другой вход и выходы которого соединены соответственно с вторым выходом формирователя синхросигнала кодовых групп и с другими входами преобразователя основания кода, выходы которого подключены к одним входам первого счетчика, выходы которого соединены с одними входами второго.счетчика, и к одним входам блока стробирования, выходы которого соединены с входами первого сумматора, выход которого через фильтр верхних частот подключен к первом входу второго сумматора,второй вход и выход которого соединены соответственно с выходом источника сигналов служебной связи и входом частотного модулятора,при этом,выход источника дискретной информации подключен к одному входу последовательного регистра, другой вход и выходы которого соединены . сответственно с выходом инвертора, К .входу которого подключен выход блока синхронизации, и с одними входами параллельного регистра, выходы которого подключены к соответствующим входам преобразователя основания кода, выходы блока памяти подключены к входам блока запрета и к другим входам второго счетчика, выходы которого соединены с соответствующими входами блока памяти, а соответствующие входы первого счетчика соединены с выходом блока сдвига и с вторым выходомi формирователя синхросигнала линейных посьшок, первый выход которого подключен к другому входу блока стробирования и к первому входу блока сдвига, второй вход которого соединен с первым выходом формирователя синхросигнала кодовых групп, второй выход которого

подключен к другому входу параллельного регистра, на приемной стороне введены блок контроля, корреляционный приемник, приемник сигналов служебной связи и последовательно соединенные второй решающий блок и декодер, выходы которого подключены к дополнительным входам преобразователя основания сигнала и к входам блока контроля, выход которого соединен с входом регистратора ошибок и с вторым входом блока восстановления границ кодовых групп, причем вькод усилителя промежуточной частоты подключен к входу приемника сигналов служебной связи и к входу корреляционного приемника, вьпсоды которого соединены с сигнальными входами первого и второго решающих блоков и с входами блока восстановления границ линейных посылок, выход которого подключен ко вто, рому входу декодера, третий вход , которого соединен с выходом первого решающего блока.

2. Система по п. 1, о т л и ч аю щ а я с я тем, что : корреляционньй приемник содержит два перемножителя, управляемый фазовращатель, два фильтра нижних частот, элемент задержки, два фазовращателя, два интегратора, формирователь сигнала ошибки и блок селекции, выходы которого через интеграторы подключены к входам формирователя сигнала ошибки, выход которого подключен к управляющему входу управляемого фазовращателя, сигнальный вход которого соединен с сигнальными входами первого и второго перемножителей, управляющие, входы которых соединены соответственно с выходами первого и второго фазовращателей, к входам которых подкл1- чены выход элемента задержки, вход которого соединен с выходом I управляемого фазовращателя, сигнальный вход которого является входом корреляционного приемника, выходами которого являются выходы первого и второго фильтров нижних частот, к входам которых J oдключeны соответственно выходы первого и второго перемножителей, выходы фильтров нижних частот соединены с входами блока селекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Кодер балансного кода 3B2Q | 1987 |

|

SU1531223A1 |

| Система передачи дискретной инфор-МАции | 1976 |

|

SU818026A1 |

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| Кодер двоичного кода 3В4В-3 | 1986 |

|

SU1444964A1 |

| Цифровая радиорелейная система передачи | 1987 |

|

SU1478357A1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1080252A2 |

Изобретение относится к радиотехнике. Увеличивается объем передаваемой информации. Система на передающей стороне содержит источник дискретной информации, блок синхронизации, формирователь (Ф) синхросигнала кодовых групп,Ф синхросигнала линейных посылок, 1-и сумматор, преобразователь основания кода. Вновь введены блок стробирования, источник сигналов служебной связи, 2-й сумматор, фильтр верхних частот, блок сдвига, частотный модулятор, последовательный регистр, инвертор, два счетчика, блок памяти, параллельный регистр и блок запрета. На приемной стороне система содержит приемник (П) дискретной информации, Ф двоичного сигнала, блок восстановле-, ния границ информационных посылок, ЗТ1Ч, преобразователь основания сигнала, 1-й решающий блок, блок восстановления границ линейных посыпок, блок восстановления границ кодовых групп, регистратор ошибок, состоящий из счетчика и блока индикации. Вновь введены блок контроля, корреляционный П, состоящий из двух перемножителей, управляемого фазовращателя, Ф сигнала ошибки, элемента задержки, с € двух интеграторов, двух фильтров (Л нижних частот, двух фазовращателей и блока селекции,П сигналов служебной связи, и последовательно соединенные 2-й решающий 6noKji декодер. Преобразование двоичного основания в четвертичное осуществляется в соответствии с таблицей, приведенной в описании изобретения, 1 з.п. ф-лы. 2 ил., 1 табл.

| Система передачи дискретной инфор-МАции | 1976 |

|

SU818026A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-01—Подача