(54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1982 |

|

SU1115226A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Система телемеханики | 1984 |

|

SU1257686A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СИСТЕМА ОПОЗНАВАНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ | 2003 |

|

RU2254596C2 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

I

Изобретение относится к радиотехнике и может быть использовано в устройствах передачи и обработки информации.

Известно декодирующее устройство, содержащее блок фильтров, выходы которого подключены ко входам блока запрета и блока синхронизации, а также блок.элементов ИЛИ и последовательно соединенные блок памяти и декодер l .

Однако известное устройство имеет низкую помехоустойчивость и небольшую скорость передачи информации.

11ель изобретения - повышение помехоустойчивости и скорости передачи информации.

Для этого в декодирующее устройство, содержащее блок фильтров, выходы которого подключень ко входам блока запрета и блока синхронизации, а также блок элементов ЛИ и последовательно соединенные блок памяти и декодер, введены счегчик контроля ошибок, первый преобразователь, послеаовяте.тъно соединенные второй преобра., блок группирования сигналов, анализатор и кодер, а также два элемента И и последовательно соединенные генератор сигнала опроса и элемент ИЛИ, выход которого подключен к тактовому входу блока памяти, при этом выходы блока запрета подключены ко входам счетчика контроля ошибок, первого ij второго преобразователей, причем выходы первого преобразова геля подключены к первым входак) блока элементов ИЛИ,

10 а выходы кодера через итопые входы блока элементов ИЛИ подключены ко входам блока памяти, соответствующие выходы которого подключены к третьим входам блока элементов ИЛИ и входам первого

15 элемента И, выход которого Г100ключен к управляющему входу кодера, в,ход счетчика контроля ошибок подключен к первому входу второго элемент И, выход которого подключен к разре1и4кгиему входу

20 декодера, а первый, пто|.Г)й и третий выходы блока синхронизпции подключены соответственно к вторым входам второго элемента И и элемента ИЛИ и к объедиценным входам первого элемента И и генератора сягнала опроса.

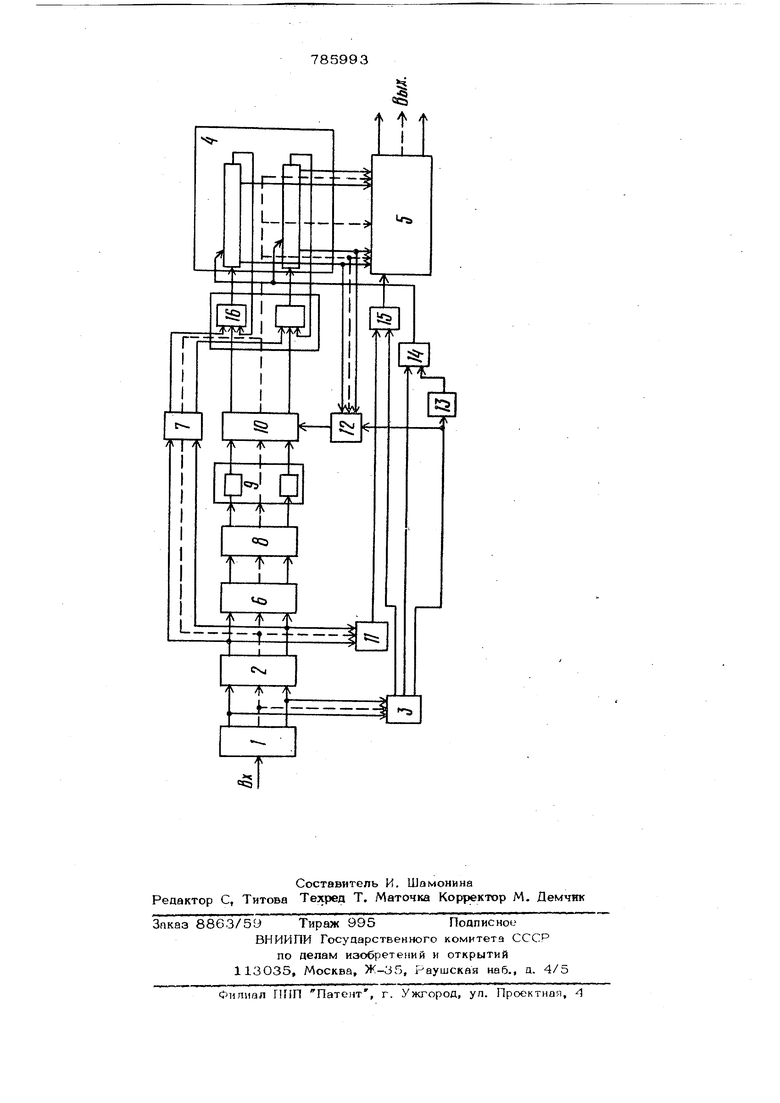

На чертеже изображена структурная электрическая схема предложенного устройстве.

Предложенное устройство содержит бло 1 фильтров, блок 2 запрета, блок 3 синхронизации, блок 4 памяти, декодер 5, преобразователи 6 и 7, блок 8 группирования сигналов, анализатор 9, кодер 1О, счетчик 11 контроля ошибок, первый элемент И 12, генератор 13 сигнала опроса, элемент ИЛИ 14, второй элемент И 15, блок 16 элементов ИЛИ.

Предложенное, устройство работает еледугошим образом.

На вход 1 поступает кодовая комбинация, подлежащая декодированию. Элементы кодовой комбинации выделяются блоком 1 и поступают на вход блоков 2 и 3. С (К-1) выходов блока 2 импульсы преобразователем 7 преобразуются в двоичный код с номером принятого сигнального признака и через блок 16 записываются в блок 4. В преобразователе 6 каждый импульс сигнального признака, за исключением К-го, преобразуется в числоимпульсный код с номером сигнального признака. Импульс К-го сигнального признака по До полнительным () выходам преобразователя 6 преобразуется одновременно в числоимпульсный код с числом импульсов, пропорциональным номеру выхода. Импульсы на 2 (К-1) выходах преобразователя 6 с помощью блока 8 объединяются и поступают на (К-1) входы анализатора 9, который осуществляет проверку по модулю (K-l) на всех (K-l) входах. Результат проверок кодируется кодером 10 в двоичный код обнаруженного искаженного одиночного сигнального признака. В зависимости от кода по сигналу с первого элемента И 12 осуществляется восстановление искаженного элемента в блоке 4. В случае уничтожения двух или более сигнальных признаков кода срабатывает счетчик 11 и не разрешает прохождение импульса с блока 3 на разрешающий вход декодера 5. После окончания приема кода блок; 3 запускает генератор,13, который через элемент ИЛИ 14 осуществляет тактирование блока 4. В случае одиночной ошибки в коде в блоке 4 находится значение О сигнального признака, которое будет обнаружено первым элементов И 12 на очередном тактовом импульсе генератора 13. В этом случае импульс с выхода первого элемента И 12 поступает на управляющий вход кодера 10, который Производит коррекцию искаженного сигнального признака. После и тактов генератора 13 в блоке 4 происходит восстановление информации, после чего блок 3 формирует на первом выходе импульс, который через второй элемент И 15 поступает на разрешающий вход декодера 5. По этому сигналу осуществляется декодирование при нятой комбинации.

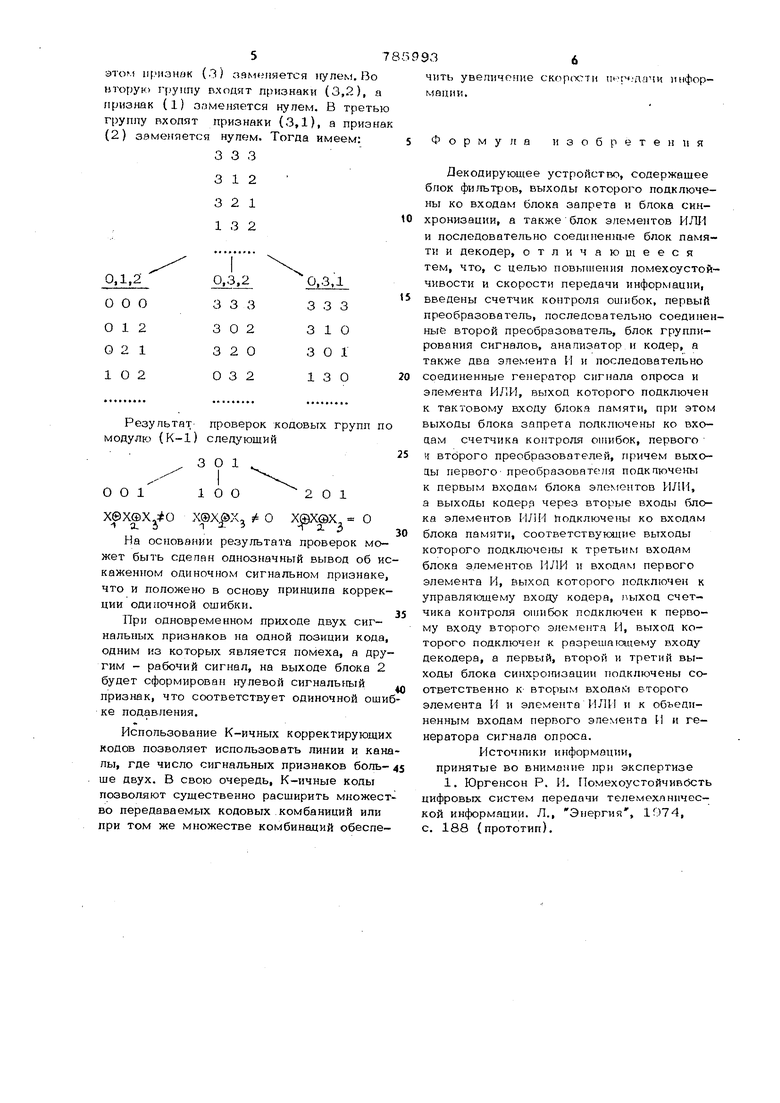

Более подробно работу предложенного устройства можно пояснить на примере трехэлементного кода (v 3) с числом сигнальных признаков (основанием кода) К 4. Число кодовых комбинаций определяется по формуле

ГЛ(К-1)(4--1) 9.

Метод построения кода заключается в том что строится избыточный (К-1) 3 основной код на (Г1 - 1) га 2 позициях. Кодовое расстояние равно d ; 1. Затем на дополнительной (третьей) контрольной позиции устанавливаются симвопы с помощью проверки:

/где Х ,Л, , Xj-,значение сигнального признака на VI позициях,® - сумма по модулю (К-1).

. Использование дополнительной позиции увеличивает кодовое расстояние до d 2.

Нулевой сигнальный признак заменяется на . К-й сигнальный признак, что повышает кодовое расстояние до Qi- 4. При этом код позволяет обнаружить две ошибки и одр1у из них исправить. Таким образом, при К 4, и 3, М (К-1) З - 9 имеем:

Принимаемый код разбивается на (К-1 )3 группы кодов. В первую группу входят сигнальные признаки (1, 2), при этом признак (.3) заменяется нулем. Во нторук груипу входят признаки (3,2), а признак (1) отменяется нулем. В третью группу рхолят признаки (3,1), а признак (2) зэменпется нупем. Тогда имеем: 333 0.1,2 000 012 021 Результат проверок кодовых групп по модулю (К-1) следующий О О 1 Х©Х®Х.О - CL i На основании результата проверок может быть сделан однозначный вывод об ис каженном одиночном сигнальном признаке, что и положено в основу принципа коррекции одиночной ошибки. При одновременном приходе двух сигнальных признаков на одной позиции кода, одним из которых является помеха, а дру гим - рабочий сигнал, на выходе блока 2 будет сформирован нулевой сигнальный признак, что соответствует одиночной оши ке подавления. Использование К-ичных корректирующих кодов позволяет использовать линии и кан лы, где число сигнальных признаков больше двух. В свою очередь, К-ичные коды позволяют существенно расширить множест во передаваемых кодовых комбаниций или при том же множестве комбинаций обеспечить увегшчрние скорсхтщ пер .Дачи информации. Формула изобретения Декодирующее устройство, содержащее блок фильтров, выходы которого подключены ко входам блока запрета и блока синхронизации, а также блок элементов ИЛИ и последовательно соединенш-ге блок памяти и декодер, отличающееся тем, что, с целью повышения помехоустойчивости и скорости передачи информации, введены счетчик контроля ошибок, первый преобразователь, последовательно соединенные второй преобразователь, блок группирования сигналов, анализатор и кодер, а также два элемента И и последовательно соединенные генератор сигнала опроса и элемента И/5И, выход которого подключен к тактовому входу блока памяти, при этом выходы блока запрета подключены ко вхо- цам счетчика контроля ошибок, первого ч второго преобразователей, причем выхоаы первого- преобразоватеия подкпючены к первым входам блока элементов ИЛИ, а выходы кодера через вторые входы блока элементов ИЛИ подключены ко входам блока памяти, соответствукяцие выходы которого подключены к третьим входам блока элементов И/Ш и входам первого элемента И, выход которого подключен к управляющему входу кодера, лыход счетчика контроля О1иибок подключен к первому входу второго элемента И, выход которого подключен к разрешающему входу декодера, а первый, BTopofi и третий выходы блока синхрО Шзации подключены соответственно к вторым входам второго элемента И и элемента ИЛИ и к объединенным входам первого элемента И и генератора сигнала опроса. Источники информации, принятые во внимание при экспертизе 1. Юргенсон Р. И. ГТомехоустойчивбсть цифровых систем передачи телемеханической информации. Л., Энергия, 1974, с. 188 (прототип).

Авторы

Даты

1980-12-07—Публикация

1978-11-01—Подача