первой, второй, третьей и четвертой подгрупп элементов И каждой группы подключены к соответствующим вхддам соответствующих узлбв тетрадного суммирования со смещением старших разрядов в сторону увеличения разрядности на один двоичный разряд, начиная со второй подгруппы элементов относительно первой подгруппы элементов И, а выходы первой подгруппы элементов И каждой группы подключены к соответствующим входам соответствующих узлов тетрадного суммирования со смещением старших разрядов в сторону увеличения разрядности на четыре двоичных разряда относительно первой подгруппы элементов И предыдущей группы, выход И-разрядного регистра множимого соединен с входом первого узла удвоения первыми информационными входами первого, второго и третьего коммутаторов блока кратных множимого, выход первого узла удвоения которого соединен с вторым информационным входом первого коммутатора и входом второго узла удвоения блока кратных множимого, выход второго узла удвоения которого соединен с вторым информационным входом второго коммутатора и входом третьего узла удвоения блока кратных множимого, выход которого соединен с вторым инфор.мационньтм входом третьего комму.татора, управляющие входы коммутаторов соединены с группой входов задания режима работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее m -разрядные регистры множителя и множимого (т- разрядность десятичных сомножителей), 2|ц-разрядный регистр результата, 2т узлов тетрадного суммирования, 2т-1 коммутаторов, 2г«-1 узлов преобразования двоичного кода в десятичньй, 2т-разрядный сумматор, причем выходы узлов тетрадного суммирования, кроме 2т-го, соединены с информационными входами соответствукяцих узлов преобразования двоичного кода в десятичный и с пер- : выми информационными входами соответствующих коммутаторов, вторые информационные входы которых соединены с выходами соответствующих узлов преобразования двоичного кода в десятичный, выходы коммутаторов соединены с соответствующими 2/0-1 информационными входами 2т -разрядного сумматора, вькоды которого соединены соответственно с информационными входами -2гр-разрядного регистра результата, информационный 2т-й вход сумматора соединен с выходом 2)П-го узла тетрадного суммирования, управляющие входы коммутаторов и сумматора соединены с группой вхо дов задания режима работы устройства, отличающееся тем, что, с целью повышения быстродействия в него введены блок формирования кратных множимого, содержащий первьй, второй и третий узлы удвоения, первый, второй и третий коммутаторы, а также блок частичных произведений, содержащий m групп элементов И, причем каждая группа элементов И содержит первую, вторую, третью и четвертую подгруппы элементов И, причем первая и вторая подгруппы i каждой группы элементов И содержат 4 m элементов И, третья подгруппа (Л каждой группы содержит 4in 1 элементов И, -четвертая подгруппа каждой группы содержит 4ггн-2 элементов И, первые входы элементов И каждой подгруппы каждой группы объединены :и подключены к соответствующим разрядам П1 -разрядного регистра множителя, вторые входы первой подгруппы каждой группы элементов И подключены к выходам соответствующих разрядов регистра множимого, вторые входы второй подгруппы элементов И каждой группы подключены к выходам соответствующих разрядов первого коммутатора блока кратных множимого вторые входы третьей подгруппы элементов И каждой группы подключены к выходам соответствующих разрядов второго коммутатора блока кратных множимого, вторые входы четвертой подгруппы элементов И каждой группы подключены к выходам соответствующих разрядов третьего коммутатора блока кратных множимого, выходы

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействуюпщх устройств для умножения чисел, представленных в двоичной и десятичной системах счисления.

Известно множительное устройство, содержащее накопитель (блок формирования произведения) и осуществляющее умножение множимого X на множитель -ji Ч,( , причем в предварительно очищенный накопитель множимое X прибавляется i| раз, затем оно сдвигается влево на один разряд и вновь прибавляется в накопитель 1|,2. раз, и так до тех пор, пока не будут обработан1з1 все разряды множителя У. Это устройство позволяет умножить двоичные и десятичные числа 1J.

Существенным недостатком известного устройства является низкое быстродействие, особенно при умножении десятичных чисел. Так, для перемножения двух m -разрядных десятичных чисел в известном устройстве требуется время, примерно равное

A,5mt ,

где-Ь д- время суммирования двух m разрядных десятичных чисел. Здесь, предполагается, что цифры О, 1,2,...,9

появляются во всех разрядах множителя У с равной вероятностью.

Наиболее близким по технической сущности к изобретению является

множительное устройство, содержащее гтг-разрядный регистр множителя (tnразрядность десятичных сомножителей) (Щ+1)-разрядный регистр множимого со схемой удвоения, 2т -разрядный

регистр результата (в известном устройстве он подразумевается), матрицу из (m4-l)m узлов тетрадного умножения, 2 W узлов тетрадного суммирования, 2гГ1 буферных регистров, 2in узлов преобразования двоичного кода в десятичный , 2 m коммутаторов и блок суммирования, причем первые входы узлов тетрадного умножения матрицы соединены с выходами соответствующих тетрад регистра множимого, а вторые входы соединены с выходами младших разрядов соответствующих тетрад регистра множителя, входы узлов тетрадного суммирования соединены с выходами соответствующих буферных регистров и узлов тетрадного умножения, а вькоды соединены с входами соответствующих буферных регистров и узлов преобразования двоичного

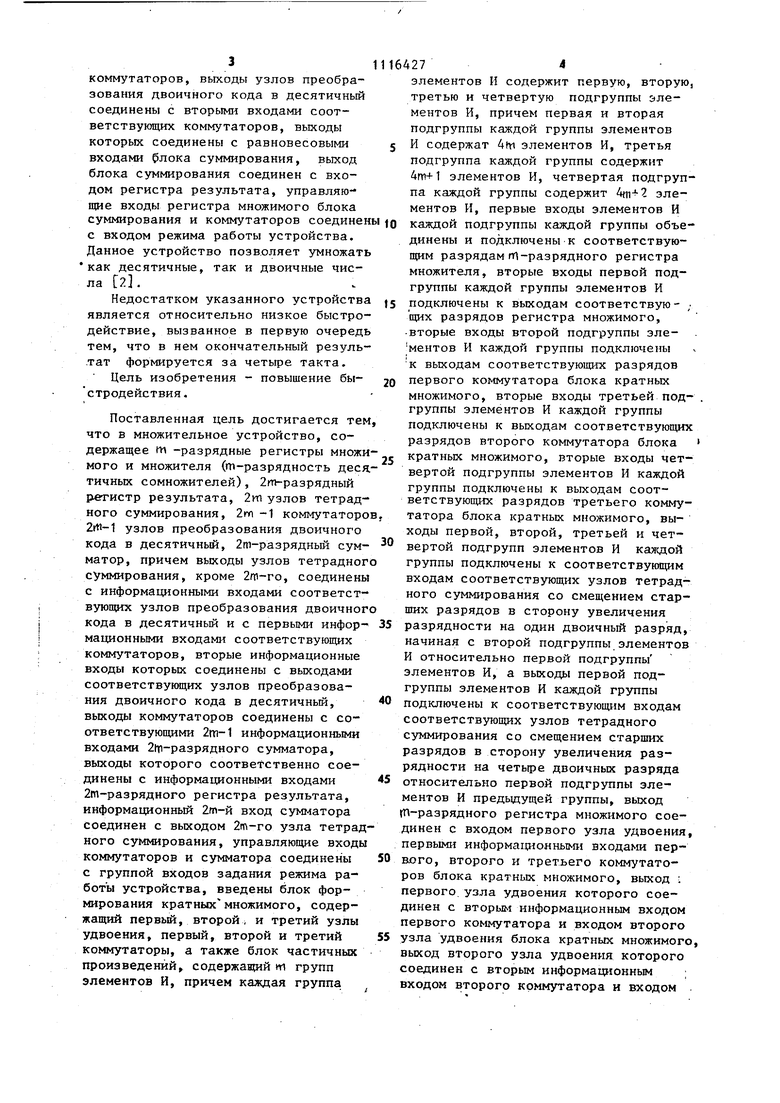

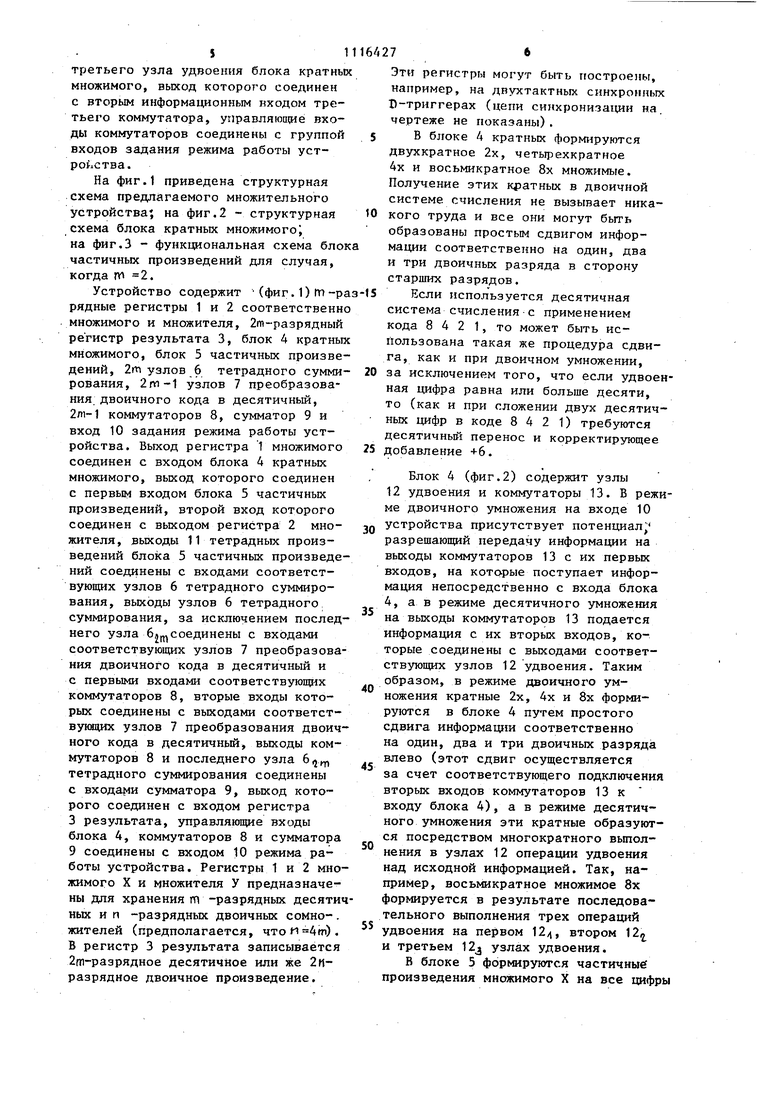

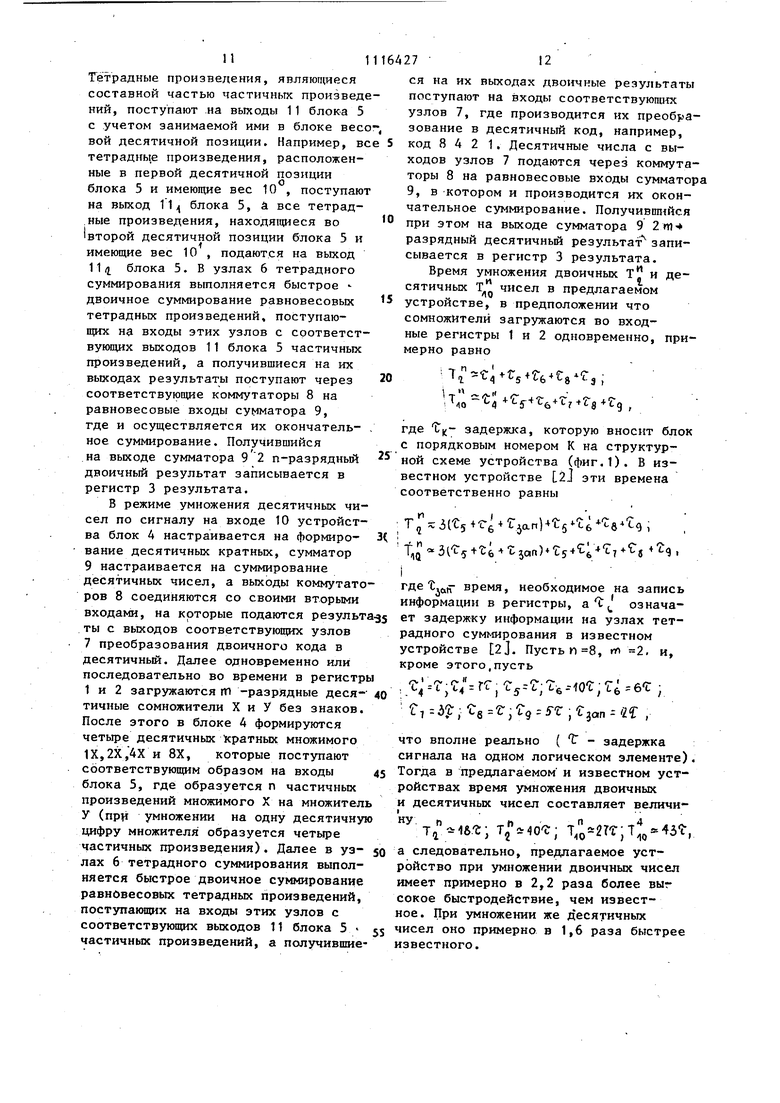

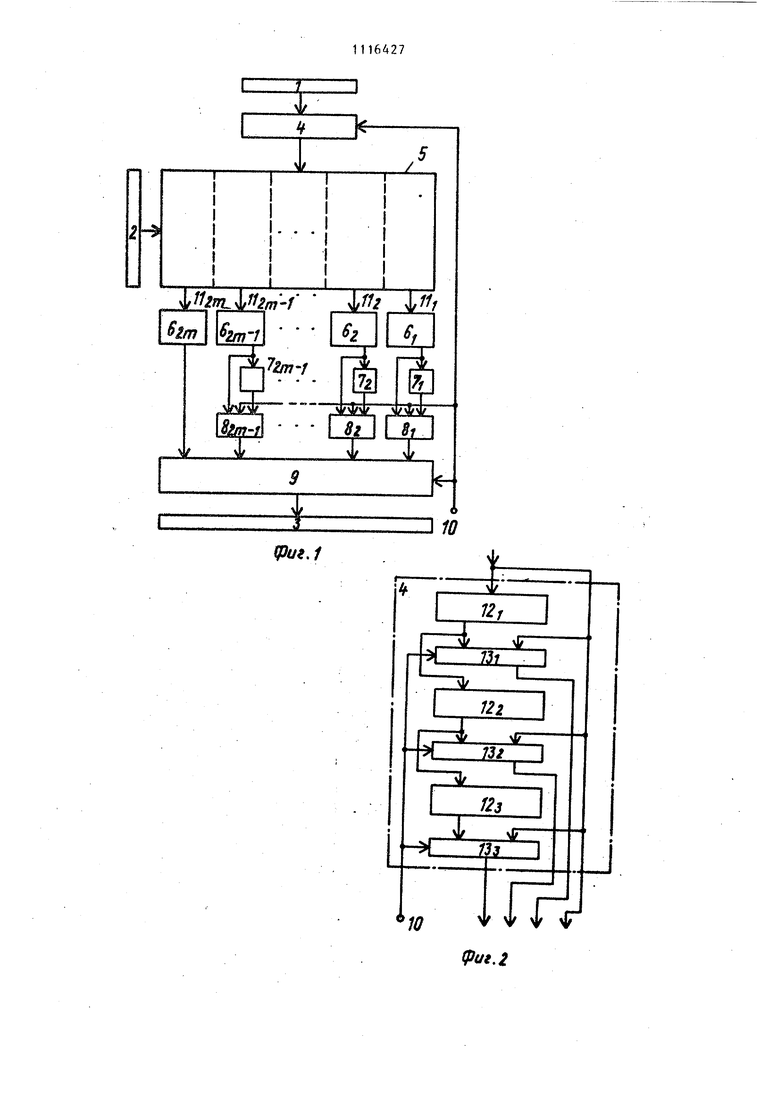

кода в десятичный, а также соединены с первыми входами соответствующих коммутаторов, выходы узлов преобразования двоичного кода в десятичный соединены с вторыми входами соответствующих коммутаторов, выходы которых соединены с равновесовыми входами рлока суммирования, выход блока суммирования соединен с входом регистра результата, управляющие входы регистра множимого блока суммирования и коммутаторов соединен с входом режима работы устройства. Данное устройство позв.оляет умножать как десятичные, так и двоичные числа 2. Недостатком указанного устройства является относительно низкое быстродействие, вызванное в первую очередь тем, что в нем окончательный результат формируется за четьфе такта. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что в множительное устройство, содержащее И1 -разрядные регистры множи мого и множителя (т-разрядность деся тичных сомножителей), 2т-разрядный регистр результата, 2ni узлов тетрадного суммирования, 2т -1 коммутаторо 2rti-1 узлов преобразования двоичного кода в десятичный, 2т-разрядный сумматор, причем выходы узлов тетрадног суммирования, кроме 2гг1-го, соединены с информационными входами соответствуюпщх узлов преобразования двоичног кода в десятичный и с первыми информационными входами соответствующих коммутаторов, вторые информационные входы которых соединены с выходами соответствующих узлов преобразования двоичного кода в десятичный, выходы коммутаторов соединены с соответствующими 2п1-1 информационными входами 2 тl-paзpяднoгo сумматора, выходы которого соответственно соединены с информационными входами 2т-разрядного регистра результата, информационный 2т-й вход сумг-iaTopa соединен с выходом 2т-го узла тетрад ного суммирования, управляющие входы коммутаторов и сумматора соединены с группой входов задания режима работы устройства, введены блок формирования кратных множимого, содержащий первый, второй , и третий узлы удвоения, первый, второй и третий коммутаторы, а также блок частичных произведений содержащий m групп элементов И, причем каждая группа элементов И содержит первую, вторую, третью и четвертую подгруппы элементов И, причем первая и вторая подгруппы каждой группы элементов И содержат 4м элементов И, третья подгруппа каждой группы содержит 4т+1 элементов И, четвертая подгруппа каждой группы содержит элементов И, первые входы элементов И каждой подгруппы каждой группы объединены и подключены к соответствующим разрядамгп-разрядного регистра множителя, вторые входы первой подгруппы каждой группы элементов И подключены к выходам соответствую- ; щих разрядов регистра множимого, вторые входы второй подгруппы элементов И каждой группы подключены к выходам соответствующих разрядов первого коммутатора блока кратных множимого, вторые входы третьей под- . группы элементов И каждой группы подключены к выходам соответствующих разрядов второго коммутатора блока кратных множимого, вторые входы четвертой подгруппы элементов И каждой группы подключены к выходам соответствующих разрядов третьего коммутатора блока кратных множимого, выходы первой, второй, третьей и четвертой подгрупп элементов И каждой группы подключены к соответствующим входам соответствующих узлов тетрадного суммирования со смещением старших разрядов в сторону увеличения разрядности на один двоичный разряд, начиная с второй подгруппы элементов И относительно первой подгруппы элементов И, а выходы первой подгруппы элементов И каждой группы подключены к соответствующим входам соответствующих узлов тетрадного суммирования со смещением старших разрядов в сторону увеличения разрядности на четыре двоичных разряда относительно первой подгруппы элементов И предыдущей группы, выход ГП-разрядного регистра множимого соединен с входом первого узла удвоения, первыми информа1шонными входами первого, второго и третьего коммутаторов блока кратньвс множимого, выход ; первого, узла удвоения которого соединен с вторым информационным входом первого коммутатора и входом второго узла удвоения блока кратных множимого, выход второго узла удвоения которого соединен с вторым информационным ; входом второго коммутатора и входом третьего узла удвоения блока кратны множимого, выход которого соединен с вторым информационным входом третьего коммутатора, управляюа ие входы коммутаторов соединены с группой входов задания режима работы устройства. На фиг.1 приведена структурная схема предлагаемого множительного устройства; на фиг.2 - структурная схема блока кратных множимогоi на фиг.З - функциональная схема бло частичных произведений для случая, когда rvi 2. Устройство содержит (фиг. 1) т-р рядные регистры 1 и 2 соответственн множимого и множителя, 2т-разрядный регистр результата 3, блок 4 кратны множимого, блок 5 частичных произве дений, 2гГ| узлов 6 тетрадного сумми рования, 2т-1 узлов 7 преобразования, двоичного кода в десятичньй, 2т-1 коммутаторов 8, сумматор 9 и вход 10 задания режима работы устройства. Выход регистра 1 множимого соединен с входом блока 4 кратных множимого, выход которого соединен с первым входом блока 5 частичных произведений, второй вход которого соединен с выходом регистра 2 множителя, выходы 11 тетрадных произведений блока 5 частичных произведе ний соединены с входами соответствующих узлов 6 тетрадного суммирования, выходы узлов 6 тетрадного суммирования, за исключением послед него узла бд,соединены с входами соответствующих узлов 7 преобразова ния двоичного кода в десятичный и с первыми входами соответствующих коммутаторов 8, вторые входы которых соединены с выходами соответствунядих узлов 7 преобразования двоич ного кода в десятичный, выходы коммутаторов 8 и последнего узла 6,j тетрадного суммирования соединены с входами сумматора 9, выход которого соединен с входом регистра 3 результата, управляющие входы блока 4, коммутаторов 8 и сумматора 9 соединены с входом 10 режима работы устройства. Регистры 1 и 2 мно жимого X и множителя У предназначены для хранения т -разрядных десяти ньк и п -разрядных двоичных сомно-. жителей (предполагается, ). В регистр 3 результата записывается 2т-разрядное десятичное или же 2ttразрядное двоичное произведение. Эти регистры могут быть построены, например, на двухтактных синхронных В-триггерах (цепи сиихрониза1щи на. чертеже не показаны). В б;гоке 4 кратных формируются двухкратное 2х, четырехкратное 4х и восьмикратное 8х множимые. Получение этих кратных в двоичной системе счисления не вызывает никакого труда и все они могут быть образованы простым сдвигом информации соответственно на один, два и три двоичных разряда в сторону старших разрядов. Если используется десятичная система счисления с применением кода 842 1, то может быть использована такая же процедура сдвига, как и при двоичном умножении, за исключением того, что если удвоенная цифра равна или больше десяти, то (как и при сложении двух десятичных цифр в коде 8421) требуются десятичный перенос и корректирующее добавление +6. Блок 4 (фиг.2) содержит узлы 12 удвоения и коммутаторы 13. В режиме двоичного умножения на входе 10 устройства присутствует потенциал разрешающий передачу информации на выходы коммутаторов 13 с их первых входов, на которые поступает информация непосредственно с входа блока 4, а в режиме десятичного умножения на выходы коммутаторов 13 подается информация с их вторых входов, которые соединены с выходами соответствующих узлов 12 удвоения. Таким образом, в режиме двоичного умножения кратные 2х, 4х и 8х формируются в блоке 4 путем простого сдвига информации соответственно на один, два и три двоичных разряда влево (этот сдвиг осуществляется за счет соответствующего подключения вторых входов коммутаторов 13 к входу блока 4), а в режиме десятичного умножения эти кратные образуются посредством многократного выполнения в узлах 12 операции удвоения над исходной информацией. Так, например, восьмикратное множимое 8х формируется в результате последовательного выполнения трех операций удвоения на первом 12, втором 122 и третьем 12 узлах удвоения. В блоке 5 формируются частичные произведения множимого X на все цифры

7

множителя У, причем независимо от того, используется ли в устройстве двоичная или десятичная система счисления, число частичных произведений равно п . Это связано с тем, что в режиме двоичного умножения образуются частичные произведения множимого на .каждую двоичную цифру г -разрядного множителя, а в режиме десятичного умножения формируются четьфе частичных произведения мноткимого на каждую десятичную цифру Шразрядного множителя, т.е. то же и, 1ак как л .

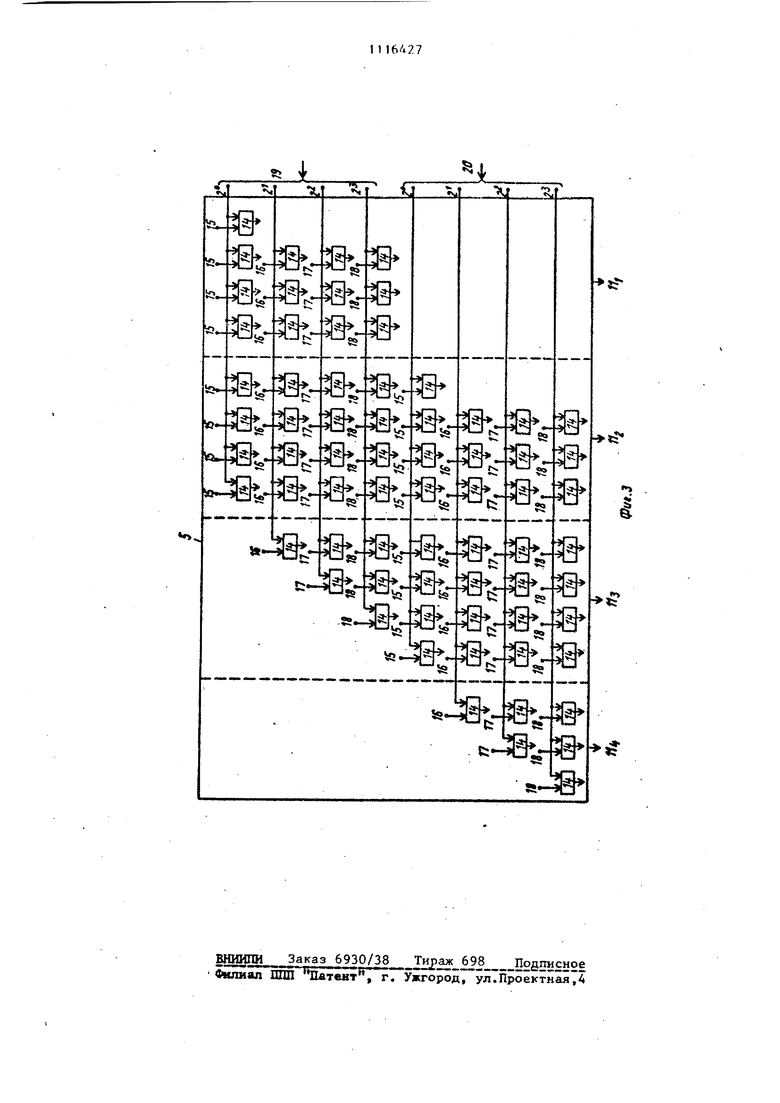

Блок 5 содержит (фиг.З) п 8 линее элементов И 14 (рассматривается случай перемножения в устройстве 8-разрядных двоичных или 2-разрядных десятичных чисел). На первые входы элементов И 14 каждой линейки из блока 4 кратных поступает соответствующее кратное множимого X (по иинам 15 подается одинарное множимое по шинам 16 - удвоенное множимое 2Х; по шинам 17 - учетверенное множимое 4Х и по шинам 18 - увосьмиренное множимое 8-Х), на вторые входы всех элементов И 14 каждой линейки поступает значение соответствующего двоичного разряда регистра 2 множителя (по шинам 19 в блок 5 поступают значения двоичных разрядов младшей тетрады регистра 2 множителя, а по шинам 20 - значения двоичных разрядов старшей тетрады регистра 2 множителя). На выходах одной линейки элементов И 14 образуется одно частичное произведение, а всего в блоке 5 формируется восемь частичных произведений. Выходы элементов И 14, расположенньтх в первой десятичной позиции блока 5, образуют первый выход 111( значения тетрадных произведений блока 5 частичных произведений (на чертеже эти элементы И 14 расположены первыми справа и отделены штриховой линией). Подобным образом образуются второй 11 третий 11 и четвертый 11| выходы тетрадньк произведений блока 5 частичных произведений.

Узлы 6 тетрадного суммирования предназначены дпя быстрого суммирования тетрадных произведений, сформированных в соответствующей десятичной позиции блока 5 частичных произведений. Они могут бьггь построены самыми различными способами.

8

Результаты, сформированные на выходах узлов 7 преобразовагтя двоичного кода в десятичный, используютоя в устройстве только п режиме десятичного умножения. Эти узлы предназначены для преобразования двоичного кода, полученного на выходе соответствующего узла 6 тетрадного суммирования, в двоично-десятичньй код

8 4 2 1. Они могут быть построены с использованием постоянного запом нающего устройства по таблицам истинности. Для определенности детально рассмотрим синтез первого узла

5 7ц преобразования двоичного кода в десятичный (другие узлы 7 строятся аналогично). Сначала следует определить, какое максимальное значение двоичного кода должен преобразовывать

0 этот узел. При этом будем руководствоваться следующим. На выходах элементов И 14, расположенных в первой десятичной позиции блока 5 и образующих его первьпЧ выход 11 тет5 радных произведений при умножении двух десятичных чисел могут одновременно фop п poвaтьcя следующие максимально возможные значения тетрадных произведений: 1001, 1000 и 0110,

0 Эти значения тетрадньк произведений возможга в устройстве только тогда, когда младшая десятичная цифра множимого X равна 9, а младшая десятичная цифра множителя У равна 7. Вви5 ДУ этого на выходе первого узла 6у тетрадного суммирования не может быть сформировано значение двоичного кода, превышающее величину ЮОН +1000+0100 10111. А поэтому узел 7

0 преобразования двоичного кода, в десятичный может быть построен на ПЗУ емкостью в двадцать четыре 2-раз,рядных десятичных слова.

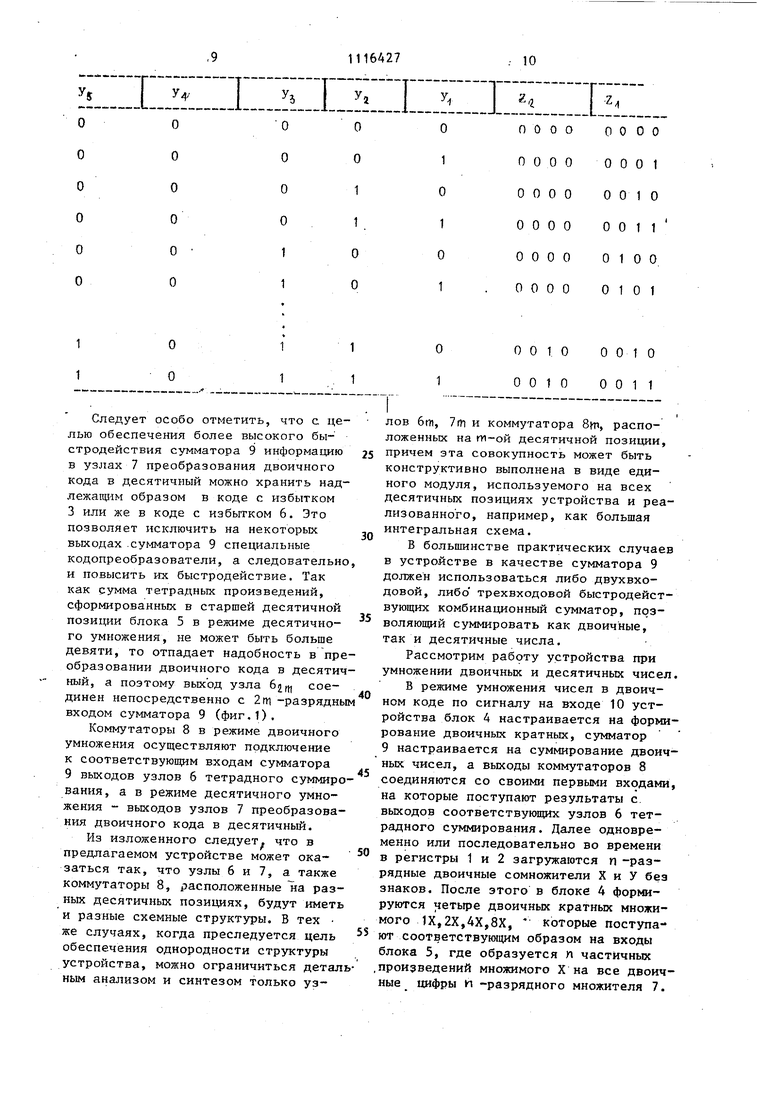

5, В таблице приведен фрагмент истин ности узла 7 преобразования двоичного кода в десятичный, в которой через У5, У4, УЗ, У, УЧ обозначен двоичный код суммы тетрадных произQ ведений, сформированный на выходе первого узла 6 тетрадного суммирования и поступающий на вход узла 7i . На выходе этого узла образуется 2-разрядное десятичное число .{,2 j в коде 8421. Возрастание индексов - при буквенных обозначениях здесь принято в направлении старших разрядов.

111 П } 111л11 1111 Следует особо отметить, что с целью обеспечения более высокого быстродействия сумматора 9 информацию в узлах 7 преобразования двоичного кода в десятичный можно хранить надлежащм образом в коде с избытком 3 или же в коде с избытком 6. Это позволяет исключить на некоторых выходах .сумматора 9 специальные кодопреобразователи, а следовательно и повысить их быстродействие. Так как сумма тетрадных произведений, сформированных в старшей десятичной позиции блока 5 в режиме десятичного умножения, не может быть больше девяти, то отпадает надобность в пре образовании двоичного кода в десятич ный, а поэтому выход узла соединен непосредственно с 2т -разрядны входом сумматора 9 (фиг.1). Коммутаторы 8 в режиме двоичного умножения осуществляют подключение к соответствуюпщм входам сумматора 9 выходов узлов 6 тетрадного суммиро вания, а в режиме десятичного умножения - вьпсодов узлов 7 преобразования двоичного кода в десятичный. Из изложенного следует, что в предлагаемом устройстве может оказаться так, что узлы 6 и 7, а также коммутаторы 8, расположенные Ъа разньк десятичных позициях, будут иметь и разные схемные структуры. В тех же случаях, когда преследуется цепь обеспечения однородности структуры устройства, можно ограничиться детал ным анализом и синтезом только узZ. 00010 0010 10010 0011 , лов 6tn, 7m и коммутатора 8)ti, расположенных на ги-ой десятичной позиции, причем эта совокупность может быть конструктивно выполнена в виде единого модуля, используемого на всех десятичных позициях устройства и реализованного, например, как большая интегральная схема. В большинстве практических случаев в устройстве в качестве сумматора 9 должен использоваться либо двухвходовой, либо трехвходовой быстродействующих комбинационный сумматор, позволяющий суммировать как двоичные, так и десятичные числа. Рассмотрим работу устройства при умножении двоичных и десятичных чисел. В режиме умножения чисел в двоичном коде по сигналу на входе 10 устройства блок 4 настраивается на формирование двоичных кратных, сумматор 9 настраивается на суммирование двоичных чисел, а выходы коммутаторов 8 соединяются со своими первыми входами, на которые поступают результаты с. выходов соответствунщих узлов 6 тетрадного суммирования. Далее одновременно или последовательно во времени в регистры 1 и 2 загружаются п -разрядные двоичные сомножители X и У без знаков. После этого в блоке 4 формируются четыре двоичных кратных множимого 1Х,2Х,4Х,8Х, которые поступают соответствующим образом на входы блока 5, где образуется п частичных произведений множимого X на все двоичные цифры м -разрядного множителя 7. 111 Тетрадные произведения, являющиеся составной частью частичных произведе ний, поступают .на выходы 1 1 блока 5 с учетом занимаемой ими в блоке весо вой десятичной позиции. Например, вс тетрадные произведения, расположенные в первой десятичной позиции блока 5 и имеющие вес 10 , поступают на выход 11;( блока 5, а все тетрад.ные произведения, находящиеся во второй десятичной позиции блока 5 и имеющие вес 10 , подаются на выход 11 ti блока 5. В узлах 6 тетрадного суммирования выполняется быстрое двоичное суммирование равновесовых тетрадных произведений, поступающих на входы этих узлов с соответствующих выходов 11 блока 5 частичных произведений, а получившиеся на их выходах результаты поступают через соответствующие коммутаторы 8 на равновесовые входы сумматора 9, где и осуществляется их окончательное суммирование. Получившийся на выходе сумматора 9 2 п-разрядный двоичный результат записывается в регистр 3 результата. В режиме умножения десятичных чисел по сигналу на входе 10 устройства блок 4 настраивается на формирование десятичных кратных, сумматор 9 настраивается на суммирование десятичных чисел, а выходы коммутато ров 8 соединяются со своими вторыми входами, на которые подаются результ ты с выходов соответствующих узлов 7 преобразования двоичного кода в десятичный. Далее одновременно или последовательно во времени в регистр 1 и 2 загружаются гп -разрядные десятичные сомножители X и У без знаков. После этого в блоке 4 формируются четыре десятичных кратных множимого 1Х,2Х,4Х и 8Х, которые поступают соответствующим образом на входы блока 5, где образуется п частичных произведений множимого X на множител У (ПРИ умножении на одну десятичну цифру множителя образуется четыре частичных произведения). Далее в узлах 6 тетрадного суммирования выполняется быстрое двоичное суммирование равновесовых тетрадных произведений, поступающих на входы этих узлов с соответствующих выходов 11 блока 5 частичных произведений, а получившие 27 ся на их выходах двоичные результаты поступают на входы соответствующих узлов 7, где производится их npeo6{jaзование в десятичный код, например, код 8421. Десятичные числа с выходов узлов 7 подаются через коммутаторы 8 на равновесовые входы сумматора 9, в котором и производится их окончательное суммирование. Получившийся при этом на выходе сумматора 9 2 т- разрядный десятичньй результат записывается в регистр 3 результата. Время умножения двоичных Т и десятичных Т чисел в предлагаемом устройстве, в предположении что сомножители загружаются во входные регистры 1 и 2 одновременно, примерно равно . + т - Ч где задержка, которую вносит блок с порядковым номером К на структурной схеме устройства (фиг.1). В известном устройстве 12. эти времена соответственно равны Tj:c3(t5+T + rjan)t5-t6 te tg, t,J -3(Г5+t; 4г jan) . время, необходимое на запись где 4счГ информации в регистры, at означает задержку информации на узлах тетрадного суммирования в известном устройстве t2j. Пусть п 8, гя 2, и, кроме этого,пусть ,(Г;.г,,е5--е;Те.мо(:, ,(Г,5--5-Г, , что вполне реально ( ТГ - задержка сигнала на одном логическом элементе). Тогда в предлагаемом и известном устройствах время умножения двоичных и десятичных чисел составляет величи Tj -ioJr; Т 27Т;Т; 43г, а следовательно, предлагаемое устройство при умножении двоичных чисел имеет примерно в 2,2 раза более выг сокое быстродействие, чем иэвестное. При умножении же Десятичньпс чисел оно примерно в 1,6 раза быстрее известного.

9й/г./

4

Itj.

Г

;j

ш

..J

;jj

V V у

W ut.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бут Э, и Бут К | |||

| Автоматические цифровые машины | |||

| Н | |||

| ГИФМЛ | |||

| Автоматический сцепной прибор американского типа | 1925 |

|

SU1959A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-30—Публикация

1982-10-06—Подача