Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных

быстродействующих устройств для ум- ножения двоичных и десятичных чисел.

Цель изобретения - повышение быстродействия устройства за счет сокращения времени выполнения в нем умножения двоичных чисел.

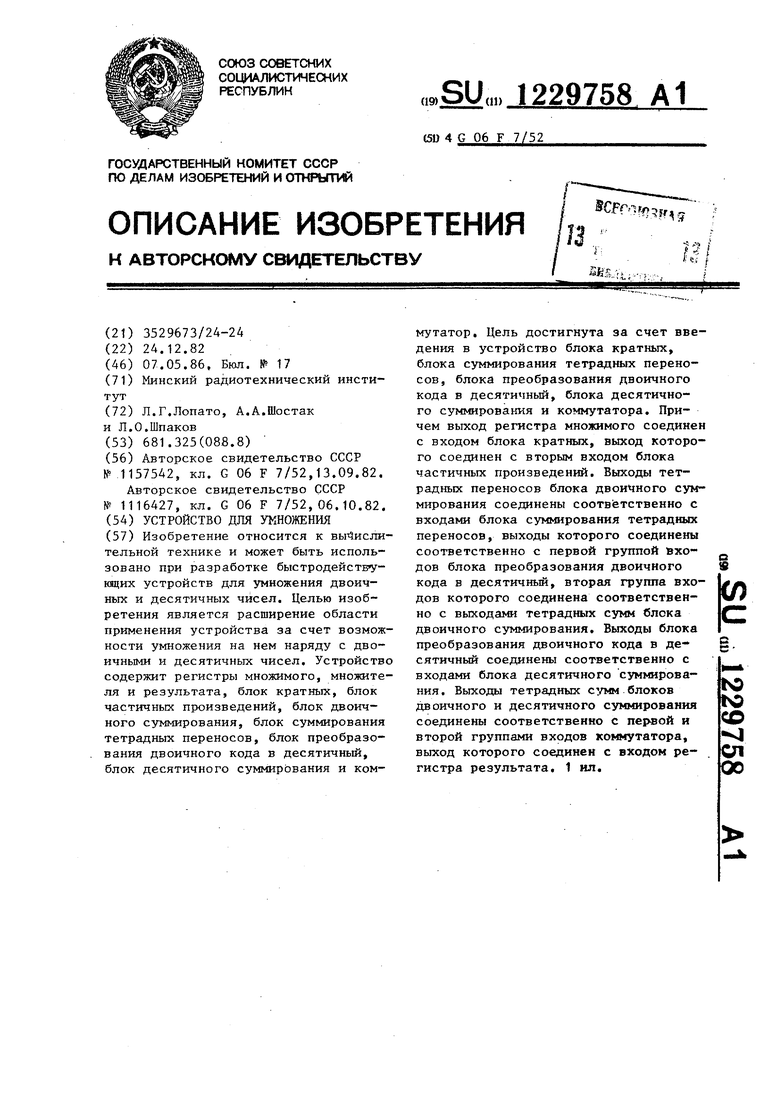

На чертеже приведена структурная схема устройства (число десятичных разрядов у множимого и множителя равно trv ).

Устройство содержит регистры 1-3 соответственно множимого, множителя и произведения, блок 4 формирования кратных множимого, блок 5 « юрмирова- ния частичных произведений, ysjibi тетрадного суммирования, узлы 7, -72,суммирования тетрадных переносов, узлы 8,-8, .преобразования двоичного кода в десятичный, блок 9 десятичного суммирования, коммутаторы 10,-10 первой группы, коммутаторы

ные входа коммутаторов 11, 1,2 ое- динены с выходами переносов соответствующих узлов .тетртдного суммирования с первого по предпоследний

,. и входами соответствумцих узлов 7, - 72,1сум:мирования тетрадных переносов, выходы которых подключены к входам старших разрядов соответствующих узлов 8 ,преобразования двоичного

0 кода в десятичный, выходы которых подключены в соответствии со значе- ниям111 весов разрядов к входам соот- ветствукшщх разрядов блока 9 десятичного суммирования, выходы коммутато15 ров 11,-112.второй группы подключены к входам последующих узлов тетрадного суммирования, управлягапир входы коммутаторов 10, -lOjrrx 11 - 112.,первой и второй групп подключе2Q ны к входу 12 режима устройства. Регистры 1 и 2 соответственно множимого и множителя предназначены для хранения ьп-разрядных десятичных и п-разрядных двоичных сомно-

11,-11 второй группы и вход 12 ре- jj жителей (предполагается, что 4ni).

жима устройства.

Выходы регистра 1 множимого подключены к информационным входам блока 4 формирования кратных множ1шого, вход управления режимом работы которого подключен к входу 12 режима устройства, выходы регистра 2 множителя и блока 4 формирования кратных множимого подключены к входам блока 5 формирования частичных произведений, тетрадные выходы которого подключены к входам соответствующих узлов 6 игг, тетрадного суммирования, тетрадные выходы узлов 6 -6,, 2тетрад- ного суммирования с первого по предпоследний подключены к входам младших разрядов соответствующих узлов 8 -82,(Преобразования двоичного кода в десятичный, тетрадный выход последнего узла 6 тетрадного суммирования подключен к входу старшего разря™ да блока 9 десятичного, суммирования, тетрадные выходы узлов 6 тетрадного суммирования подключены к первым информационным входам соответствующих коммутаторов 10 г гт Рвой группы, вторые информационные входы которых, подключены к выходам соответ ствующих разрядов блока 9 десятичного суммирования, выходы комм гтато- ров первой группы подключены к входам соответствующих разрядов регистра 3 произведения, информацион310

35

XI5

f

55

В регистр 3 произведения записьшается 21-п-разрядное десятичное или же

2 1-разрядное двоичное произведение

В блоке 4 формируются двухкратное, четырехкратное и восьмикратное множимые. Получение этих кратных в двоичной системе счисления не вызывает никакого труда и все они могут быть образованы про.стым сдвигом кода множимого соответственно на один два и три двоичных разряда в сторону его старших разрядов. При использовании десятичной системы счисления с применением кода 8421 может быть использована такая же процедура сдви га, как и при двоичной системе счисления, за исключением того, что если удвоенная десятичная цифра равна или больше десяти, то (как и при сложении двух десятичных цифр в коде 8421) требуются десятичный перенос и корректирующее добавление +6. Блок 4 формирования кратных множимого может быть реализован на основе трех последовательно соединенных узлов удвоения и трех коммутаторов.

Блок: 5 предназначен для формирования частичных произведений и может быть построен с помощью определенным образом смещенных линеек двухвходо- вых элементов И, На первые входы элементов И каждой линейки из блока 4 кратныз : поступает значение соответствующего кратного множимого, а на

ные входа коммутаторов 11, 1,2 ое- динены с выходами переносов соответствующих узлов .тетртдного суммирования с первого по предпоследний

и входами соответствумцих узлов 7, - 72,1сум:мирования тетрадных переносов, выходы которых подключены к входам старших разрядов соответствующих узлов 8 ,преобразования двоичного

кода в десятичный, выходы которых подключены в соответствии со значе- ниям111 весов разрядов к входам соот- ветствукшщх разрядов блока 9 десятичного суммирования, выходы коммутаторов 11,-112.второй группы подключены к входам последующих узлов тетрадного суммирования, управлягапир входы коммутаторов 10, -lOjrrx 11 - 112.,первой и второй групп подключены к входу 12 режима устройства. Регистры 1 и 2 соответственно множимого и множителя предназначены для хранения ьп-разрядных десятичных и п-разрядных двоичных сомно-

жителей (предполагается, что 4ni).

В регистр 3 произведения записьшается 21-п-разрядное десятичное или же

2 1-разрядное двоичное произведение .

В блоке 4 формируются двухкратное, четырехкратное и восьмикратное множимые. Получение этих кратных в двоичной системе счисления не вызывает никакого труда и все они могут быть образованы про.стым сдвигом кода множимого соответственно на один два и три двоичных разряда в сторону его старших разрядов. При использовании десятичной системы счисления с применением кода 8421 может быть использована такая же процедура сдви га, как и при двоичной системе счисления, за исключением того, что если удвоенная десятичная цифра равна или больше десяти, то (как и при сложении двух десятичных цифр в коде 8421) требуются десятичный перенос и корректирующее добавление +6. Блок 4 формирования кратных множимого может быть реализован на основе трех последовательно соединенных узлов удвоения и трех коммутаторов.

Блок: 5 предназначен для формирования частичных произведений и может быть построен с помощью определенным образом смещенных линеек двухвходо- вых элементов И, На первые входы элементов И каждой линейки из блока 4 кратныз : поступает значение соответствующего кратного множимого, а на

их вторые входы подается значение соответствующего двоичного разряда регистра 2 мнолсителя. На выходах элементов И одной линейки образуется одно час гичное произведение, а всего в блоке 5 формируется л частичных произведений. Выходы элементов И, расположенных в одной и той же весовой позиции (десятичной или шестнадцатиричной) блока 5, образуют его один тетрадный выход. Всего в блоке

5имеется 2н, тетрадных выходов.

Узлы 6 1 тетрадного суммирования осу1Г1ествляют быстрое двоичное суммирование значений тетрад, сформи рованных на соответствунлцих тетрадных выходах блока 5 формирования частичных произведений. На тетрадном выходе каждого узла 6, -6, формируется тетрада суммы в однорядном двоичном коде, а на их выход переноса поступают все те переносы, которые образуются в данном узле 6 при суммировании в нем значений тетрад и которые имеют вес, превьпиающий вес суммируемых тетрад. Эти переносы могут быть как одноразрядными двоичными числами, так и многоразрядными. Последнее имеет место при использовании в узлах 6,-6j с целью увеличения их быстродействия многовходовых параллельных комбинационных счетчиков.

Узлы 7, -7/,|., суммирования тетрадных переносов предназначены для быстрого двоичного суммирования зна- чений переносов, сформированных на выходах переносов соответствуняцих узлов 6, (Тетрадного суммирования Они являются комбинационными суммирующими схемами.

Каждый узел 8 -Sj.,предназначен для быстрого преобразования его входного двоичного кода в выходной десятичный код. Входной двоичный код узл .,образован следующим образом: младшая его часть является тетрадой двоичной суммы соответствукщего узла

6тетрадного суммирования, старшая ж часть является двоичной суммой, сформированной на выходе соответствующег узла 7 суммирования тетрадных переносов. Узлы ,., могут быть реализованы как в виде однотактных комбинационных схем, так и на основе ПЗУ.

В последнем случае информацию в ПЗУ целесообразно хранить надлежащим образом либо в коде с избытком 3, либо в коде с из 1тком 6. Это позволяет исключить на входах блока 9 десятичного суммирования специальные кодопреобразователи, а следовательно и повысить его быстродействие;

В блоке 9 десятичного суммировани выполняется суммирование с учетом весов разрядов десятичных результато образованных на выходах узлов преобразования двоичного кода в де- сятичньй. В большинстве практических случаев этот блок должен обеспечивать быстрое десятичное суммирование либо двух,либо трех десятичных слагаемьк.

Коммутаторы 10, 0, первой группы осуществляют передачу информации на входы регистра 3 произведения или с выходов разрядов блока 9 десятичного суммирования (режим десятичного умножения), или с тетрадных выходов узлов 6 тетрадного суммирования (режим двоичного умножения). Каждый коммутатор 10,- lOjfT может быть реализован на четырех логических элементах 2И-2ИЛИ.

Коммутаторы второй группы предназначены для объединения в режиме двоичного умножения независимых узлов 6 jfn тетрадного суммирования в единый (цельный) блок двоичного суммирования, осуществляющий быстрое суммирование п двоичных частичных произведений и формирующий на своих выходах 2п-разрядный результат в однорядном двоичном коде. В этом блоке двоичного суммирования могут быть применены все самые совершенные методы и средства быстрого сворачивания fi -рядного двоичного кода в однорядный. Наличие коммутаторов путях передачи переносов от одних узлов 6 тетрадного суммирования к другим в большинстве случаев не снижает быстродействие блока двоичного суммирования, так как разрядные переносы его суммирующих элементов формируются, как правило, быстрее, чем разрядные суммы. В тех же случаях,когда это будет признано целесообразным, функции коммутаторов 11 -112 могут учтены при разработке соответствующих суммирующих элементов блока двоичного суммирования, не снижая их быстродействие. Коммутаторы 11 -llj, второй группы могут быть реализованы на основе двухвходовых элементов И.

Устройство при умножении в нем двоичных и десятичных чисел, работает следующим образом.

Б режиме двоичного умножения по сигналу на- входе 12 устройства блок 4 настраивается, на фop иpoвaниe двоичных кратных множимого, коммутаторы ll.-ll .второй группы обеспечивают объединение независимых узлов тетрадного суммирования в единьй блок двоичного суммирования, осуществляющий преобразовгшие -разряд- ного двоичного кода в однорядньй, а с помощью коммутаторов первой группы подготавливается передача результатов с тетрадных выходов узлов на информационные входы регистра 3 произведения. Далее одновременно или последовательно во времени в регистры 1 и- 2 загружаются ь-разрядные двоичные сомножители. После этого в блоке 4 формируются двоичные кратные множимого (двухкратное, четырехкратное и восьмикратное) которые совместно с множимым поступают соответствующим образом на входы блока 5, где образуется h двоич- ных частичных произведений. С помощь узлов , тетрадного суммирования объединеннык с помощью .коммутаторов 11 -11 , в торой группы в единый блок двоичного суммирования, осуще- ствляется быстрое суммирование п двоичных частичных произведений и образовавшаяся при этом 2и-разрядная двоичная сумма через коммутаторы 10 10,j первой группы записывается в регистр 3 произведения.

При умножении в устройстве десятичных чисел по сигналу на входе 12 режима устройства блок 4 настраивается на формирование десятичных крат- ных множимого, коммутаторы 11, 1 второй группы обеспечивают независимую (автономную) работу всех узлов 6,-62 тетрадного суммирования, а с помощью коммутаторов 10 чгг: первой группы подготавливается прием информации на входы регистра 3 произведения с выходов разрядов блока 9 десятичного суммирования.

Далее одновременно либо последо- вательно во времени в регистры 1 и 2 загружаются т -разрядные десятичные сомножители. После этого в блоке 4 формируются десятичные кратные множимого (двухкратное, четырехкратное и восьмикратное) а в блоке 5 образуется 4гг, десятичных частичных произведений. С помощью узлов 6 -6„ тет0 1 .-т

радного суммирования и соответствующих узлов 7, -7,-, с т-1мирования тетрадных переносов осуществляется автономное (локальное) двоичное суммирование равновесовых тетрад этих десятичных частичных произведений, а образовавшиеся при этом двоичг.ые результаты преобразуются на соответст- узлах 8,-8,,в десятичные, которые далее в блоке 9 преобразуются в однорядньй 2гг,-разрядный десятичный ре1ультат. Этот результат и запи:сывается в регистр 3 в к честве окончательного произведения.

Формула изобретения

Устройство для умножения, содержащее регистры множимого, множителя и произведения, блок формирования кратных множимого, блок формирования частичных произведений, узлы тетрадного суммирования, узлы преобразования двоичного кода в десятичный, блок десятичного суммирования и коммутаторы первой группы, причем выходы регистра множимого подключены к информационным входам блока формирования кратных множимого, вход управления режимом работы которого подключен к входу режима устройства, выходы регистра множителя и блока формирования кратных множимого подключены к входам блока формирования частичных произведений, тетрадные выходы которого подключены к входам соответству- ющизс узлов тетрадного суммирования, тетрадные выходы узлов тетрадного сумгдарования с первого по предпоследний подключены к входам младших разрядов соответствукнцих узлов преобразования двоичного кода в десятичный, тетрадный выход последнего узла тетрадного суммирования подключен к входу старшего разряда блока десятичного суммирования, тетрадные выходы узлов тетрадного суммирования подключены к первым информационным входам соответствуюищх коммутаторов первой группы, отличающее- с я тем, что, с целью повьшения быстродействия, в него введены узлы суммирования тетрадных переносов и коммутаторы второй группы, информационные входы которых соединены с выходами переносов соответствующих узлов тетрадного с 7Ф1ирования с первого по предпоследний и входами соответствующих узлов суммирования тетдадных пе-

реносов, выходы которых подключены к входам старших разрядов соответствующих узлов преобразования двоичного кода в десятичньй, выходы которых подключены в соответствии со значениями весов разрядов к входам соответствующих разрядов блока десятичного суммирования, выходы которых подключены к вторым информационным

входам соответствующих коммутаторов первой группы, выходы которых подключены к входам соответствующих разрядов регистра произведения, выходы коммутаторов второй группы подключены к входам последующих узлов тетрадного суммирования,управляющие входы коммутаторов первой и второй групп подключены к входу режима устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

Изобретение относится к вы4исли- тельной технике и может быть использовано при разработке быстродействующих устройств для умножения двоичных и десятичных чисел. Целью изобретения является расширение области применения устройства за счет возможности умножения на нем наряду с двоичными и десятичных чисел. Устройство содержит регистры множимого, множителя и результата, блок кратных, блок частичных произведений, блок двоичного суммирования, блок суммирования тетрадных переносов, блок преобразования двоичного кода в десятичный, блок десятичного суммирования и коммутатор. Цель достигнута за счет введения в устройство блока кратных, блока суммирования тетрадных переносов, блока преобразования двоичного кода в десятичный, блока десятичного суммирования и коммутатора. Причем выход регистра множимого соединен с входом блока кратных, выход которого соединен с вторым входом блока частичных произведений. Выходы тетрадных переносов блока двоичного суммирования соединены соответственно с входами блока суммирования тетрадных переносов, выходы которого соединены соответственно с первой группой входов блока преобразования двоичного кода в десятичный, вторая группа входов которого соединена соответственно с выходами тетрадных сумм блока двоичного суммирования. Выходы блока преобразования двоичного кода в десятичный соединены соответственно с входами блока десятичного суммирования. Выходы тетрадных блоков двоичного и десятичного суммирования соединены соответственно с первой и второй группами входов коммутатора, выход которого соединен с входом регистра результата, 1 ил. Ф §. ND Ю сл 00

i gji«tf%wi«- 1« i/gfl

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1982-12-24—Подача