(Л

VI

Ф

00

« ел

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения чисел, представленных в двоичной и десятичной системах счисления.

Цел-ь изобретения - сокращение аппаратурных затрат.

теме счисления не вызывает никакого труда. Для этого достаточно сдвинуть информацию на один двоичный разряд г влево. При использовании десятичной системы с применением кода может быть использована также процедура сдвига, как и при двоичной системе счисления, за исключением того, что

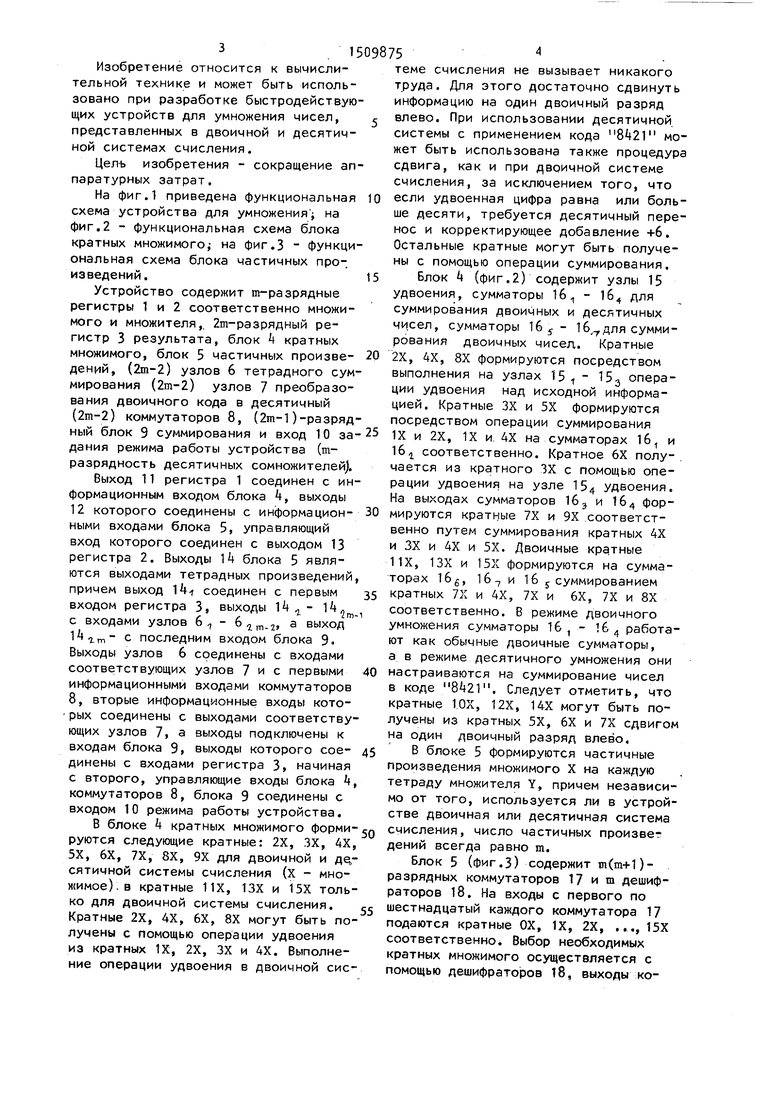

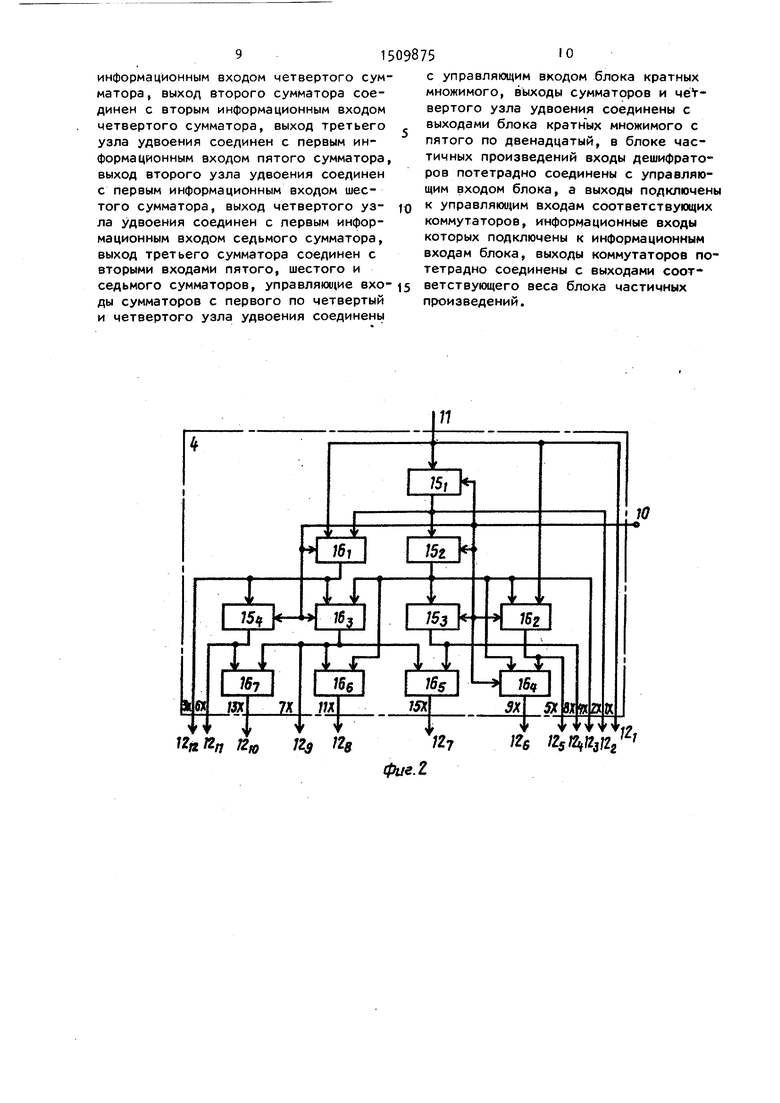

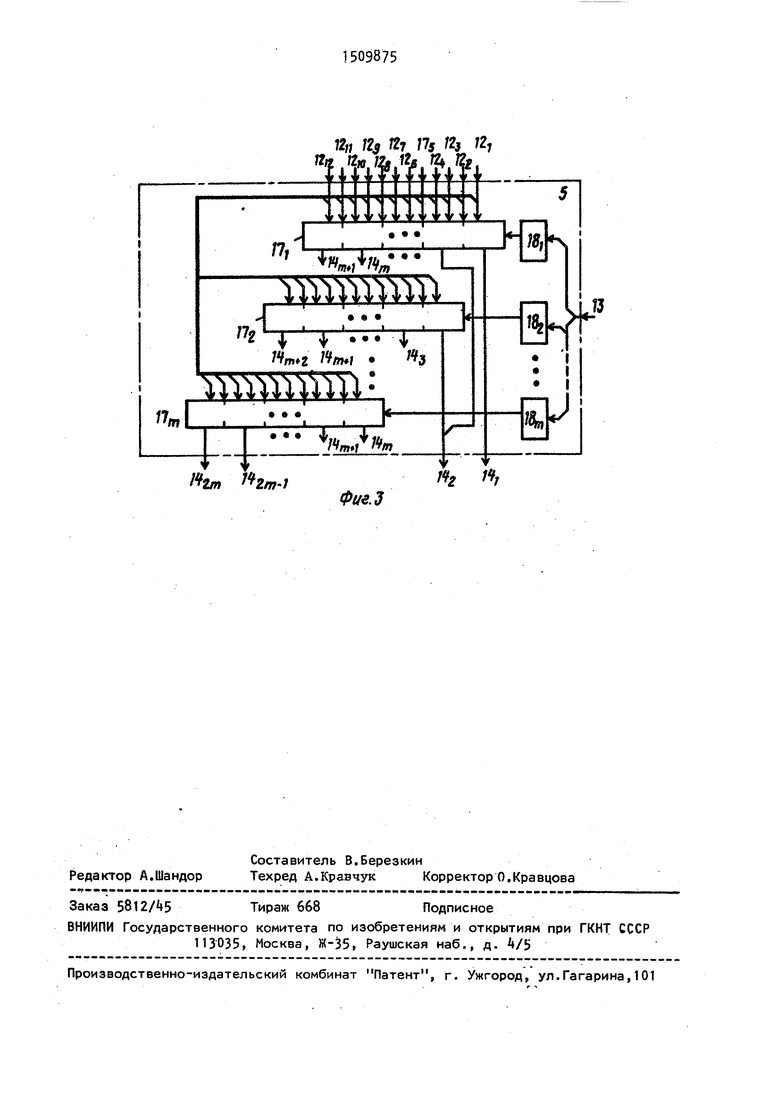

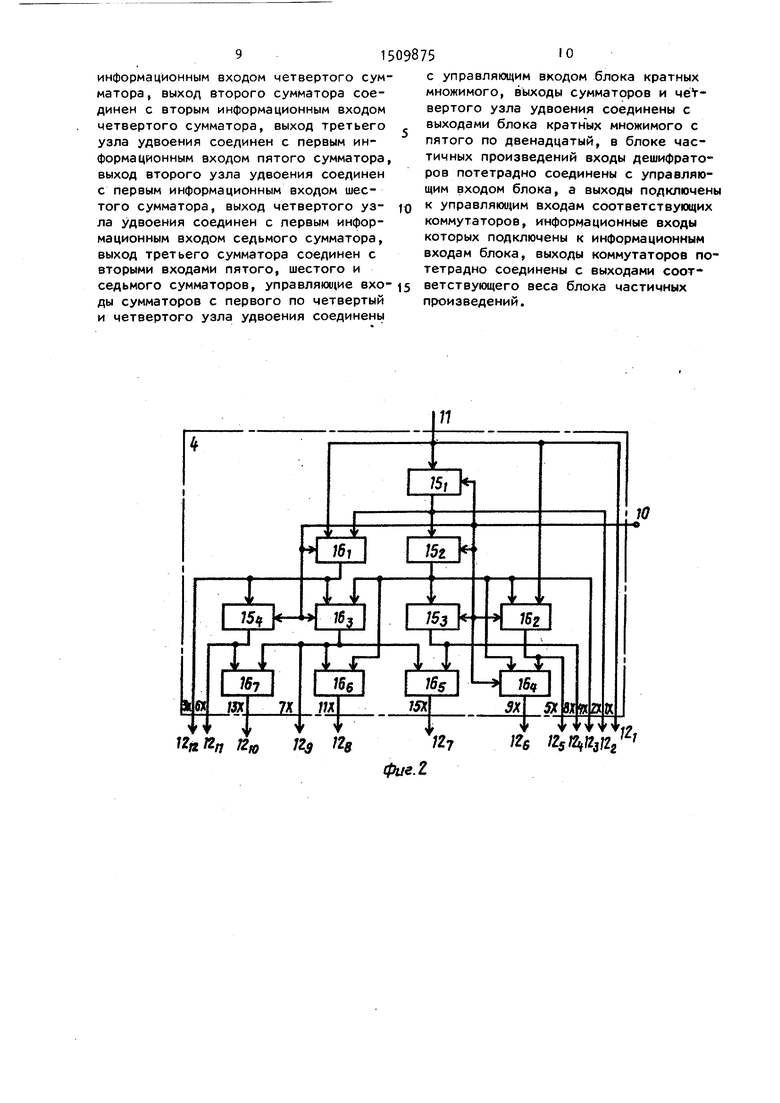

На фиг.1 приведена функциональная 10 если удвоенная цифра равна или боль- схема устройства для умножения на ше десяти, требуется десятичный пере- фиг.2 - функциональная схема блока нос и корректирующее добавление +6. кратных множимогоj на фиг.З функциональная схема блока частичных про-.

15

Остальные кратные могут быть получены с помощью операции суммирования. Блок 4 (фиг.2) содержит узлы 15 удвоения, сумматоры 16 - 164 для суммирования двоичных и десятичных чисел, сумматоры 16 j- 1б,для суммирования двоичных чисеп. Кратные

изведении.

Устройство содержит т-разрядные регистры 1 и 2 соответственно множимого и множителя,. 2т-разрядный регистр 3 результата, блок 4 кратных

множимого, блок 5 частичных произве- 20 2Х, 4Х, 8Х формируются посредством дений, (2т-2) узлов 6 тетрадного сум- выполнения на узлах 15 - 15з опера- мирования (2т-2) узлов 7 преобразования двоичного кода в десятичный (2т-2) коммутаторов 8, (2т-1)-разрядный блок 9 суммирования и вход 10 за-25 ix и 2Х, 1Х и АХ на сумматорах 1б и дания режима работы устройства (т- 1б соответственно. Кратное 6Х полу, разрядность десятичных сомножителей).

Выход 11 регистра 1 соединен с информационным входом блока , выходы

12 которого соединены с информацион- 30 мируются кратные 7Х и 9Х соответст- ными входами блока 5, управляющий венно путем суммирования кратных 4Х вход которого соединен с выходом 13 регистра 2. Выходы k блока 5 являются выходами тетрадных произведений,

причем выход I t-t соединен с первым 35 кратных 7Х и 4Х, 7Х и 6Х, 7Х и 8Х входом регистра 3, выходы 1 - 1.2m-i соответственно. В режиме двоичного

ции удвоения над исходной информацией. Кратные ЗХ и 5Х формируются посредством операции суммирования

чается из кратного ЗХ с помощью операции удвоения на узле 154 удвоения. На выходах сумматоров Тб и 164 фори ЗХ и 4Х и 5Х. Двоичные кратные 11Х, 13Х и t5X формируются на сумматорах I6g, 16-7 и 1б J суммированием

с входами узлов 6 - 6,.2 э выход последним входом блока 9. Выходы узлов 6 соединены с входами соответствующих узлов 7 и с первыми информационными входами коммутаторов 8, вторые информационные входы кото- рых соединены с выходами соответствующих узлов 7, а выходы подключены к входам блока 9, выходы которого сое- 45 динены с входами регистра 3, начиная с второго, управляющие входы блока , коммутаторов 8, блока 9 соединены с

умножения сумматоры 1б , - 164 работают как обычные двоичные сумматоры, а в режиме десятичного умножения они 40 настраиваются на суммирование чисел в коде . Следует отметить, что кратные 10Х, 12Х, 14Х могут быть получены из кратных 5Х, 6Х и 7Х сдвигом на один двоичный разряд влево.

В блоке 5 формируются частичные произведения множимого X на каждую тетраду множителя Y, причем независимо от того, используется ли в устройстве двоичная или десятичная система

В блоке 5 формируются частичные произведения множимого X на каждую тетраду множителя Y, причем независимо от того, используется ли в устрой стве двоичная или десятичная система

входом 10 режима работы устройства.

В блоке 4 кратных множимого форми- д счисления, число частичных произве- руются следующие кратные: 2Х, ЗХ, 4Х, дений всегда равно т. 5Х, 6Х, 7Х, 8Х, 9Х для двоичной и Блок 5 (фиг.З) содержит m(m+l)- сятичной системы счисления (Х - множимое), в кратные 11Х, 13Х и 15Х только для двоичной системы счисления. 5 шестнадцатый каждого коммутатора 17 Кратные 2Х, 4Х, 6Х, 8Х могут быть по- подаются кратные ОХ, IX, 2Х, ..., 15Х лучены с помощью операции удвоения из кратных IX, 2Х, ЗХ и 4Х. Выполнение операции удвоения в двоичной сисразрядных коммутаторов 17 и m дешифраторов 18. На входы с первого по

соответственно. Выбор необходимых кратных множимого осуществляется с помощью дешифраторов 18, выходы котеме счисления не вызывает никакого труда. Для этого достаточно сдвинуть информацию на один двоичный разряд влево. При использовании десятичной системы с применением кода моесли удвоенная цифра равна или боль- ше десяти, требуется десятичный пере- нос и корректирующее добавление +6.

Остальные кратные могут быть получены с помощью операции суммирования. Блок 4 (фиг.2) содержит узлы 15 удвоения, сумматоры 16 - 164 для суммирования двоичных и десятичных чисел, сумматоры 16 j- 1б,для суммирования двоичных чисеп. Кратные

2Х, 4Х, 8Х формируются посредством выполнения на узлах 15 - 15з опера- ix и 2Х, 1Х и АХ на сумматорах 1б и 1б соответственно. Кратное 6Х полуции удвоения над исходной информацией. Кратные ЗХ и 5Х формируются посредством операции суммирования

2Х, 4Х, 8Х формируются посредством выполнения на узлах 15 - 15з опера- ix и 2Х, 1Х и АХ на сумматорах 1б и 1б соответственно. Кратное 6Х полумируются кратные 7Х и 9Х соответст- венно путем суммирования кратных 4Х

чается из кратного ЗХ с помощью операции удвоения на узле 154 удвоения. На выходах сумматоров Тб и 164 формируются кратные 7Х и 9Х соответст- венно путем суммирования кратных 4Х

кратных 7Х и 4Х, 7Х и 6Х, 7Х и 8Х соответственно. В режиме двоичного

и ЗХ и 4Х и 5Х. Двоичные кратные 11Х, 13Х и t5X формируются на сумматорах I6g, 16-7 и 1б J суммированием

кратных 7Х и 4Х, 7Х и 6Х, 7Х и 8Х соответственно. В режиме двоичного

умножения сумматоры 1б , - 164 работают как обычные двоичные сумматоры, а в режиме десятичного умножения они настраиваются на суммирование чисел в коде . Следует отметить, что кратные 10Х, 12Х, 14Х могут быть получены из кратных 5Х, 6Х и 7Х сдвигом на один двоичный разряд влево.

В блоке 5 формируются частичные произведения множимого X на каждую тетраду множителя Y, причем независимо от того, используется ли в устройстве двоичная или десятичная система

счисления, число частичных произве- дений всегда равно т. Блок 5 (фиг.З) содержит m(m+l)- шестнадцатый каждого коммутатора 17 подаются кратные ОХ, IX, 2Х, ..., 15Х

разрядных коммутаторов 17 и m дешифраторов 18. На входы с первого по

счисления, число частичных произве- дений всегда равно т. Блок 5 (фиг.З) содержит m(m+l)- шестнадцатый каждого коммутатора 17 подаются кратные ОХ, IX, 2Х, ..., 15Х

соответственно. Выбор необходимых кратных множимого осуществляется с помощью дешифраторов 18, выходы ко

торых соединены с управляюицими входами коммутаторов 17. Выходы тетрад коммутаторов 17, имеющих один и тот же вес (десятичный или шестнадцате- ричный), образуют соответствующий выход значений тетрадных произведени блока 5 частичных произведений.

Функциональное назначение и реализация остальных узлов устройства.

Регистры 1 и 2 множимого и множителя предназначены для хранения га- разрядных десятичных сомножителей, В регистр 3 результата записывается 2т-разрядное (в режиме десятичного умножения) или 2п-разрядное (п т) произведение. Эти регистры могут быт построены, например, на двухтактных синхронных D-триггерах.

Узлы 6 - 6 тетрадного суммирования предназначены для быстрого суммирования по правилам двоичной арифметики тетрадных произведений, сформированных в соответствующей десятичной или шестнадцатеричной позиции блока 5 частичных произведений. Следует отметить, что максимальную сумму в L-й тетраде (предполагается, что младшая тетрада имеет первый порядковый номер, а старшая - 2т-й) дл десятичной системы счисления можно вычислить по формулам

С2т - L) X 9 + 8, для m : L i 2.m; Sio L X 9, для 1 i L m.

Аналогичные формулы могут быть по лучены и для двоичной системы счисления .

Узлы 7, - 7 „.., преобразования двоичного кода в десятичный предназначены для преобразования двоичного кода суммы, полученной на выходе соответствующего узла 6, - тетрадного суммирования, в двоично- десятичный код .

Коммутаторы 8 - режиме двоичного умножения осуществляют подключение к соответствующим входам блока 9 суммирования выходов узлов

61 ( г т-1 тетрадного суммирования,

а в режиме десятичного умножения вы

- в

2 гп-1

десятичный

преобразования

Блок 9 суммирования служит для суммирования тетрадных произведений двоичной или десятичной системы счисления (в зависимости от значения сигнала на входе 10). В большинстве практических случаев блок суммирова10

20

25

35

40

45 509875

ния представляет собой либо двухвхо- довый, либо трехвходовый быстродействующий сумматор для сложения двоичных и десятичных чисел.

При умножении двоичных и десятичных чисел устройство работает следующим образом.

В режиме умножения чисел, представленных в двоичной системе счисления, по сигналу на входе 10 устройства блок 4 настраивается на формирование двоичных кратных, блок 9 суммирования настраивается на суммирование 5 двоичных чисел, а выходы коммутаторов 8 соединяются со своими первыми входами, на которые поступают результаты с выходов соответствующих узлов 6. - 6

30

50

55

1 тетрадного суммирования. Далее одновременно или последовательно во времени в регистры 1 и 2 загружаются п-разрядные (п km) двоичные сомножители X и Y без знаков. После этого в блоке k кратных формируются кратные 2Х, ЗХ, 4Х, 5Х, 6Х, 7Х, 8Х, 9Х, 11Х, 13Х, 15Х, которые поступают соответствующим образом на входы блока 5, где образуется m частичных произведений множимого X на множитель Y (при умножении множимого X на одну тетраду множителя Y образуется одно частичное произведение). Тетрадные произведения, являющиеся составной частью частичных произведений, поступают на выходы - 14 блока 5 с учетом занимаемой ими в блоке весовой шестнадцатиричной позиции, причем значение тетрадного произведения сформированного в первой шестнадцатиричной позиции и подаваемого на выход 14 блока 5 частичных произведений, непосредственно поступает на входы младшей тетрады регистра 3 результата. В узлах 6 - 6 тетрадного суммирования выполняется быстрое двоичное суммирование равновесных тетрадных произведений, поступающих на входы этих узлов соответствующих выходов блока 5 частичных произведений, а получившиеся на их выходах результаты поступают через соответствующие коммутаторы ,. на равновесовые. входы блока 9 суммирования. Образованный на выходе блока 9 суммирования результат записывается в регистр 3 результата.

В режиме умножения десятичных чисел по сигналу на входе 10 устройства блок 4 настраивается на формирование десятичных кратных, блок 9 суммирования настраивается на суммирование десятичных чисел, а выходы коммутаторов 8 - 8 .соединяются со своими вторыми входами, на которые подаются результаты с выходов соответствующих узлов 7 lin-г преобразования двоичного кода в десятичный..

Далее одновременно или последовательно во времени в регистры 1 и 2 загружаются т-разрядные десятичные сомножители X в Y без знаков. После этого в блоке формируются кратные 2Х, ЗХ, 4Х, 5Х, 6Х, 7Х, 8Х, 9Х, кото- рые поступают соответствующим образом на входы блока Зу где образуется m частичных произведений множимого X на множитель Y. Далее в узлах 6 - 7т--г тетрадного суммирования выполняется быстрое двоичное суммирование равновесных тетрадных произведений, поступающих на входы - этих узлов с соответствующих выходов ., блока 5 частичных произведений, а получившиеся на их выходах двоичные результаты поступают на входы соответствующих узлов 7т - 1 .-1,, где производится их преобразование в д сятич- ный код . Десятичные числа с выходов узлов 7т - 7гт-г подаются через коммутаторы В - 8 гр, на равновесные входы блока 9 суммирования. Образованный на выходе блока Э сумми- рования результат записывается в регистр 3 результата.

Формула изобретения

Устройство для умножения, содержащее регистры множимого, множителя и результата, блок кратных множимого, блок частичных произведений, узлы тетрадного суммирования, узлы преоб- разования двоичного кода в десятичный, коммутаторы и блок суммирования причем выход регистра множителя соединен с управляющим входом блока частичных произведений, все выходы которого, кроме первого и последнего, со единены с входами узлов тетрадного суммирования, выходы которых, соединены с входами соответствующих узлов преобразования двоичного кода в десятичный и с первыми информационными входами соответствующих коммутаторов вторые входы которых соединены с выходами соответствующих узлов преобразования двоичного кода в десятичный, выходы коммутаторов соединены с соответствующими информационными входами блока суммирования, выходы которого соединены с входами тетрад регистра результата, начиная с второй, управляющие входы блока кратных множимого, коммутаторов и блока суммирования соединены с входом режима работы устройства, выход регистра множимого соединен с информационным входом блока кратных множимого, выходь которого соединены с информационными входами блока частичных произведений, при этом блок кратных множимого содержит три узла удвоения, информационный вход первого узла удвоения соединен с информационным входом и первым выходом блока кратных множимого, выход первого узла удвоения соединен с вторым выходом блока кратных множимого и информационным входом второго узла удвоения, выход которого соединен с третьим выходом блока кратных множимого и с информационным входом третьего узла удвоения, выход которого соединен с четвертым выходом блока кратных множимого, управляющие входы первого, второго и третьего узлов удвоения соединены с управляющим входом блока кратных множимого, о т - личающеес я тем, что, с целью сокращения аппаратурных затрат, первый выход блока частичных произведений соединен с входом первой тетрады регистра произведения, последний выход блока частичных произведений соединен с соответствующим информационным входом блока суммирования, в блок кратных множимого введены четвертый узел удвоения и семь сумматоров, а блок частичных произведений содержит дешифраторы в коммутаторы, причем в блоке кратных множимого первые информационные входы первого и второго сумматоров соединены с информационным входом первого узла удвоения, второй информационный вход первого сумматора соединен с информационным входом второго узла удвоения, аыход первого сумматора соединен с информационным входом четвертого узла удвоения и с первым информационным входом третьего сумматора, второй информационный вход которого соединен с информационным входом третьего узла удвоения, с вторым информационным входом второго сумматора и с первым

9 1

информационным входом четвертого сум матора, выход второго сумматора соединен с вторым информационным входом четвертого сумматора, выход третьего узла удвоения соединен с первым информационным входом пятого сумматора выход второго узла удвоения соединен с первым информационным входом шестого сумматора, выход четвертого узла удвоения соединен с первым информационным входом седьмого сумматора, выход третьего сумматора соединен с вторыми входами пятого, шестого и седьмого сумматоров, управляюи4ие вхо ды сумматоров с первого по четвертый и четвертого узла удвоения соединены

09875 О

с управляющим вкодом блока кратных множимого, выходы сумматоров и четвертого узла удвоения соединены с выходами блока кратных множимого с пятого по двенадцатый, в блоке частичных произведений входы дешифраторов потетрадно соединены с управляющим входом блока, а выходы подключены to Управлящим входам соответствующих коммутаторов, информационные входы которых подключены к информационным входам блока, выходы коммутаторов потетрадно соединены с выходами соот15 ветствующего веса блока частичных произведений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1982 |

|

SU1157542A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств для умножения чисел, представленных в двоичный и десятичной системах счисления. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит регистры 1-3 множимого, множителя и результата, блок 4 кратных множимого, блок 5 частичных произведений, узлы 6 тетрадного суммирования, узлы 7 преобразования двоичного кода в десятичный, коммутаторы 8, блок 9 суммирования, вход 10 задания режима работы. 3 ил.

12aJ2fj Kfo Пз Ч 7

фиг.г

}Z6

12п Пз Itf Пз Пз I2j

f Zm-J г ffr

Фие,3

| Способ раскроя ткани для швейных изделий | 1956 |

|

SU105310A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-09-23—Публикация

1987-09-07—Подача