Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

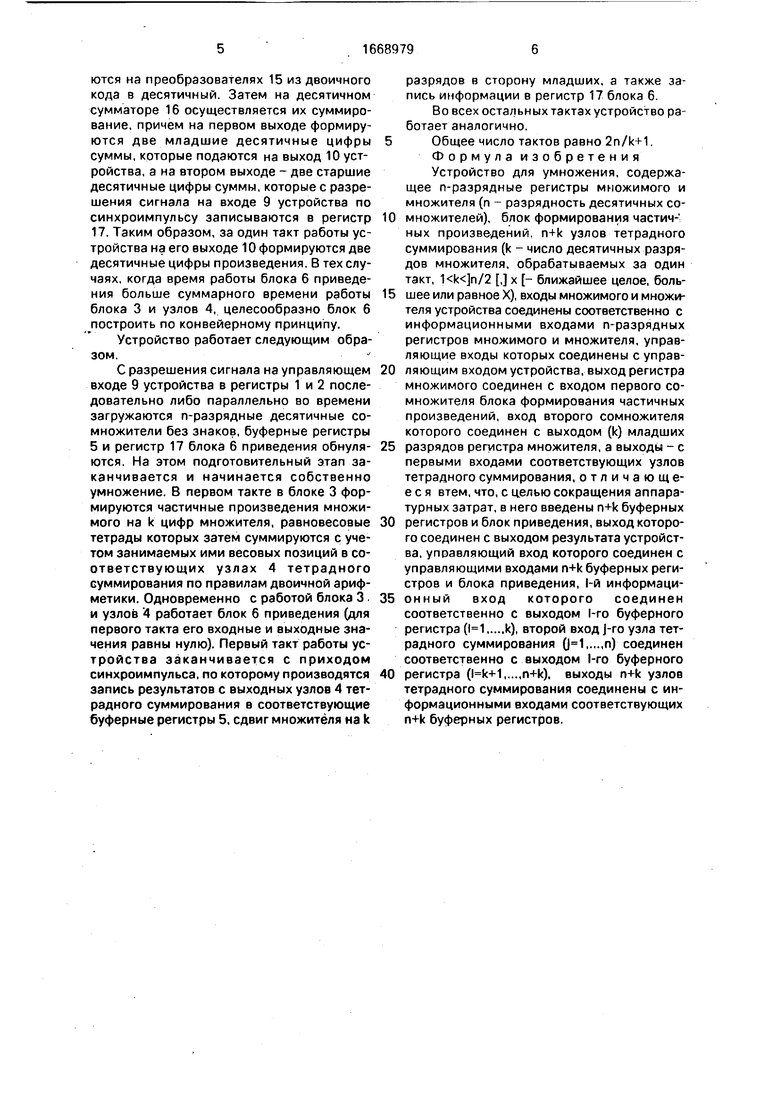

Изобретение относится к вычислительной технике и может быть использовано для быстрого умножения десятичных чисел. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит регистры множимого 1, множителя 2, узлы 4 тетрадного суммирования, блок 3 частичных произведений, буферные регистры 5 и блок 6 приведения. 3 ил.

ю

( О 00 Ю VI Ю

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения десятичных чисел, а также служить основой построения универсальных устройств умножения двоичных и десятичных чисел.

Целью изобретения является сокращение аппаратурных затрат.

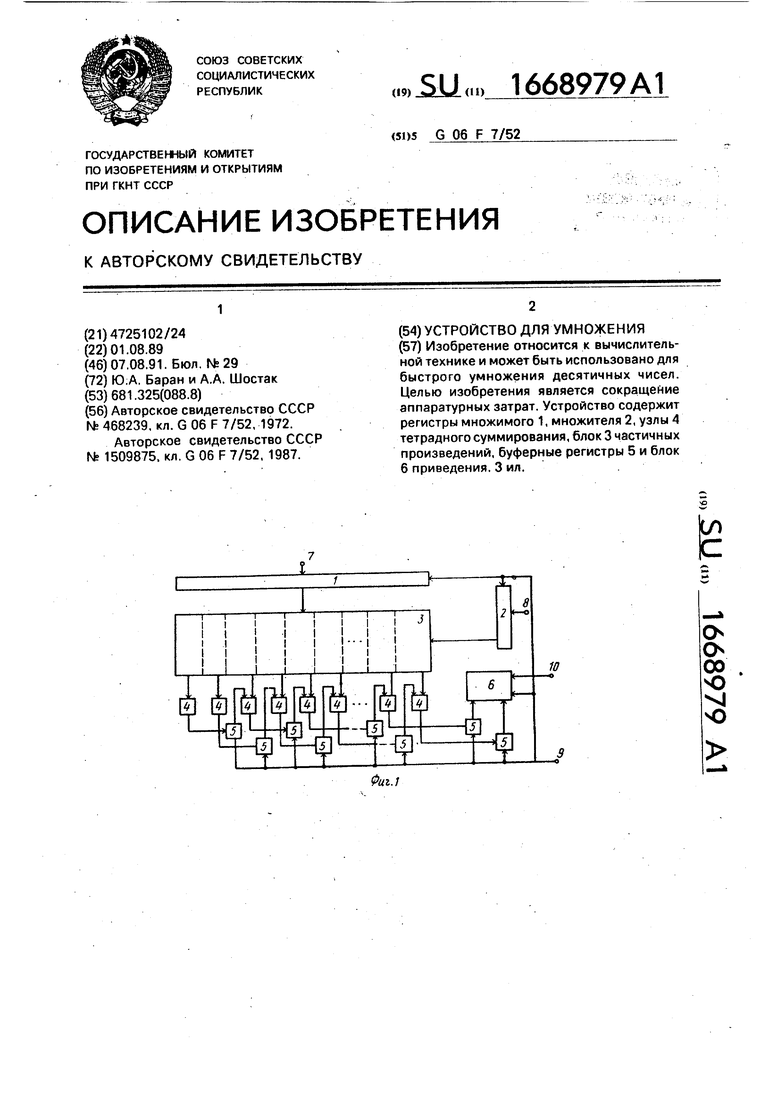

На фиг. 1 приведена структурная схема устройства (для ); на фиг. 2 - два возможных варианта построения блока формирования частичных произведений; на фиг. 3 - структурная схема блока приведения.

Устройство содержит регистры 1 и 2 множимого и множителя соответственно, блок 3 формирования частичных произведений, узлы А тетрадного суммирования, буферные регистры 5, блок 6 приведения, входы 7 и 8 множимого и множителя устройства соответственно, управляющий вход 9 устройства и выход 10 результата.

Функциональное назначение и реализация узлов и блоков устройства следующие.

Регистр 1 множимого предназначен для хранения множимого. Цепи синхронизации всех регистров устройства с целью упрощения не показаны. Входы синхронизации всех элементов памяти регистров объединены и соединены с входом синхронизации устройства.

Регистр 2 множителя предназначен для хранения множителя. В процессе выполнения умножения в нем осуществляется одно- тактный сдвиг множителя на k разрядов в каждом такте.

Блок 3 служит для формирования частичных произведений множимого на k разрядов множителя. На фиг. 2 показаны два возможных варианта построения этого блока. Первый вариант (фиг. 2,а) содержит узел 11 кратных множимого и узел 12 частичных произведений. В узле 11 формируются или кратные множимого 1Х, 2Х, 4Х и 8Х или кратные 1Х, 1Х, ЗХ8Х, 9Х, где X - множимое. Узел 12 может быть реализован в виде матрицы двухвходовых элементов И либо представлять собой k коммутаторов.

На фиг. 2,6 для k-2 приведена структурная схема второго варианта блока 3 формирования частичных произведений, содержащего усеченную матрицу узлов 13 десятичного умножения. Каждый узел 13 предназначен для перемножения двух десятичных цифр и может быть построен, например, на постоянном запоминающем устройстве, на шифраторе или в виде композиции двоичного.умножителя и преобразователя двоичного кода ч десятичный.

Узлы 4 тетрадного суммирования являются узлами комбинационного типа. В каждом такте работы устройства в этих узлах осуществляется двоичное суммирование

равновесных частичных произведений, сформированных в данном такте на выходах блока 3,; и прибавление к полученному результату содержимого соответствующего буферного регистра 5, сформированного в

0 предыдущем такте работы устройства. Узлы 4 тетрадного суммирования могут формировать результат как в однорядном, так и в многорядном коде.

Буферные регистры 5 служат для хране5 ния результатов, формируемых в каждом такте на выходах соответствующих узлов 4 тетрадного суммирования.

Блок 6 предназначен для приведения результата, записываемого в каждом такте

0 в k младших буферных регистрах 5, в однорядный двоично-десятичный код. На фиг. 3 приведена структурная схема блока 6 при следующих допущениях: , узлы 4 формируют на своих выходах результат в одноряд5 ном коде, в блоке 6 в каждом такте формируется не более 2k десятичных цифр результата, k младших цифр которого являются очередными k цифрами произведения сомножителей. Блок 6 содержит два двоич0 ных сумматора 14, два преобразователя 15 двоичного кода в десятичный, десятичный сумматор 16 и регистр 17.

Двоичный сумматор 14 в каждом такте работы устройства осуществляется сумми5 рование содержимого соответствующего буферного регистра 5 со значением соответствующей тетрады регистра 17, сформированным в предыдущем такте работы устройства.

0Преобразователь 15 предназначен для

преобразования результата, полученного на выходе двоичного сумматора 14, из двоичного кода в двоично-десятичный. Десятичный сумматор 16 предназначен для

5 суммирования результатов, полученных на выходах преобразователей 15, в двоично- десятичном коде. Регистр 17 предназначен для хранения двух старших десятичных цифр результата, сформированного на вы0 ходе десятичного сумматора 16.

Блок 6 приведения работает следующим образом.

На входы блока 6 с выходов первого и второго буферных регистров 5 подаются два

5 результата в двоичном коде. Далее на первом и втором двоичных сумматорах 14 осуществляется их суммирование со значениями младшей и старшей тетрад регистра 17 соответственно. Полученные на выходах сумматоров 14 суммы преобразуются на преобразователях 15 из двоичного кода в десятичный. Затем на десятичном сумматоре 16 осуществляется их суммирование, причем на первом выходе формируются две младшие десятичные цифры суммы, которые подаются на выход 10 устройства, а на втором выходе - две старшие десятичные цифры суммы, которые с разрешения сигнала на входе 9 устройства по синхроимпульсу записываются в регистр 17. Таким образом, за один такт работы устройства на его выходе 10 формируются две десятичные цифры произведения. В тех случаях, когда время работы блока 6 приведения больше суммарного времени работы блока 3 и узлов 4, целесообразно блок 6 построить по конвейерному принципу.

Устройство работает следующим образом.

С разрешения сигнала на управляющем входе 9 устройства в регистры 1 и 2 последовательно либо параллельно во времени загружаются n-разрядные десятичные сомножители без знаков, буферные регистры 5 и регистр 17 блока 6 приведения обнуляются. На этом подготовительный этап заканчивается и начинается собственно умножение. В первом такте в блоке 3 формируются частичные произведения множимого на k цифр множителя, равновесовые тетрады которых затем суммируются с учетом занимаемых ими весовых позиций в соответствующих узлах 4 тетрадного суммирования по правилам двоичной арифметики. Одновременно с работой блока 3 и узлов 4 работает блок 6 приведения (для первого такта его входные и выходные значения равны нулю). Первый такт работы устройства заканчивается с приходом синхроимпульса, по которому производятся запись результатов с выходных узлов 4 тетрадного суммирования в соответствующие буферные регистры 5. сдвиг множителя на k

разрядов в сторону младших, а также запись информации в регистр 17 блока 6.

Во всех остальных тактах устройство ра ботает аналогично.

Общее число тактов равно 2n/k И.

Формула изобретения Устройство для умножения, содержащее n-разрядные регистры множимого и множителя (п - разрядность десятичных сомножителей), блок формирования частич- ных произведений, n+k узлов тетрадного суммирования (k - число десятичных разрядов множителя, обрабатываемых за один такт, , х - ближайшее целое, большее или равное X), входы множимого и множителя устройства соединены соответственно с информационными входами поразрядных регистров множимого и множителя, управляющие входы которых соединены с управляющим входом устройства, выход регистра множимого соединен с входом первого сомножителя блока формирования частичных произведений, вход второго сомножителя которого соединен с выходом (k) младших

разрядов регистра множителя, а выходы - с первыми входами соответствующих узлов тетрадного суммирования, отличающееся втем, что, с целью сокращения аппаратурных затрат, в него введены n+k буферных

регистров и блок приведения, выход которого соединен с выходом результата устройства, управляющий вход которого соединен с управляющими входами n+k буферных регистров и блока приведения, 1-й информационный вход которого соединен соответственно с выходом 1-го буферного регистра (), второй вход j-ro узла тетрадного суммирования () соединен

соответственно с выходом 1-го буферного

регистра (l k+1n+k), выходы n+k узлов

тетрадного суммирования соединены с информационными входами соответствующих n+k буферных регистров.

I I I

I

--Н-Г-НJ-г

I I

I I I 12

| Десятичное множительное устройство | 1972 |

|

SU468239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-07—Публикация

1989-08-01—Подача