Изобретение относится к запоминающим устройствам и может быть использовано в различных системах унравлемия, в которых запоминающие устройства с сохранением информации нри отключении питания используются в качестве ностоянных )минаю1цих устройств, т. е. в которых Т()ебуется падежное сохранение накоплеиной информации в режиме считывания и хранения.

Известно запоминающее устройство с coxpaiieiuieM информации при отключении ннтания, содержащее накопитель, блок сонряження, резервный источник питания,, разделительные элементы 1.

Однако извеетное устройство не обеспечивает падежное сохранение накопленной информацни в момент включения и отключения основного источника питания.

Наиболее близким к предлагаемому является запоминаюп1ее устройство с резервным источником гпггания, содержащее матрицу памяти, вход питания которой нодк.почен к резервному источнику питания неносредствен-но и к вводу основного источника питания -- через диод, блок соиряЖе1П1я, через адресные и информационные входы и информационные выходы матрицы па.мяти подключены к соответствующим щинам устройства, детектор падения напряжения, вход которого подключен к вводу основного источника нитапия, нереключатели, выходы которых подключены соответственно к входам блокировки и считывания записи матрицы памяти, а нервые коммутируемые входы - к резервному источнику питания, при этом второй коммутируемый вход второго переключателя через блок сопряжения подключен к первой управляющей щипе устройства 2.

Недостаток этого устройства заключается в том, что при включении основного источника питания не обеспечивается на-, дежное сохранение накопленной информации, так как разблокировка наконителя происходит при достижении напряжения па выходе основного источника питания порогового уровня (который заведомо ниже номипальпого), а переходные процессы в схеме, как правило, еще некоторое время имеют место. Кроме того, в данном устройстве невоз.можно использовать накопитель, ностроепный на интегральных нолупроводниковых запоминающих элементах КМДПструктур, так как для них необходимо соблюдать определенную последовательность включения входных сигналов и недопустимо постоянное нрисутствие разрешаюпхего сигнала на входе блокировки накопителя.

Цель изобретения - новышепие надежности устройства.

Иоставле1И1ая цель достигается те.м, что в заиоминающее устройство с сохранение.м информации при отключении питания, содержащее наконитель, элемент развязки,

пороговый элемент, переключатели и резервный источник нитання, выход которого подключен ко входу питания накопителя, первым входам переключателей и одному из выводов элемента развязки, другой вывод которого соединен с выходом основного источника питания и входом порогового элемента, выходы первого и второго переключателей соединены соответственно со входом блокировки и со входом считывания/записи накопителя, второй вход второго переключателя является первым управляюиа.и.м входом устройства, адресный и информационный входь 1 и выход накопителя являются соответственно адресным и информационным входами и информационным выходом устройствам, введены элемент задержки и

элемент И, причем вход элемента задержки

подключен к выходу норогового элемента

и к первому входу элемента И, второй вход

которого подключен к выходу элемента

задержки, выход элемента И нодключен к

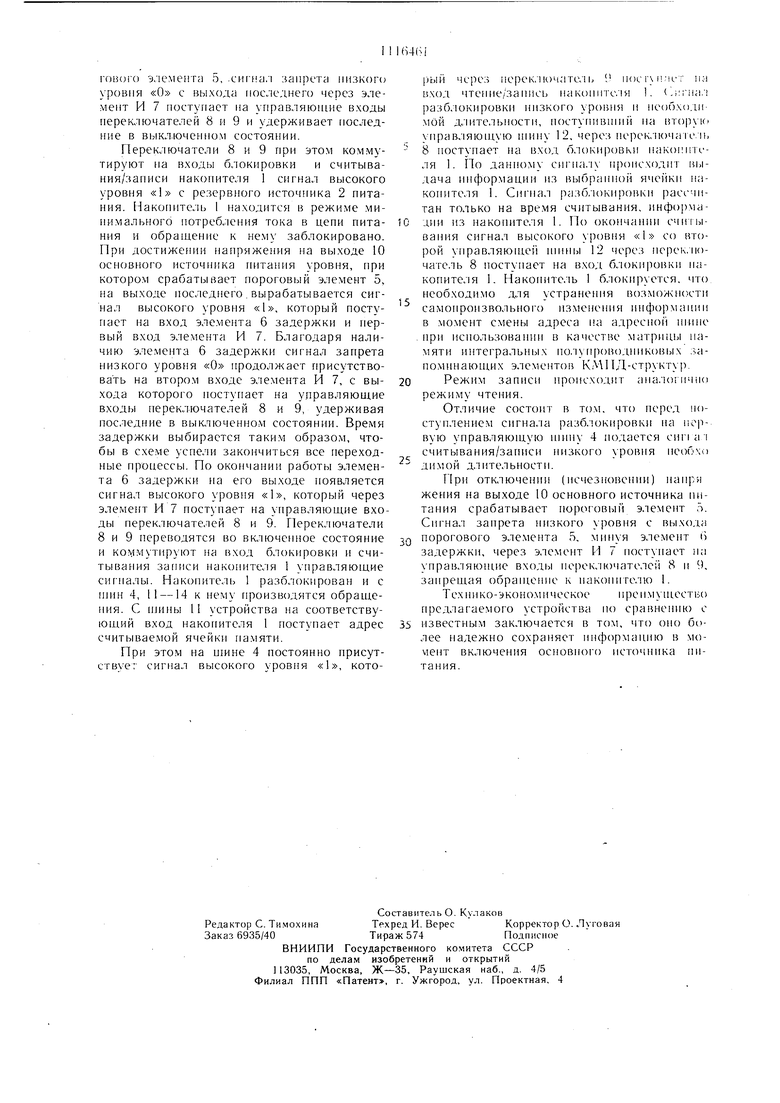

управляющим входам переключателей, второй вход первого переключателя является вторы.м управляющим входом устройства. На чертеже приведепа схема предлагаемого устройства.

Схема содержит накопитель 1, резервный источник 2 питания, элемент 3 развязки, первую унравляюн1.ую щи}(у 4, пороговый элемент 5, элемент 6 задержки, эле.мент И 7, первый 8 и второй 9 переключатели, выход 10 основного источника питания, адресную 11, вторую управляющую 12, входную 13 и выходную 14 информационные шины устройства. Выход резервного источника 2 питания подключен к входу питания накопителя 1, первым входам первого 8 и второго 9 переключателей и одному из выводов элемента 3 развязки, другой вывод которого соединен с выходом 10 основного источника питания и входом порогового элемента 5, выход которого подключеп ко входу элемента 6 задержки и к первому входу элемента И 7. Выход элемента 6 задержки подключается ко второму входу эле.мента И 7, выход которого подключен к управляющим входам первого 8 и второго 9 переключателей. Выходы первого 8 и второго 9 переключателей соединены соответственно

со входом блокировки и со входом считывапия/зап1 си накопителя 1.

Устройство работает следующим образом.

Пороговый элемент 5 содержит стабилитрон, напряжение стабилизации которого определяет уровень срабатывания порогового элемента.

Если наиряжение основного источника питания ниже уровня срабатывания порогового э.юмента о, .cunia.i запрета низкого уровня «О с выхода последнего через элемент И 7 поступает на управляюпше входы переключателей 8 и 9 н удерживает ноеледнпе в выкл.ючепном состоянип. Переключатели 8 и 9 при этом коммутируют на входы блокировки и счптывания/занпси пакопителя 1 сигнал высокого уровня «1 с резервного источника 2 питаппя. Накопитель I находится в режиме минимального потребления тока в цепи питания и обращение к нему заблокировано. При достижении напряжения на выходе 10 основного источника гп1танпя уровня, нри котором срабатывает пороговый элемент 5, на выходе последнего , вырабатывается сигпал высокого уровня «1, который поступает на вход элемента 6 задержки и первый вход элемента И 7. Благодаря наличию элемепта б задержки сигнал запрета низкого уровня «О нродолжает присутствовать на втором входе элемента И 7, с выхода которого поступает на управляющие входы переключателей 8 и 9, удерживая последппе в выключенном состоянии. Время задержки выбпрается таким образом, чтобы в схеме успели закончиться все переходные процессы. По окончании работы элемента 6 задержки па его выходе появляется сигнал высокого уровня «1, который через элемент И 7 поступает па управляющие входы переключателей 8 и 9. Переключатели 8 и 9 переводятся во включенное состояние и коммутируют на вход блокировки и считывания записи пакопителя 1 управляющие сигпалы. Накопитель 1 разблокирован и с ипн 4, 11 -14 к нему производятся обращения. С ИП1ПЫ 11 устройства на соответствующий вход накопителя 1 поступает адрес считываемой ячейки памяти. При этом на тине 4 постоянно присутствуег сигнал высокого уровня «1, который через нереключатель ; посгх име г на ()д чтенне/за1П1С1) паконнтс.чя 1. t.nina.i разблокировки низкого уровня и необходи мой длител1 ности, поступивнщй на (ггорук) унравляюнлую П1ину 12, через перек.початель 8 поступает па вход блокировки пакошпеля 1. По данному cnnia.iy п|)опсходпт libiдача ипформацин из В1)1браппс)й яче{|К11 накопителя 1. Сигнал разб,1окнро кп рассчптап только на время считывания, информални из нако1П1теля 1. По окончанни счигывания сигнал высокого уровня «1 со второй унравляюпгей ninm.i 12 через нереключатель 8 ностунает на вход блокировки n;iконителя 1. Пакоиите.чь 1 блокируется, что пеобходимо для устранепия возможности самопропзвольпого пзмепепия ни форм а пи и в момент смены адреса на адресной П1ипе прп пспользова1П1п в качестве матрпцы памяти интегральпых полупроводниковых запоминающих элементов КМПД-структур. Режим заппси происходит ана.югнчпо режиму чтения. Отличие состоит в том. что перед посту пленпем cnrna.ia разб.юкировки па первую унравляюпхую ninny 4 подается сигип считывания/записи пизкого уровпя iiet) zin м ой длптел ьпости. При отключении (псчезновеппи) папри жения на вы.ходе 10 основного источника питания срабатывает пороговый элемент 5. Спгнал запрета ппзкого уровпя с выхода порогового элемента о, минуя элемент п задержки, через элемепт И 7 поступает на управляюн1ие входы переключателей 8 и 9, заирещая обращение к наконптелю I. Техпико-эконо.п1ческое нре имущество предлагаемого устройства по сравненпю с известпым заключается в том, что опо более надежно сохраняет пнформаппю в моvieHT включения основного нсточппка питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU842975A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1982 |

|

SU1083236A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1408458A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1615809A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1990 |

|

SU1716573A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1988 |

|

SU1508286A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU807388A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОПЕРАТИВНОЙ ПАМЯТЬЮ С СОХРАНЕНИЕМ ДАННЫХ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ | 1986 |

|

RU1385875C |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С СОХРАНЕНИЕМ ИНФОРМАЦИИ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ, содержащее накопитель, элемент развязки, пороговый элемент, переключатели и резервный источник питания, выход которого подключен ко входу питапия накопителя, первым входам переключателей и одному из выводов элемента развязки, другой вывод которого соединен с выходом основного источника питания и входом порогового э.чсмента, выходы первого и второго переключателей соединепы соответствепно со входом блокировки и со входом считывания/записи накопителя, второй вход второго переключателя является первым управляющим входом устройства, адресный и пнформационпьп входы и выход накопителя являются соответственно адресным п информационным входами п информационным выходом устройства, отличающееся тем, что, с целью повыщения надежности устройства, оно содержит элемент задержки и элемент И, причем вход элемепта задержки подключен к выходу порогового элемента и к первому входу элемента И, второй вход которого подключен к выходу элемента ш (Л задержки, выход элемента И подключен к управляющим входам переключателей, второй вход первого переключателя является вторым управляющи.ч входом устройства. WoО5 4 О)

Авторы

Даты

1984-09-30—Публикация

1983-05-19—Подача