4iib

Х

4i СЛ

00

ue.f

1

Изобретение относится к запоминающим устройствам и предназначено дли надежного хранения информации в цифровых вычислительных системах, в частности в системах с резервированием.

Целью изобретения является повышние надежности устройства.

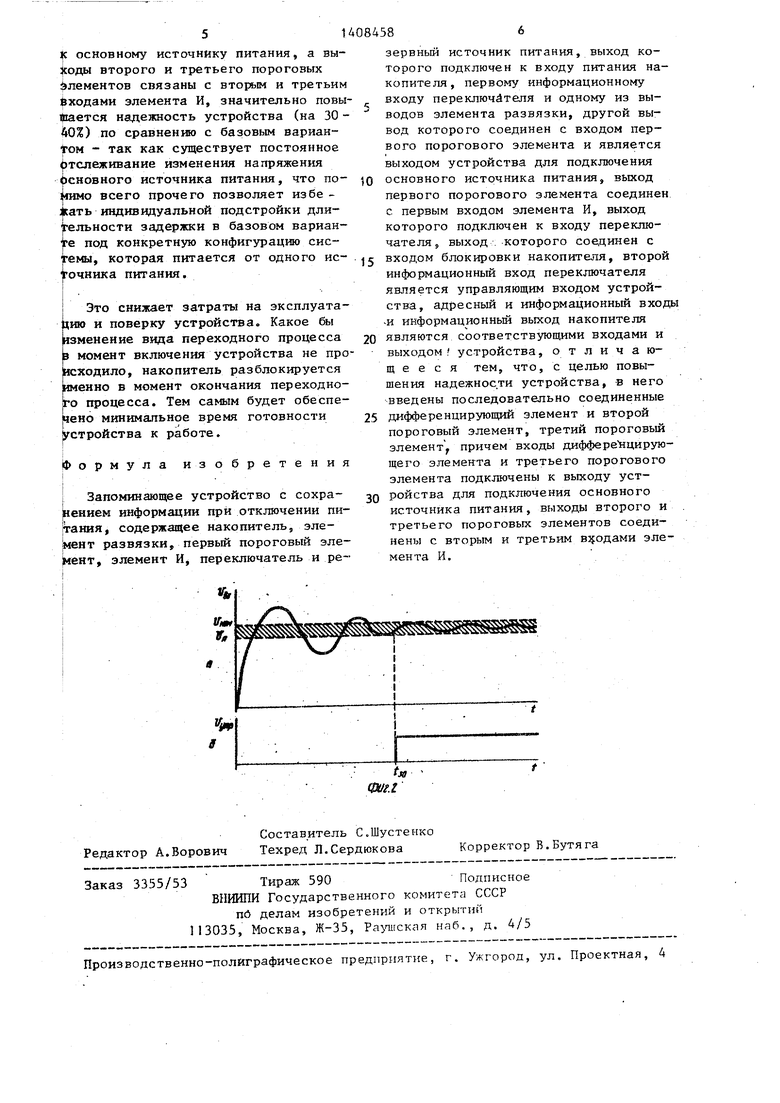

На фиг.1 приведена структурная схема устройства; на фиг.2 - зависимости от времени: а) напряжения основного источника питания; б) сигнала разблокировки накопителя (приложенного к управляющим входам переключателей) предлагаемого устроства .

Предлагаемое устройство содержит накопитеш 1, вход блокировки которого подключен к выходу перекхвоча- теля 2,связанному своим первым информационным входом с резервным источником 3 питания, подключенным, кроме того, к питающему входу накоптеля. Второй информационный вход пе реключатепя 2 соединен с управляющи входом 4 устройства, а адресный вхо 5f информационньй вход 6 и информационный выход 7 накопителя являются адресным, информационным входами и информационным выходом устройства. Элемент 8 развязки одним выводом поключен к резервному источнику питания, а другим - к .выходу устройства для подключения основного источника 9 питания и к входам дифференцирующего элемента 10, первого и третьего пороговых элементов 11 и 12. Выход Д1)фе ренцирующего элемента связан с входом второго порогового элемента 13), а выходы всех трех пороговых элементов соединены с входами элемента И 14, нагруженного на упраляющий вход переключателя

Предлагаемое устройство работает следующим образом.

Пороговые элементы 11-13 сравнивают напряжения, подаваемые на их входы, с опорными уровнями напряжения задваемыми при настройке системы. Если входное напряжение меньше опорного уровня, то на выходе порогового элемента .11 поддерживается низкий уровень напряжения О, а пр превышении входным напряжением опорного выход порогового элемента 11 устанавливается в состояние с высоким уровнем напряжения 1. Если входное напряжение пороговых элемен

0

5

0 5 О

тов 12 и 13 меньше опорных уровней, то на выходе i-cc поддерживается уровень 1, а если больше - то уровень О.

В автоматическом режиме, когда отсутствует напряжение основного источника 9, выходы пороговых элементов 11-13 находятся в состоянии низкого уровня О, и, следовательно, на выходе элемента И поддерживается состояние О. Переключатель 2 при таком состоянии управляющих входов коммутирует на управляющий вход накопителя 1 сигнал высокого уровня с резервного источника 3 питания. Происходит хранение записанной в накопителе информации, причем обращение к накопителю заблокировано.

При переключении на основной источник 9 напряжение последнего Ug в силу инерционности нагрузки постепенно нарастает, причем нарастание в общем случае носит колебательный характер (фиг.2а). При доо,тиже- нии напряжением на выходе основного источника 9 уровня U, при котором срабатывает первый пороговый элемент 11, на выходе последнего вырабатывается сигнал высокого уровня 1, который поступает на третий вход элемента И 14. При этом имеет место условие

п Uboc. ,

(1)

условия

где и„„„ - номинальное напряжение

НОМ

основного источника питания.

Пороговый элемент 13 формирует на своем выходе сигнал высокого уровня при условии, что напряжение на

1

его входе U меньше заданного U, а поскольку входное напряжение порогового элемента 13 является выходным напряжением дифференцирующего элемента 10, то выполняется условие

я

и

dUe, dt

условия

где и - напряжение на выводах ос- вл

новного источника питания.

Таким образом, пороговый элемент 13 сравнивает с опорным уровнем напряжение, пропорциональное скорости изменения напряжения на выводе основного источника питания. При этом опорньй уровень U выбирается из

n

- (ЁЬ.) Mt

S40

f-)3- заданная скорость изменения Uo, выбираемая из услог- ВИЯ, что переходный процесс приблизился к своему установившемуся значению на- столько, что его можно считать завершенным.

конечном итоге на вькоде пороо элемента 13 поддерживается при выполнении условия

lf - b...

На выходе порогового элемента 12 поддерживается сигнал высокого уров- ня 1 при выполнении условия

и

«

и

ном

где и

Hefi

номинальное напряжение основного источника питания .

Таким образом, на выходе элемента И 14 присутствует уровень 1 при одновременном вьтолнении условий (1), (2) и (3). Наличие же уровня 1 на управляющих входах переключателей 2 и 3 соответствует коммутации на управляющие входы накопителя 1 внешних управляющих сигналов, т.е. разблокировке накопителя 1. В известном устройстве разблокировка происходит при достижении питающего напряжения порогового уровня и.

В предлагаемом устройстве накопитель разблокирован, когда переходный

UHOM

со

процесс войдет в зону tU скоростью не больше заданной (фиг. 2а, б

Условия по неравенствам (1) и (3) выбраны для исключения ложной разблокировки накопителя в точках максимума и минимума переходного процесса соответственно.

Таким образом, осуществляется управление процессом разблокировки накопителя 1 при постоянном отслеживании напряжения основного источника питания. В известном устройстве ;Такое отслеживание отсутств т, по- :этому при оптимальной установке времени задержки при использовании од

10

15

20

25

30

ного источника напряжения это время не будет оптимальным для другого источника или при изменении характера нагрузки источника, что проявляется при подсоединении к системе, в .составе которой работает запоминающее устройство, дополнительных модулей и при изменении параметров нагрузки со временем (старении). Если время задержки .t выбрать заведомо большим, чем оптимальное, то не будет обеспечено минимальное время бтовности известного устройства, что не позволяет использовать его в системах с резервированием (а именно в таких системах наиболее часто применяют запоминающие устройства с автономным питанием).

Для того, чтобы при дифференцировании напряжения переходного процесса не было ложных срабатываний системы от высокочастотных импульсных помех, обычно присутствующих в реальных систем ах, передаточная функция (W(S)) дифференцирующего элемента может быть выбрана следующим образом:

+ 1

( g ) (,j.

S + 1)

(4)

т,..

35 40

)

45

50

55

где Т. - постоянная времени дифференцирования, выбираемая из быстродействия переходного процесса;

Т - постоянная времени интегрирования , выбираемая из условия наибольшего подавления высокочастотных помех и зависящая от спектральных характеристик помехи; Т - постоянная времени, выбираемая из максимально возможной скорости перекодно- го процесса и ограничивающая верхнюю частоту дифференцируемого сигнала. В результате предложейных изменений схемы запоминающего устрьйства с сохранением информации при отключении питания, заключающихся и том, что в него введены последовательно соединенные дифференцирующий и второй пороговый элементы, а также третий пороговый элемент, причем входы дифференцирующего элемента и третье го порогового элемента подсоедяв01Ы

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1615809A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1983 |

|

SU1116461A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1987 |

|

SU1448362A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1990 |

|

SU1716573A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1988 |

|

SU1508286A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1695395A1 |

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU842975A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1982 |

|

SU1083236A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

Изобретение относится к запоминающим устройствам и предназначено для надежного хранения информации в цифровых вычислительных системах, в частности в системах с резервированием. Цель изобретения - повышение надежности устройства. Устройство .содержит накопитель 1, переключатель 2, резервный источник питания 3, элемент развязки 8, выход 9 для подключения основного источника питания, дифференцирующий элемент 10, пороговые элементы 11, 12, 13, элемент И 14 с соответствующими связями. В устройстве существует постоянное отслеживание изменения напряжения основного источника питания, что позволяет избежать индиввдуальной подстройки длительности задержки йод конкретную конфигурацию системы,которая питается от одного источника питания. 2 ил. i СЛ

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU807388A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1983 |

|

SU1116461A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-07—Публикация

1986-09-22—Подача