Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных устройств хранения и обработки цифровой информации, работающих на нижнем уровне АСУТП в условиях высокого уровня помех. Цель изобретения - повышение надежности хранения информации.

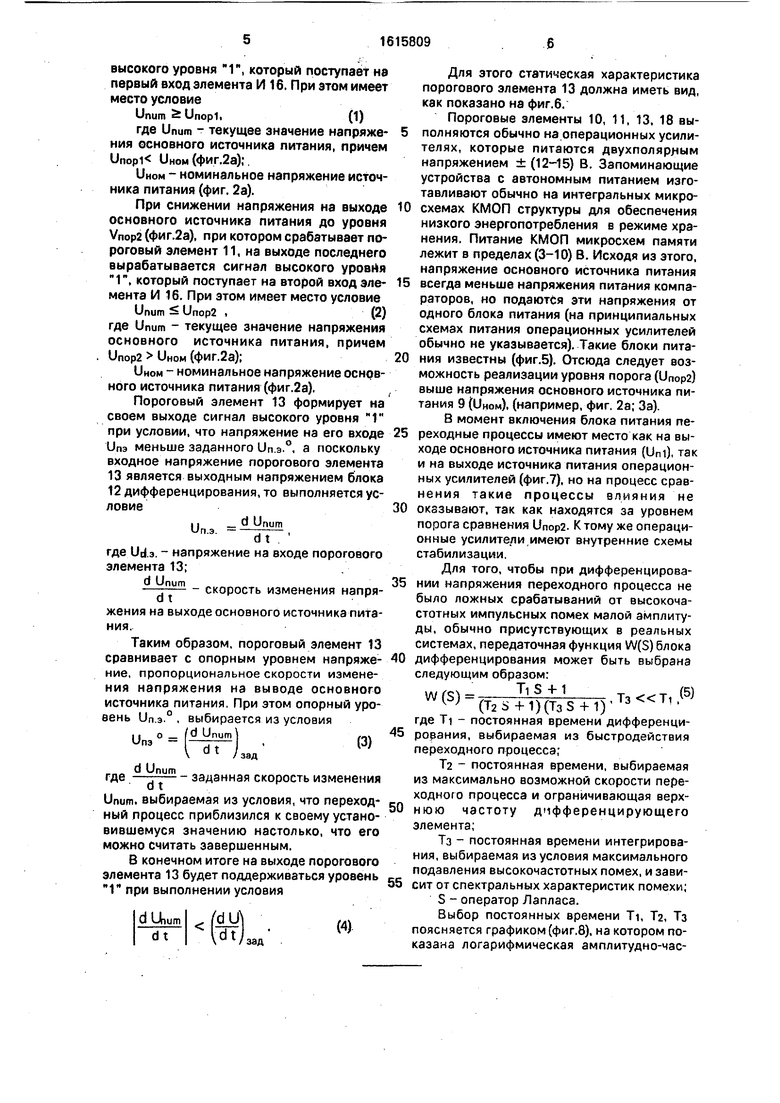

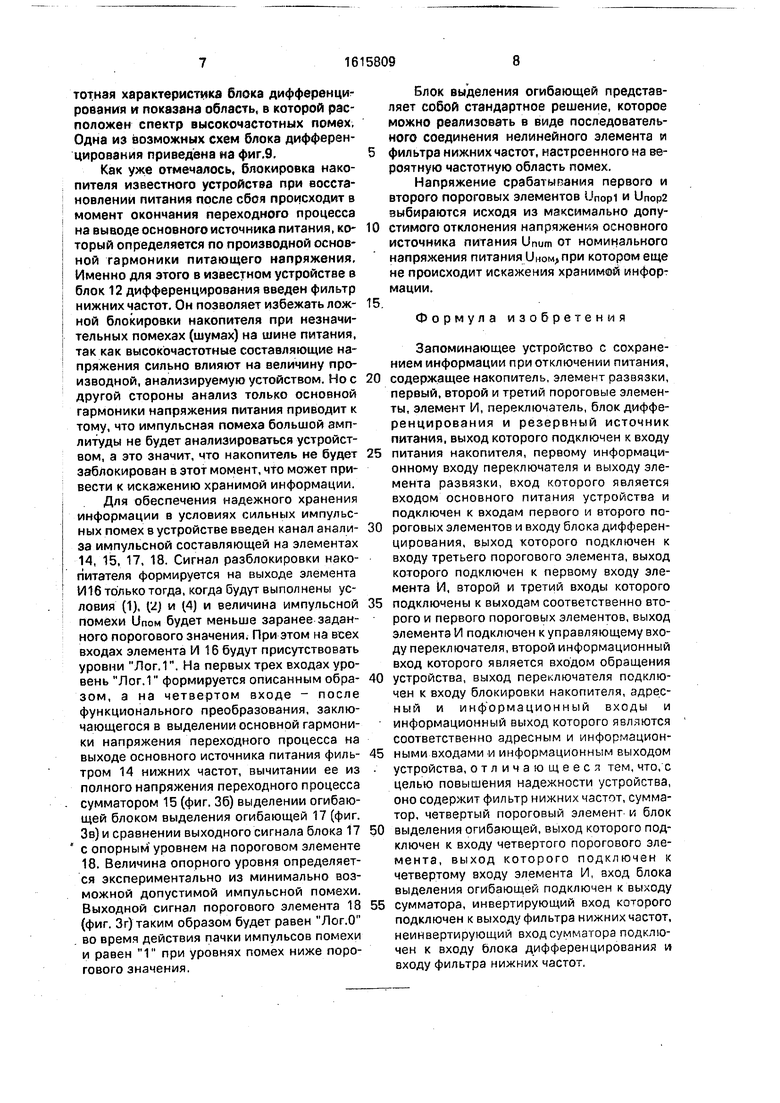

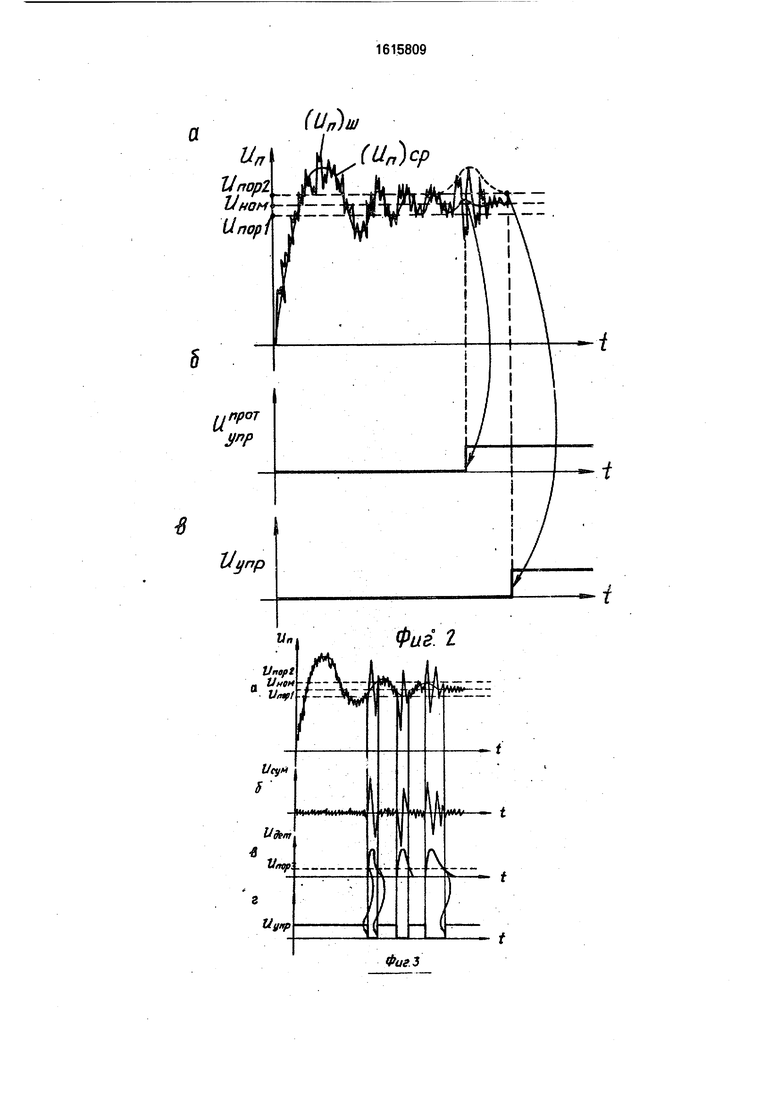

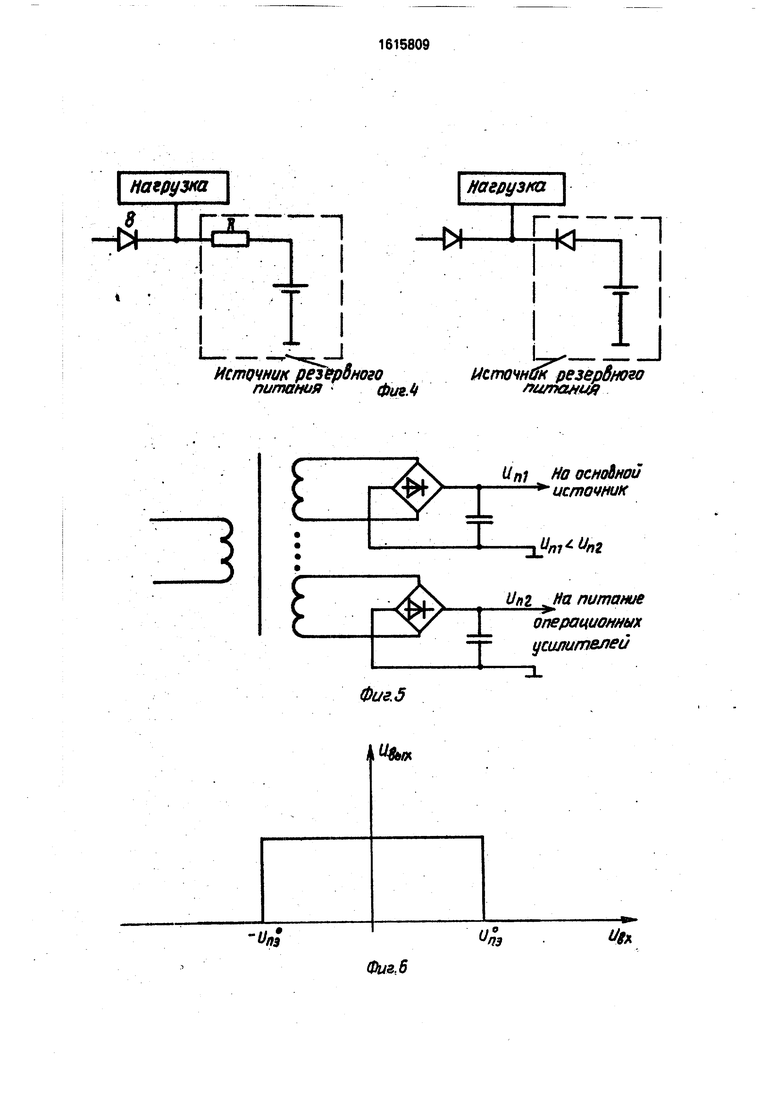

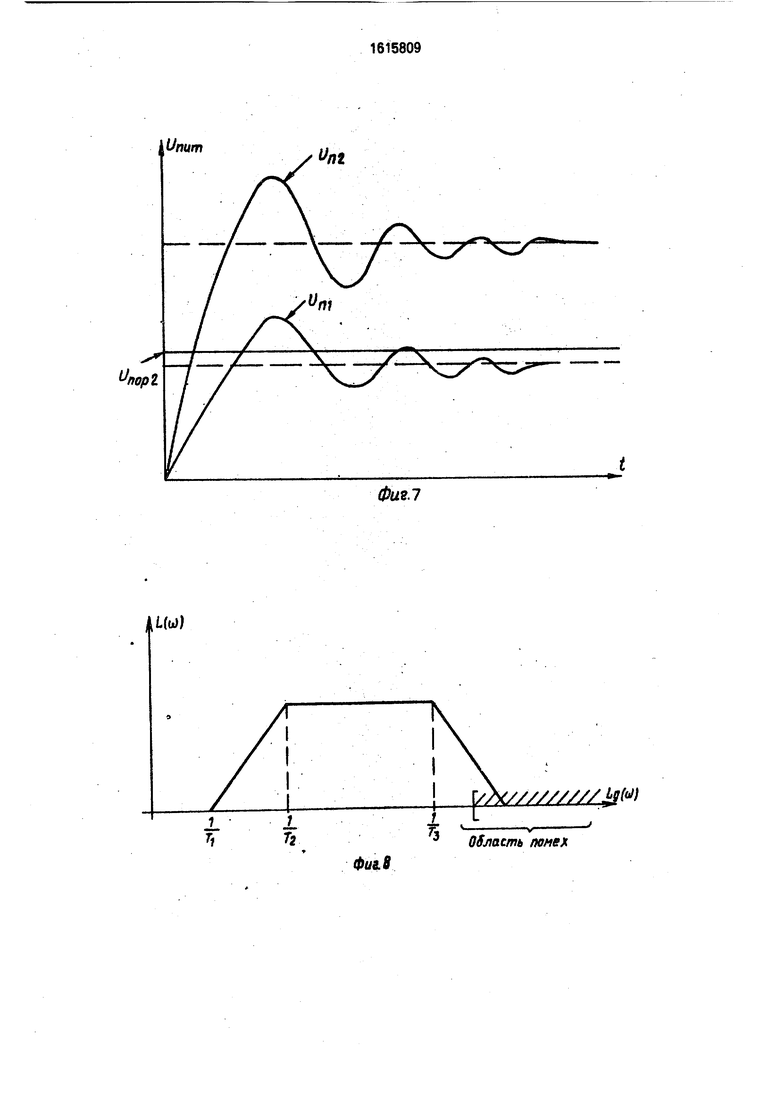

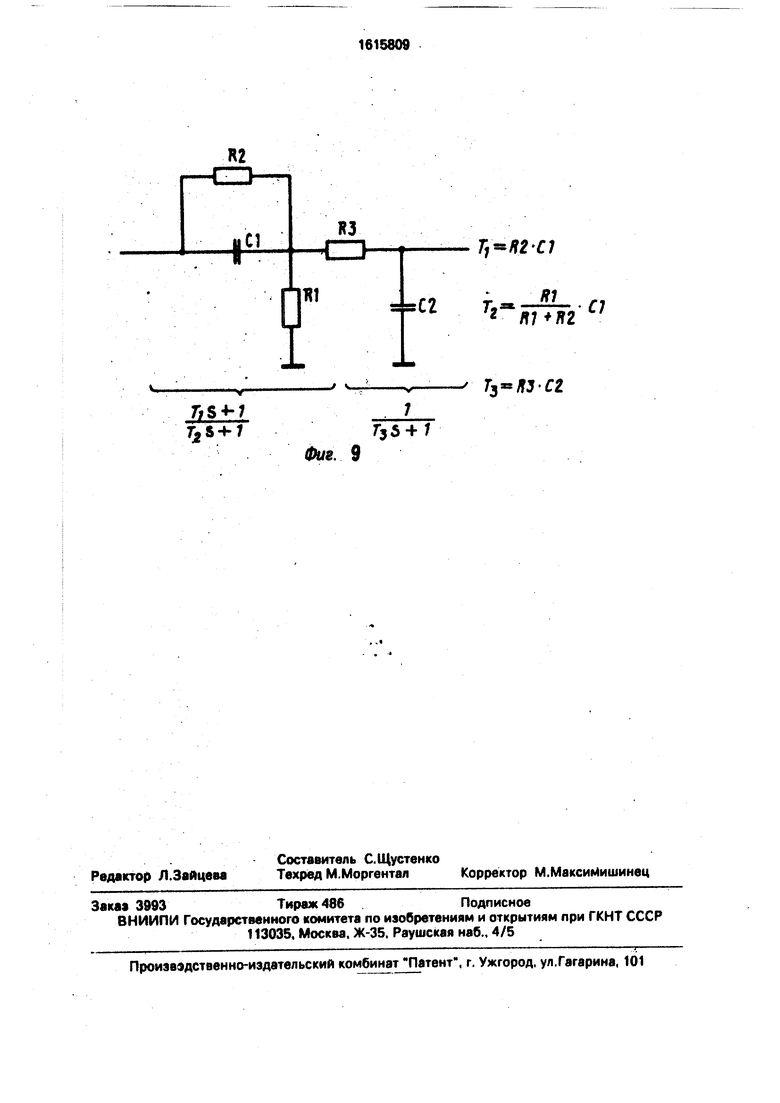

На фиг.1 показана структурная схема устройства; на фиг.2 - зависимости от времени напряжения источника питания, сигнала разблокировки накопителя для известного устройства сигнала разблокировки накопителя, приложенного к управляющему входу переключателя, для предлагаемого устройства; на фиг.З - от времени напряжения источника питания в случае больших импульсных помех, сигнала на выходе сумматора, сигнала на выходе блока выделения огибающей, сигнала на выходе четвертого порогового элемента; на фиг.4 - резервный источник питания; на фиг. 5 - схема блока питания устройства; на фиг.6 - статистическая характеристика третьего порогового элемента; на фиг. 7 - зависимость от времени напряжения питания (Uni) операционных усилителей и напряжения основного источника питания (Unz); на фиг.З - логарифмическая амплитудно-частотная характеристика блока дифференцирования; на фиг.9 - принципиальная схема и выбор постоянных времени блока дифференцирования.

Устройство содержит накопитель 1, переключатель 2, резервный источник 3 питания, вход 4 обращения, адресный вход 5, информационный вход 6, информационный выход 7, элемент развязки 8, вход 9 основного источника питания, пороговые элементы 10 и 11, блок 12 дифференцирования, пороговый элемент 13, фильтр 14 нижних частот, сумматор 15, элемент И 16, блок 17 выделения огибающей и пороговый элемент 18, подключенный своим выходом к четвертому входу элемента И.

Устройство работает следующим образом.

Пороговые элементы 10, 11, 13 сравнивают напряжения, подаваемые на их входы, с опорными уровнями напряжений, задава- ° емыми при настройке системы.

Если напряжение основного источника питания на входе 9 меньше Unopi (фиг.2а), то на выходе порогового элемента 10 поддерживается низкий уровень напряжения О, а при превышении входным напряжением Unopi выход порогового элемента 10 устанавливается в состояние с высоким уровнем напряжения 1. Если выходное напряжение пороговых элементов 11 и 13 меньше

опорных уровней (для 11 порогового элемента это Unop2 (фиг.2а), то на их входах поддерживается уровень 1, а если больше, то уровень О.

В автономном режиме, когда отсутствует напряжение основного источника 9. выход порогового элемента 10 находится в состоянии низкого уровня О и, следовательно, на выходе элемента И 16 поддержи- 0 вается состояние О. Перек лючатель 2 при таком состоянии управляющего вхрда коммутирует на вход блокировки накопителя 1 сигнал высокого уровня с резервного источника 3 питания. Происходит хранение запи- 5. санной в накопителе информации, причем обращение к нему заблокировано.

Резервный источник 3 питания имеет специальную конструкцию, позволяющую подключать его выход непосредственно к 0 одному из выводов элемента развязки. Это известное техническое решение заключающееся в том, что последовательно с резервным источником обычно включают токоограничивающее сопротивление 5 (фиг.4а). Поскольку резервные источники обычно выполняют в виде низковольтных аккумуляторов, то величина сопротивления выбирается из условия протекания небольшого зарядного тока через аккумулятор при 0 работе от основного источника.

В режиме резервного питания запоминающее устройство находится в режиме хранения, при этом по техническим условиям допускается работа при пониженном на- 5 пряжении питания для уменьшения потребляемой мощности, поэтому напряжение основного источника питания принципиально больше напряжения резервного источника. Исходя из этого, когда элемент 0 развязки 8 открыт напряжением основного источника, резервный источник находится в режиме подзаряда. При переходе на резервное питание падение напряжения на сопротивлении безусловно приводит к 45 уменьшению напряжения питания, но так как потребляемый накопителем 1 ток в режиме хранения весьма мал, это уменьшение пренебрежимо мало по сравнению с напряжением резервного источника. Кроме того, 50 резервный источник может содержать и разделительный диод (фиг,46).

При переключении на основной источник напряжение последнего (Unum) в силу инерционности нагрузки будет постепенно 55 нарастать, причем в общем случае будет носить колебательный характер (фиг, 2а). При достижении на выходе основного источника уровня Unopi (фиг. 2а), при котором срабатывает первый пороговый элемент 10. на выходе последнего вырабатывается сигнал

высокого уровня Г, который поступает на первый вход элемента И 16. При этом имеет место условие

Unum Unopi,(1)

где Unum - текущее эначение напряже- ния основного источника питания, причем Unopi UHOM (фиг.2а);.

UHOM номинальное напряжение источника питания (фиг. 2а).

При снижении напряжения на выходе основного источника питания до уровня Vnop2 (фиг.2а), при котором срабатывает пороговый элемент 11, на выходе последнего вырабатывается сигнал высокого уровйя 1, который поступает на второй вход эле- мента И 16. При этом имеет место условие

Unum 2 Unop2 ,(2)

где Unum - текущее значение напряжения основного источника питания, причем Unop2 UHOM (фиг.2а);

UHOM - номинальное напряжение основного источника питания (фиг.2а}.

Пороговый элемент 13 формирует на своем выходе сигнал высокого уровня 1 при условии, что напряжение на его входе Una меньше заданного Un.a.. а поскольку входное напряжение порогового элемента 13 является выходным напряжением блока 12 дифференцирования, то выполняется условие

11 - .JJnum

Un.3.,

где Urf.3. - напряжение на входе порогового элемента 13;

d Unum

--:скорость изменения напря0 t,

жения на выходе основного источника питания.

Таким образом, пороговый элемент 13 сравнивает с опорным уровнем напряже- ние, пропорциональное скорости изменения напряжения на выводе основного источника питания. При этом опорный уровень Un.3.

и,

где

dU

выбирается из условия d Unum

/зад

(3)

пиш

dt

- заданная скорость изменения

Unum. выбираемая из условия, что переход- ный процесс приблизился к своему установившемуся значению настолько, что его можно Считать завершенным.

В конечном итоге на выходе порогового элемента 13 будет поддерживаться уровень 1 при выполнении условия

/dU)

St)

(4)

зад

5

1015

20

25 30

35

0

5

п

g

Для этого статическая характеристика порогового элемента 13 должна иметь вид, как показано на фиг.6.

Пороговые элементы 10, 11, 13, 18 выполняются обычно на операционных усилителях, которые питаются двухполярлым напряжением ± (12-15) В. Запоминающие устройства с автономным питанием изготавливают обычно на интегральных микросхемах КМОП структуры для обеспечения низкого энергопотребления в режиме хранения. Питание КМОП микросхем памяти лежит в пределах (3-10) В. Исходя из этого, напряжение основного источника питания всегда меньше напряжения питания компараторов, но подаются эти напряжения от одного блока питания (на принципиальных схемах питания операционных усилителей обычно не указывается). Такие блоки питания известны (фиг.5). Отсюда следует возможность реализации уровня порога (Unop2) выше напряжения основного источника питания 9 (UHOM), (например, фиг. 2а; За).

В момент включения блока питания переходные процессы имеют место как на выходе основного источника питания (Uni), так и на выходе источника питания операционных усилителей (фиг.7), но на процесс сравнения такие процессы влияния не оказывают, так как находятся за уровнем порога сравнения Unop2. К тому же операционные усилители имеют внутренние схемы стабилизации.

Для того, чтобы при дифференцировании напряжения переходного процесса не было ложных срабатываний от высокочастотных импульсных помех малой амплитуды, обычно присутствующих в реальных системах, передаточная функция W(S) блока дифференцирования может быть выбрана следующим образом:

(т.ь1 ,)аз з.1)з«т,р)

где TI - постоянная времени дифференци- рорания, выбираемая из быстродействия переходного процесса;

Т2 - постоянная времени, выбираемая из максимально возможной скорости переходного процесса и ограничивающая верхнюю частоту дифференцирующего элемента;

Тз - постоянная времени интегрирования, выбираемая из условия максимального подавления высокочастотных помех, и зависит от спектральных характеристик помехи;

S - оператор Лапласа.

Выбор постоянных времени Ti, Т2, Тз поясняется графиком (фиг.8), на котором показана логарифмическая амплитудно-частоткая характеристика блока дифференцирования и показана область, в которой расположен спектр высокочастотных помех, Одна из возможных схем блока дифференцирования приведена на фиг.9.

Как уже отмечалось, блокировка накопителя известного устройства при восстановлении питания после сбоя происходит в момент окончания переходного процесса на выводе основного источника питания, который определяется по производной основной гармоники питающего напряжения. Именно для этого в известном устройстве в блок 12 дифференцирования введен фильтр нижних частот. Он позволяет избежать ложной блокировки накопителя при незначительных помехах (шумах) на шине питания, так как высокочастотные составляющие на- пряжения сильно влияют на величину производной, анализируемую устойством. Но с другой стороны анализ только основной гармоники напряжения питания приводит к тому, что импульсная помеха большой амплитуды не будет анализироваться устройством, а это значит, что накопитель не будет заблокирован в этот момент, что может привести к искажению хранимой информации. Для обеспечения надежного хранения информации в условиях сильных импульсных помех в устройстве введен канал анализа импульсной составляющей на элементах 14, 15, 17, 18. Сигнал разблокировки нако- Нитателя формируется на выходе элемента И16 только тогда, когда будут выполнены условия (1), () и (4) и величина импульсной помехи UnoM будет меньше заранее заданного порогового значения. При этом на всех входах элемента 1/1 16 будут присутствовать уровни Лог, Г. На первых трех входах уровень Лог,1 формируется описанным образом, а на четвертом входе - после функционального преобразования, заключающегося в выделении основной гармоники напряжения переходного процесса на выходе основного источника питания фильтром 14 нижних частот, вычитании ее из полного напряжения переходного процесса сумматором 15 (фиг, 36) выделении огибающей блоком выделения огибающей 17 (фиг. Зв)и сравнении выходного сигнала блока 17 с опорным уровнем на пороговом элементе 18, Величина опорного уровня определяется экспериментально из минимально возможной допустимой импульсной помехи. Выходной сигнал порогового элемента 18 (фиг, Зг) таким образом будет равен Лог,0 во время действия пачки импульсов помехи и равен 1 при уровнях помех ниже порогового значения.

Блок выделения огибающей представяет собой стандартное решение, которое ожно реализовать в виде последовательного соединения нелинейного элемента и

ильтра нижних частот, настроенного на вероятную частотную область помех.

Напряжение срабатывания первого и второго пороговых элементов Unopi и Unop2 эыбираются исходя из максимально допустимого отклонения напряжений основного источника питания Unum от номинального напряжения питания UHOM при котором еще не происходит искажения хранимой информации.

Формула изобретения

Запоминающее устройство с сохранением информации при отключении питания,

содержащее накопитель, элемент развязки, первый, второй и третий пороговые элементы, элемент И, переключатель, блок дифференцирования и резервный источник питания, выход которого подключен к входу

питания накопителя, первому информационному входу переключателя и выходу элемента развязки, вход которого является входом основного питания устройства и подключен к входам первого и второго пороговых элементов и входу блока дифференцирования, выход хоторого подключен к входу третьего порогового элемента, выход которого подключен к первому входу элемента 1/1, второй и третий входы которого

подключены к выходам соответственно второго и первого пороговых элементов, выход элемента 1/1 подключен к управляющему входу переключателя, второй информационный вход которого является входом обращения

устройства, выход переключателя подключен к входу блокировки накопителя, адресный и информационный входы и информационный выход которого являются соответственно адресным и информационными входами и информационным выходом

устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит фильтр нижних частот, сумматор, четвертый пороговый элемент и блок

выделения огибающей, выход которого подключен к входу четвертого порогового элемента, выход которого подключен к четвертому входу элемента И, вход блока выделения огибающей подключен к выходу

сумматора, инвертирующий вход которого подключен к выходу фильтра нижних частот, неинвертирующий вход сумматора подключен к входу блока дифференцирования и входу фильтра нижних частот.

(Un}

П)Ш

ил

1/порП Ином -

Unopi

Uyiy

(Un}cp

Фаг.З

Нагрузка

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1408458A1 |

| Индикаторное устройство | 1990 |

|

SU1744472A2 |

| Запоминающее устройство с сохранением информации при отключении питания | 1983 |

|

SU1116461A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1982 |

|

SU1083236A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1987 |

|

SU1434504A1 |

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU842975A1 |

| Запоминающее устройство с сохранением информации при отключении питания ранением | 1987 |

|

SU1681337A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения и обработки цифровой информации, работающих на нижнем уровне АСУТП в условиях высокого уровня помех. Цель изобретения - повышение надежности устройства. Устройство содержит накопитель 1, переключатель 2, резервный источник питания 3, вход 4 обращения устройства, адресный вход 5, информационный вход 6, информационный выход 7, элемент развязки 8, вход 9 основного источника питания, пороговые элементы 10, 11, блок 12 дифференцирования, пороговый элемент 13, элемент И 16, фильтр 14 нижних частот, сумматор 15, блок 17 выделения огибающей, пороговый элемент 18. Поставленная цель достигается тем, что обращение к накопителю решается только при окончании переходного процесса по основной гармонике напряжения источника питания и при отсутствии импульсных помех большой амплитуды. 9 ил.

п

I

-,i.,l

Источник pneptmto питания ФигЛ

-«/л/

-w

Ucmo4HW резерВно ffumoHiuff

Фиг. 5

у-.

A

Фмз,5

Unum

± ri

л

T2

Фие.7

I r/ v///x//x//jgfo/;

f.

Область помек

i

C1

R3

Фие. 9

C2

:. Ki

2

a

Ту из-сг

| Запоминающее устройство с сохранением информации при отключении питания | 1982 |

|

SU1083236A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1408458A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-12-23—Публикация

1989-01-30—Подача