Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, блок сопряжения, основной и резервный источники питания, стабилизатор тока, разделительные элементы, группу элементов гальванической развязки 1.

Недостатком данного устройства является возможность разрушения информации, записанной в накопителе на КМОП-структурах, при изменении сигналов на адресном входе устройства и при коммутации основного источника питания.

Известно также запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, рез.ервный источник питания, блок сопряжения, пороговые элементы, переключатели, триггер, элемент задержки и элемент ИЛИ 2.

Недостатком указанного устройства является возможность разрушения информации, запис анной в накопителе на КМОПструктурах, при изменении сигналов на адресном входе устройства.

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с резервным источником питания, содержащее накопитель, блок сопряжения, пороговый элемент, разделительный, фильтрующий и ограничительный элементы и резервный источник питания, причем вход питания накопителя подключен через фильтрующий элемент к щине нулевого потенциала, через ограничительный элемент к выходу резервного источника питания и непосре |,ственно к одному из выводов разделительного элемента, другой вывод которого, вход порогового элемента и вход блока сопряжения подключены к входу основного питания устройства, информационный вход и выход накопи теля соединены соответственно с первыми выходом и входом блока сопряжения, второй, третий, четвертый и пятый входы и второй выход которого являются адресным, чтения, записи и информационным входами и информационным выходом устройства соответственно 3.

Недостатком этого устройства является возможность разрушения информации, записанной в накопителе, выполненном на КМОП-структурах, при изменении сигналов на адресном входе устройства.

Указанный недостаток обусловлен тем, что при номинальном на пряженииосновного источника питания вход накопителя постоянно находится под разрешающим потенциалом и потому при смене адресных сигналов, либо при наличии помех на адресном входе устройства при фиксированном адресе, может произойти изменение записанной в

накопителе информации, т. е. ее разрущение.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что - в запоминающее устройство с сохранением информации при отключении питания, содержащее накопитель, блок сопряжения, пороговый, разделительный фильтрующий и ограничительный элементы, резервный источник питания, причем первый вход накопителя подключен через фильтрующий элемент к щине нулевого потенциала, через ограничительный элемент к выходу резервного источника питания и к одному

5 из выводов разделительного элемента, другой вывод которого подключен к входу порогового элемента, первому входу блока сопряжения и щине питания, второй вход и выход накопителя соединены соответственно с первым выходом и вторым входом

0 блока сопряжения, третий вход, которого является адресным, четвертый вход - информационным, пятый и шестой входы - управляющими входами устройства, второй выход блока сопряжения является ин5 формационным выходом устройства, введены регистр адреса, элемент ИЛИ, первый и второй элементы И, первый и второй формирователи импульсов и элемент задержки, причем третий выход блока сопряжения подключен к первому входу ре0 гистра адреса, четвертый выход - к первому входу элемента ИЛИ, пятый выход - к второму входу элемента ИЛИ и первому входу второго элемента И, второй вход которого соединен с первым входом первого элемента И и выходом порогового элемента,

второй вход первого элемента И соединен с выходом элемента ИЛИ, третий вход которого соединен с щиной питания, выход первого элемента И соединен с первым входом первого формирователя импульсов,

Q выход которого соединен с вторым входом регистра адреса и первым входом элемента задержки, выход которого подключен к первому входу второго формирователя импульсов, выход которого подключен к третьему входу накопителя, выходы регистра адреса

5 и второго элемента И соединены соответственно с четвертым и пятым входами накопителя, третьи входы регистра адреса, первого и второго элементов И, вторые входы формирователей импульсов и элемента задержки соединены с первым входом накопатеЛя.

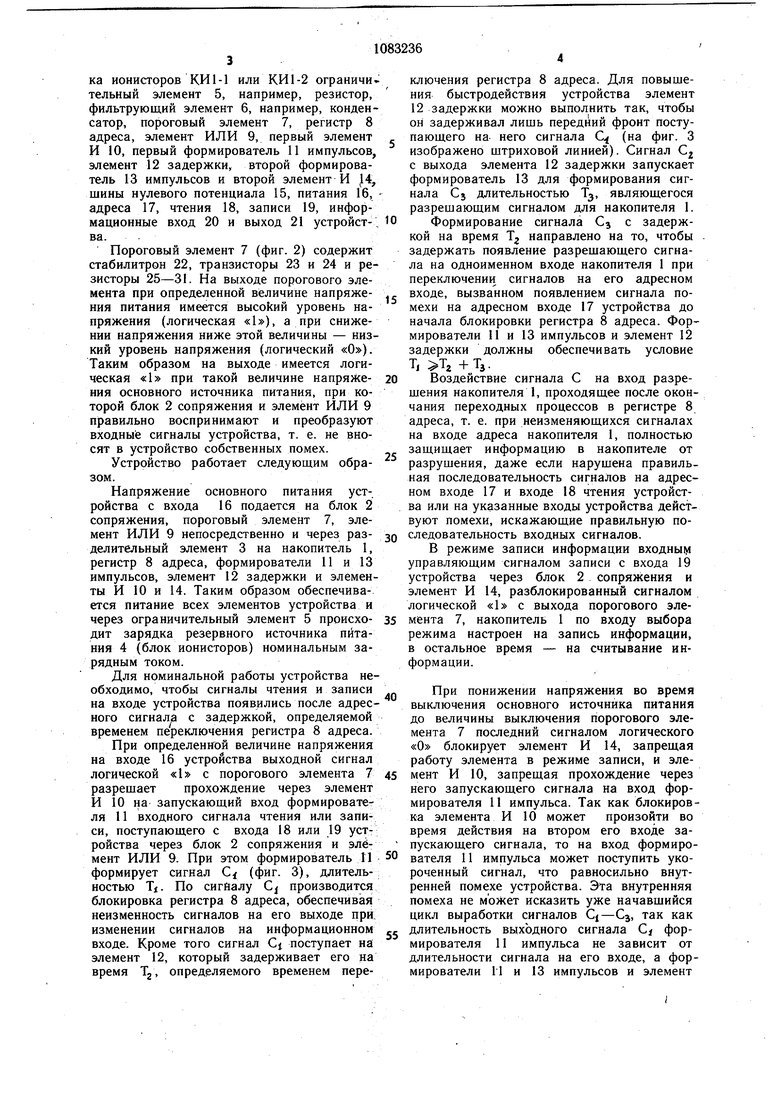

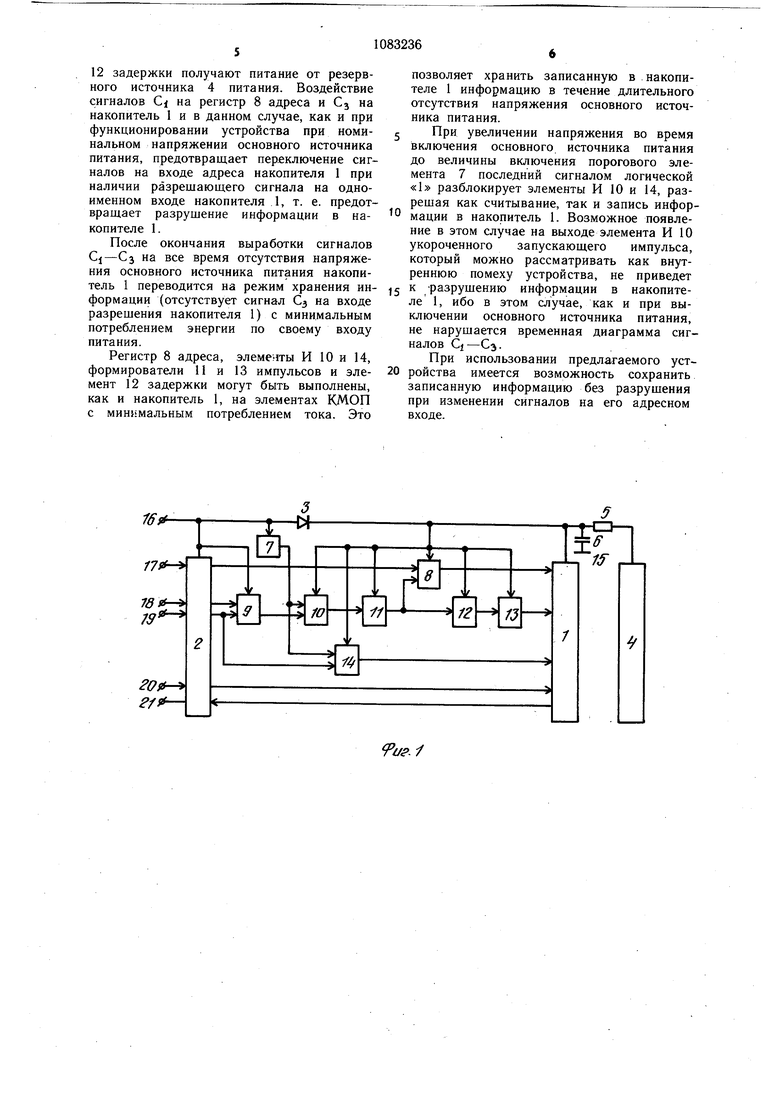

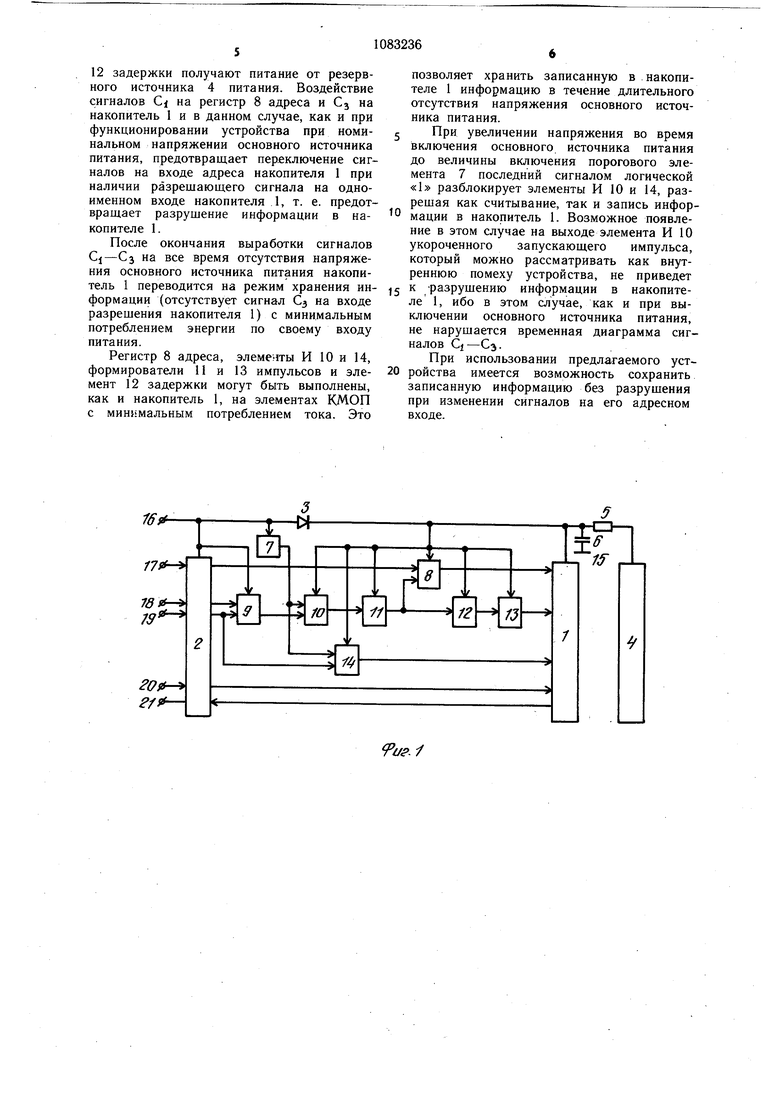

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - пример реализации порогового элемента; на фиг. 3 временная диаграмма работы устройства.

5 Устройство содержит накопитель 1, блок 2 сопряжения, разделительный элемент 3, например диод, резервный источник 4 питания, выполненный, например, в виде блока ионисторов КИ1 -1 или КИ1-2 ограничи тельный элемент 5, например, резистор, фильтрующий элемент 6, например, конденсатор, пороговый элемент 7, регистр 8 адреса, элемент ИЛИ 9, первый элемент И 10, первый формирователь 11 импульсов, элемент 12 задержки, второй формирователь 13 импульсов и второй элемент И 4, шины нулевого потенциала 15, питания 16, адреса 17, чтения 18, записи 19, информационные вход 20 и выход 21 устройст-. ва.

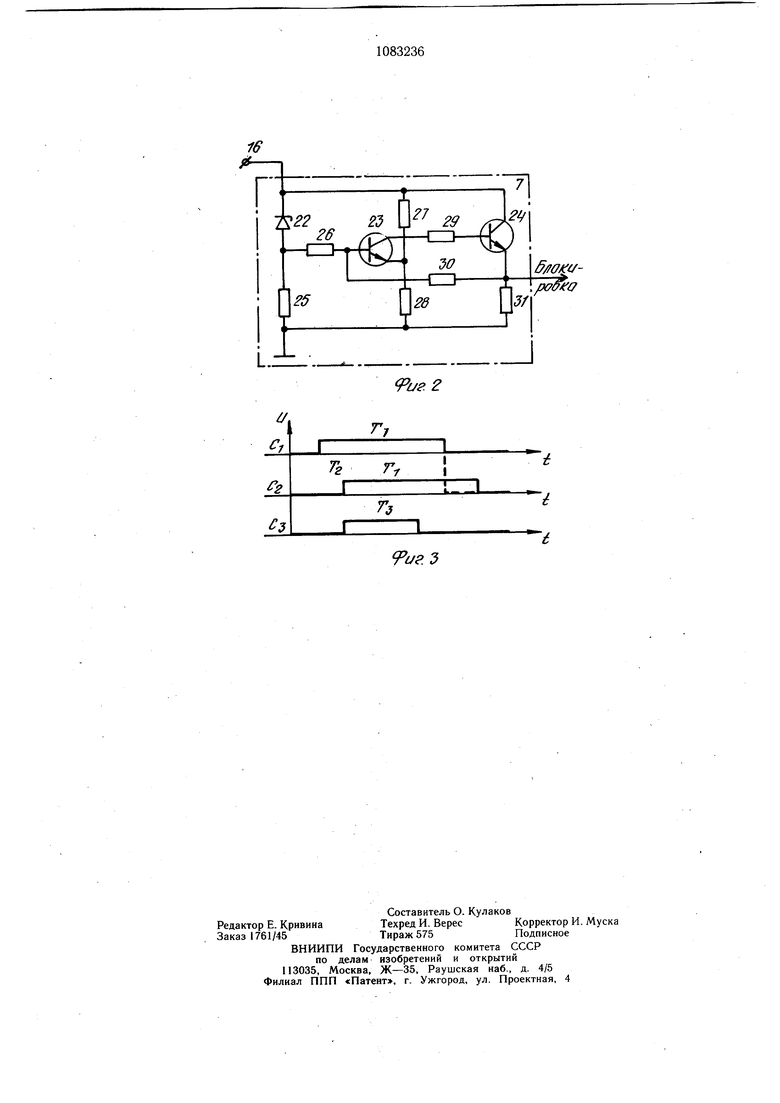

Пороговый элемент 7 (фиг. 2) содержит стабилитрон 22, транзисторы 23 и 24 и резисторы 25-31. На выходе порогового элемента при определенной величине напряжения питания имеется высоКий уровень напряжения (логическая «1), а при снижении напряжения ниже этой величины - низкий уровень напряжения (логический «О). Таким образом на выходе имеется логическая «1 при такой величине напряжения основного источника питания, при которой блок 2 сопряжения и элемент ИЛИ 9 правильно воспринимают и преобразуют входные сигналы устройства, т. е. не вносят в устройство собственных помех.

Устройство работает следующим образом.

Напряжение основного питания устройства с входа 16 подается на блок 2 сопряжения, пороговый элемент 7, элемент ИЛИ 9 непосредственно и через разделительный элемент 3 на накопитель 1, регистр 8 адреса, формирователи 11 и 13 импульсов, элемент 12 задержки и элементы И 10 и 14. Таким образом обеспечивается питание всех элементов устройства и через ограничительный элемент 5 происходит зарядка резервного источника питания 4 (блок ионисторов) номинальным зарядным током.

Для номинальной работы устройства необходимо, чтобы сигналы чтения и записи на входе устройства появились после адресного сигнала с задержкой, определяемой временем переключения регистра 8 адреса.

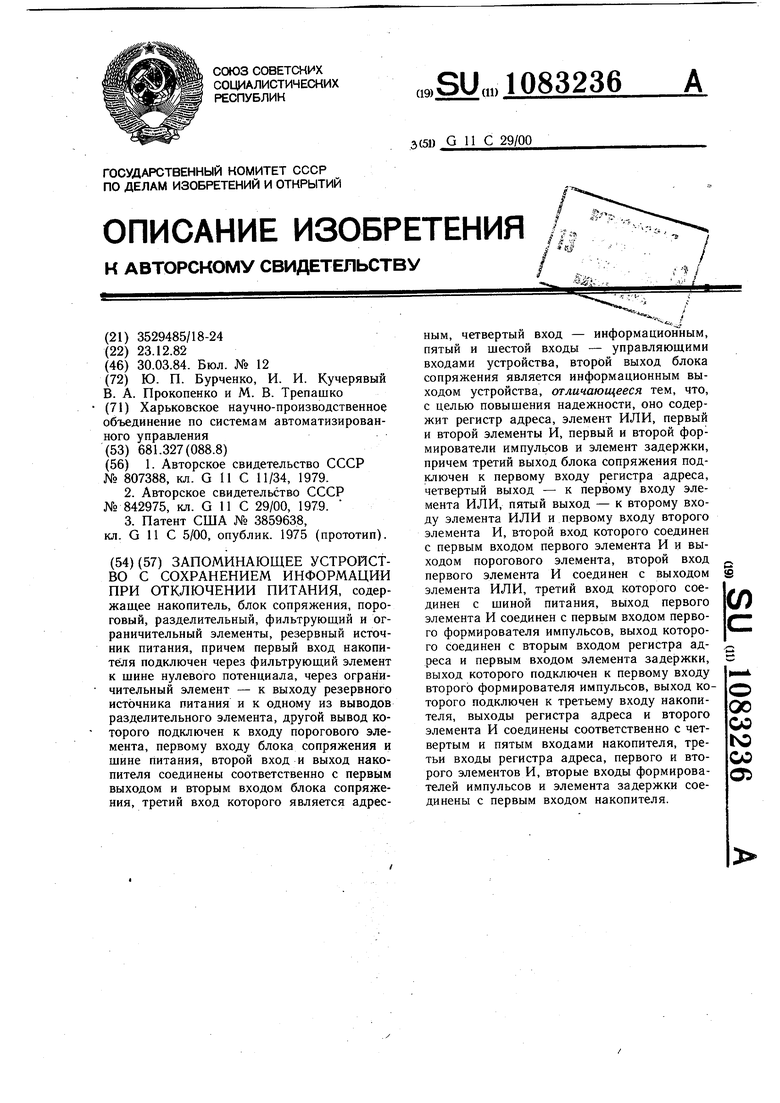

При определенной величине напряжения на входе 16 устройства выходной сигнал логической «1 с порогового элемента 7 разрешает прохождение через элемент И 10 на запускающий вход формирователя 11 входного сигнала чтения или записи, поступающего с входа 18 или 19 устройства через блок 2 сопряжения и элемент ИЛИ 9. При этом формирователь П формирует сигнал С (фиг. 3), длительностью Tf. По сигйалу Cj производится блокировка регистра 8 адреса, обеспечивая неизменность сигналов на его выходе при, изменении сигналов на информационном входе. Кроме того сигнал Cf поступает на элемент 12, который задерживает его на время Tj, определяемого временем переключения регистра 8 адреса. Для повышения быстродействия устройства элемент 12 задержки можно выполнить так, чтобы он задерживал лишь передний фронт поступающего на него сигнала Q (на фиг. 3 изображено штриховой линией). Сигнал С с выхода элемента 12 задержки запускает формирователь 13 для формирования сигнала С; длительностью Т, являющегося разрешающим сигналом для накопителя 1.

Формирование сигнала Cj с задержкой на время Т направлено на то, чтобы задержать появление разрещающего сигнала на одноименном входе накопителя 1 при переключении сигналов на его адресном входе, вызванном появлением сигнала помехи на адресном входе 17 устройства до начала блокировки регистра 8 адреса. Формирователи 11 и 13 импульсов и элемент 12 задержки должны обеспечивать условие Т, Тг +Тз.

Воздействие сигнала С на вход разрещения накопителя 1, проходящее после окончания переходных процессов в регистре 8 адреса, т. е. при неизменяющихся сигналах на входе адреса накопителя 1, полностью защищает информацию в накопителе от разрушения, даже если нарушена правильная последовательность сигналов на адресном входе 17 и входе 18 чтения устройства или на указанные входы устройства действуют помехи, искажающие правильную последовательность входных сигналов.

В режиме записи информации входным управляющим сигналом записи с входа 19 устройства через блок 2 сопряжения и элемент И 14, разблокированный сигналом логической «1 с выхода порогового элемента 7, накопитель 1 по входу выбора режима настроен на запись информации, в остальное время - на считывание информации.

При понижении напряжения во время выключения основного источника питания до величины выключения порогового элемента 7 последний сигналом логического «О блокирует элемент И 14, запрещая работу элемента в режиме записи, и элемент И 10, запрещая прохождение через него запускающего сигнала на вход формирователя 11 импульса. Так как блокировка элемента И 10 может произойти во время действия на втором его входе запускающего сигнала, то на вход формирователя 11 импульса может поступить укороченный сигнал, что равносильно внутренней помехе устройства. Эта внутренняя помеха не может исказить уже начавшийся цикл выработки сигналов Q-Cj, так как длительность выходного сигнала С формирователя 11 импульса не зависит от длительности сигнала на его входе, а формирователи 11 и 13 импульсов и элемент

12 задержки получают питание от резервного источника 4 питания. Воздействие сигналов Cj на регистр 8 адреса и Сз на накопитель 1 и в данном случае, как и при функционировании устройства при номинальном напряжении основного источника питания, предотвращает переключение сигналов на входе адреса накопителя 1 при наличии разрешающего сигнала на одноименном входе накопителя 1, т. е. предотвращает разрушение информации в накопителе 1.

После окончания выработки сигналов Cj-Сз на все время отсутствия напряжения основного источника питания накопитель 1 переводится на режим хранения информации (отсутствует сигнал Сз на входе разрешения накопителя 1) с минимальным потреблением энергии по своему входу питания.

Регистр 8 адреса, элементы И 10 и 14, формирователи 11 и 13 импульсов и элемент 12 задержки могут быть выполнены, как и накопитель 1, на элементах КМОП с минимальным потреблением тока. Это

позволяет хранить записанную в накопителе 1 информацию в течение длительного отсутствия напряжения основного источника питания.

При увеличении напряжения во время включения основного источника питания до величины включения порогового элемента 7 последний сигналом логической «1 разблокирует элементы И 10 и 14, разрешая как считывание, так и запись информации в накопитель 1. Возможное появление в этом случае на выходе элемента И 10 укороченного запускающего импульса, который можно рассматривать как внутреннюю помеху устройства, не приведет

к -разрушению информации в накопителе 1, ибо в этом случае, как и при выключении основного источника питания, не нарушается временная диаграмма сигналов GI-Сэ.

При использовании предлагаемого устройства имеется возможность сохранить записанную информацию без разрушения при изменении сигналов на его адресном входе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1983 |

|

SU1116461A1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 2004 |

|

RU2261470C1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1975 |

|

SU627539A1 |

| Устройство для зарядки емкостного накопителя | 1990 |

|

SU1780151A1 |

| Оперативное запоминающее устройство | 1981 |

|

SU970462A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| Запоминающее устройство | 1979 |

|

SU809364A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С СОХРАНЕНИЕМ ИНФОРМАЦИИ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ, содержащее накопитель, блок сопряжения, пороговый, разделительный, фильтрующий и ограничительный элементы, резервный источник питания, причем первый вход накопителя подключен через фильтрующий элемент к шине нулевого потенциала, через ограничительный элемент - к выходу резервного источника питания и к одному из выводов разделительного элемента, другой вывод которого подключен к входу порогового элемента, первому входу блока сопряжения и шине питания, второй вход и выход накопителя соединены соответственно с первым выходом и вторым входом блока сопряжения, третий вход которого является адресным, четвертый вход - информационным, пятый и шестой входы - управляющими входами устройства, второй выход блока сопряжения является информационным выходом устройства, отличающееся тем, что, с целью повышения надежности, оно содержит регистр адреса, элемент ИЛИ, первый и второй элементы И, первый и второй формирователи импульсов и элемент задержки, причем третий выход блока сопряжения подключен к первому входу регистра адреса, четвертый выход - к первому входу элемента ИЛИ, пятый выход - к второму входу элемента ИЛИ и первому входу второго элемента И, второй вход которого соединен с первым входом первого элемента И и выходом порогового элемента, второй вход i первого элемента И соединен с выходом элемента ИЛИ, третий вход которого сое(Л динен с шиной питания, выход первого элемента И соединен с первым входом первого формирователя импульсов, выход которого соединен с вторым входом регистра адреса и первым входом элемента задержки, выход которого подключен к первому входу второго формирователя импульсов, выход которого подключен к третьему входу накописх со to теля, выходы регистра адреса и второго элемента И соединены соответственно с четвертым и пятым входами накопителя, тресо тьи входы регистра адреса, первого и второго элементов И, вторые входы формироваО5 телей импульсов и элемента задержки соединены с первым входом накопителя.

аг--/

23

p

иг2

.Ъ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с сохранениемиНфОРМАции пРи ОТКлючЕНии пиТАНия | 1979 |

|

SU807388A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-23—Подача