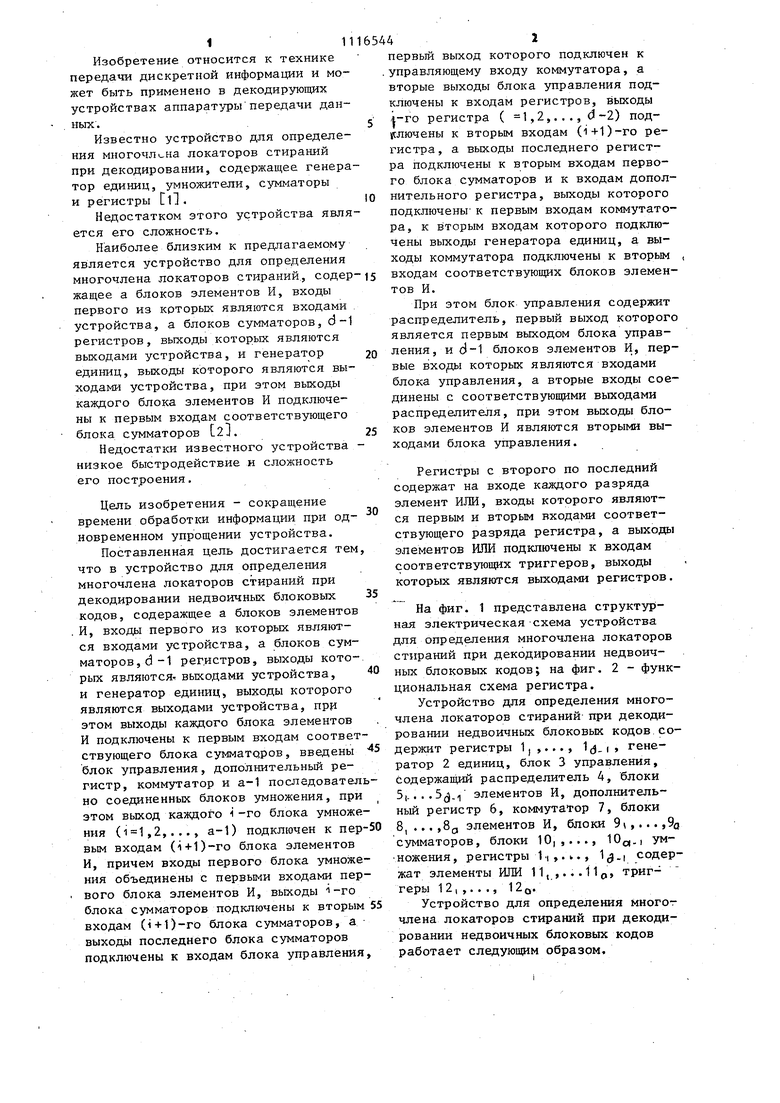

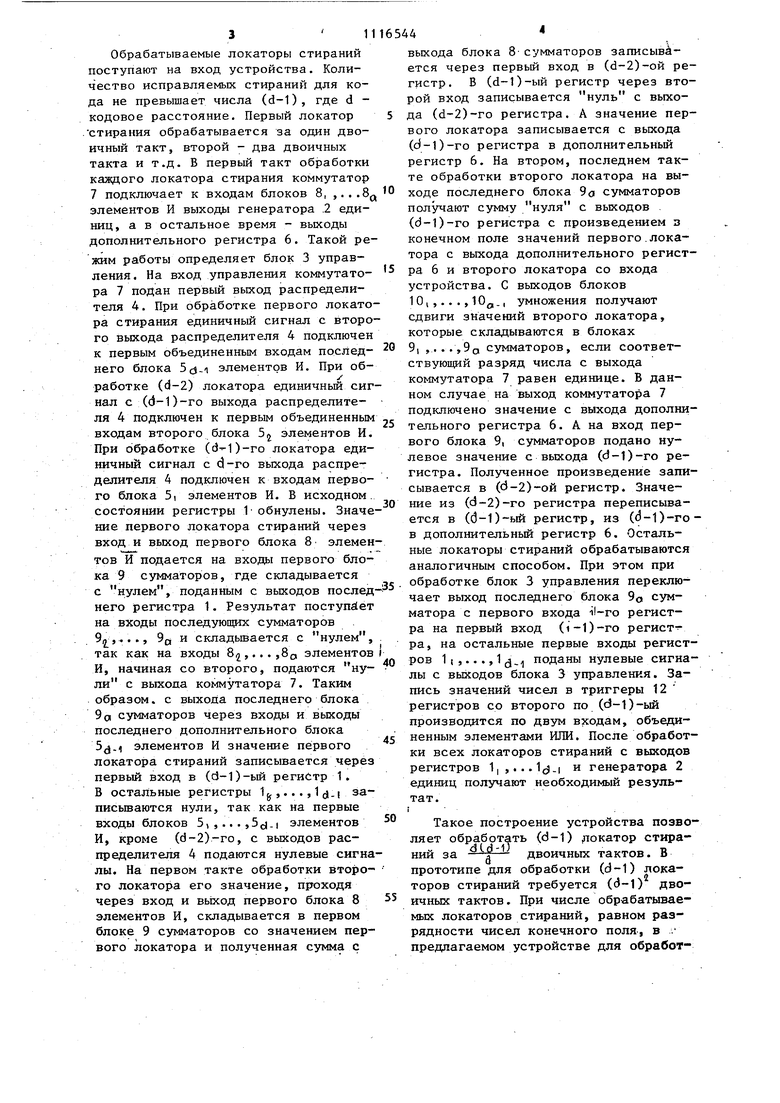

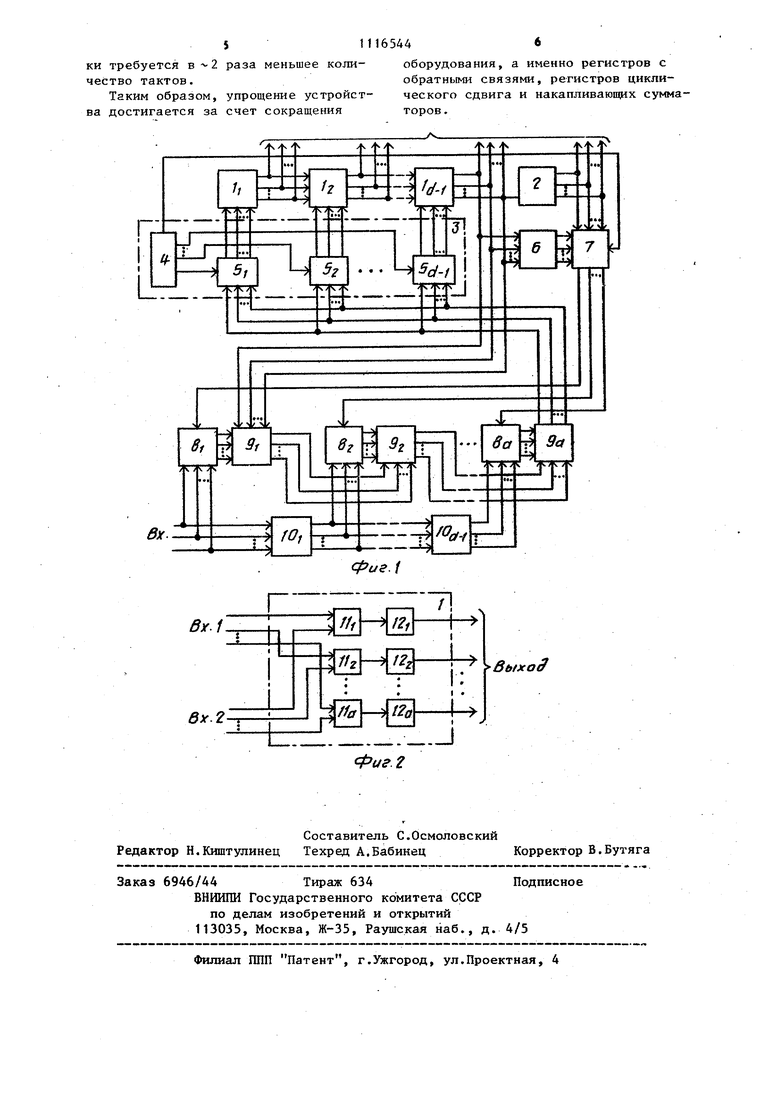

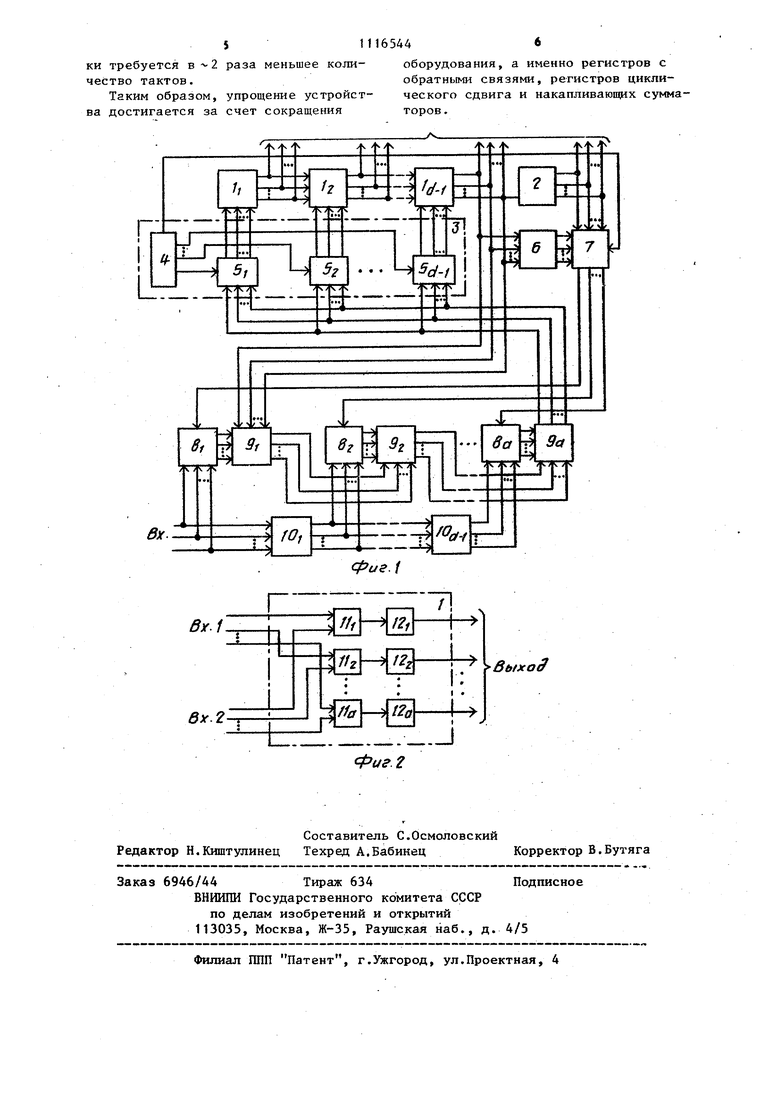

Изобретение относится к технике передачи дискретной информации и может быть применено в декодирующих устройствах аппаратурыпередачи данных., Известно устройство для определения многочлена локаторов стираний при декодировании, содержащее генера тор единиц, умножители, сумматоры и регистры Lll. Недостатком этого устройства явля ется его сложность. Наиболее близким к предлагаемому является устройство для определения многочлена локаторов стираний, содер жащее а блоков элементов И, входы первого из которых являются входами устройства, а блоков сумматоров, d-1 регистров, выходы которых являются выходами устройства, и генератор единиц, выходы которого являются выходами устройства, при этом выходы каждого блока элементов И подключены к первым входам соответствующего блока сумматоров 12J. Недостатки известного устройства низкое быстродействие и сложность его построения. Цель изобретения - сокращение времени обработ1Ш информации при од новременном упрощении устройства. Поставленная цель достигается тем что в устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов, содеражщее а блоков элементов И, входы первого из которых являются входами устройства, а блоков сумматоров, d-1 регистров, выходы которых являются выходами устройства, и генератор единиц, выходы которого являются выходами устройства, при этом выходы каждого блока элементов И подключены к первым входам соответ ствующего блока сумматоров, введены блок управления, дополнительный регистр, коммутатор и а-1 последовател но соединенных блоков умножения, при этом выход каждого i-го блока умноже ния (1 1,2,..., а-1) подключен к пер вьм входам (i+1)-ro блока элементов И, причем входы первого блока умноже ния объединены с первыми входами пер вого блока элементов И, выходы i-го блока сумматоров подключены к вторым входам (i+1)-ro блока сумматоров, а выходы последнего блока сумматоров подключены к входам блока управления первый выход которого подключен к управляющему входу коммутатора, а вторые выходы блока управления подключены к входам регистров, выходы i-го регистра ( 1,2,..., d-2) подкслючены к вторым входам (i+1)-ro регистра, а выходы последнего регистра подключены к вторым входам первого блока сумматоров и к входам дополнительного регистра, выходы которого подключены- к первым входам коммутатора, к вторым входам которого подключены выходы генератора единиц, а выходы коммутатора подключены к вторым , входам соответствующих блоков элементов И. При этом блок управления содержит распределитель, первый выход которого является первым выходом блока управления, и d-1 блоков элементов И, первые входы которых являются входами блока управления, а вторые входы соединены с соответствующими выходами распределителя, при этом выходы блоков элементов И являются вторыми выходами блока управления. Регистры с второго по последний содержат на входе каждого разряда элемент ИЛИ, входы которого являются первым и вторым входами соответствующего разряда регистра, а выходы элементов ИЛИ подключены к входам соответствующих триггеров, выходы которых являются выходами регистров. На фиг. 1 представлена структур ная электрическая схема устройства для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов; на фиг. 2 - функциональная схема регистра. Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов содержйт регистры 1, ,..., 1{j(, генератор 2 единиц, блок 3 управления, содержащий распределитель 4, блоки 5|. ...5(j.i элементов И, дополнительный регистр 6, коммутатор 7, блоки 8, ...,8д элементов И, блоки 9,... ,9 сумматоров, блоки 10, Ю., умножения, регистры 1.) ,. k., 1.| содержат элементы ШШ 11, ,...11р, триггеры 12, ,. . ., 12Q. Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковьпс кодов работает следующим образом. Обрабатываемые локаторы стираний поступают на вход устройства. Количество исправляемых стираний для кода не превышает числа (d-1), где d кодовое расстояние. Первый локатор .стирания обрабатывается за один двоичный такт, второй - два двоичных такта и т.д. В первый такт обработки каждого локатора стирания коммутатор 7 подключает к входам блоков 8,,...8 элементов И выходы генератора .2 единиц, а в остальное время - выходы дополнительного регистра 6. Такой ре жим работы определяет блок 3 управления. На вход управления коммутато ра 7 подан первый выход распределителя 4. При обработке первого локато ра стирания единичный сигнал с второ го выхода распределителя 4 подключен к первым объединенным входам последнего блока 5ci-n элементов И. При обработке (d-2) локатора единичный сиг нал с (d-1)-го выхода распределителя 4 подключен к первым объединенным входам второго блока 5 элементов И. При обработке (d-l)-ro локатора единичный сигнал с d-ro выхода распределителя 4 подключен к входам первого блока 5, элементов И. В исходном. состоянии регистры обнулены. Значе ние первого локатора стираний через вход и выход первого блока 8 элемен тов И подается на входы первого блока 9 сумматоров, где складывается с нулем, поданным с выходов послед него регистра 1. Результат поступает на входы последующих сумматоров .. . „ нулем, 9о и складывается с так как на входы 82,...,8о, элементов И, начиная со второго, подаются нули с выхода коммутатора 7. Таким образом, с выхода последнего блока 9(51 сумматоров через входы и выходы последнего дополнительного блока Sjj.i элементов И значение первого локатора стираний записывается через первый вход в (б-1)-ый регистр 1. В остальные регистры 1,...,1d-i записьшаются нули, так как на первые входы блоков 5),...,5о|.| элементов И, кроме (d-2)-го, с выходов распределителя 4 подаются нулевые сигна лы. На первом такте обработки второго локатора его значение, прюходя через вход и вьЬсод первого блока 8 элементов И, складывается в первом блоке 9 сумматоров со значением первого локатора и полученная сумма с выхода блока 8- сумматоров записывается через первый вход в (ё-2)-ой регистр. В (d-1)-ый регистр через второй вход записывается нуль с выхода (d-2)-го регистра. А значение первого локатора записывается с выхода (d-1)-го регистра в дополнительный регистр 6. На втором, последнем такте обработки второго локатора на выходе последнего блока 9а сумматоров получают сумму нуля с выходов . (d-1)-го регистра с произведением з конечном поле значений первого.локатора с выхода дополнительного регистра 6 и второго локатора со входа устройства. С выходов блоков 1 ОI,...,10д., умножения получают сдвиги значений второго локатора, которые складываются в блоках 9) ,...,9(3 сумматоров, если соответствующий разряд числа с выхода коммутатора 7 равен единице. В данном случае на выход коммутатора 7 подключено значение с выхода дополнительного регистра 6. А на вход первого блока 9| сумматоров подано нулевое значение с выхода (d-1)-го регистра. Полученное произведение записывается в (3-2)-ой регистр. Значение из (d-2)-го регистра переписывается в (б-1)-ый регистр, из (3-1)-го в дополнительный регистр 6. Остальные локаторы стираний обрабатываются аналогичным способом. При этом при обработке блок 3 управления переключает выход последнего блока 9о сумматора с первого входа регистра на первый вход (i-l)-ro регистра, на остальные первые входы регистров 11 ,..., 1 (3-1 поданы нулевые сигналы с выходов блока 3 управления. Запись значений чисел в триггеры 12 регистров со второго по (с}-1)-ый производится по двум входам, объединенным элементш и ИЛИ. После обработки всех локаторов стираний с выходов регистров 1| ,...1сЗ-| и генератора 2 единиц получают необходимый результат. Такое построение устройства позволяет обработать (d-1) докатор стираний за У двоичных тактов. В прототипе для обработки (d-1) локаторов стираний требуется (cJ-1) двоичных тактов. При числе обрабатываемых локаторов стираний, равном разрядности чисел конечного поля, в . предлагаемом устройстве для обработ511165446

ки требуется в 2 раза меньшее коли- оборудования, а именно регистров с чество тактов.обратнь ми связями, регистров циклиТаким образом, упрощение устройст- ческого сдвига и накапливающих суммава достигается за счет сокращения торов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов | 1987 |

|

SU1481902A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для умножения элементов конечных полей | 1984 |

|

SU1226445A1 |

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| Устройство для умножения элементов конечных полей | 1983 |

|

SU1124291A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МНОГОЧЛЕНА ЛОКАТОРОВ СТИРАНИЙ ПРИ ДЕКОДИРОВАНИИ НЕДВОИЧНЫХ БЛОКОВЫХ КОДОВ, содержащее oi блоков элементов И, входы первого из которых являются входами устройства, а блоков сумматоров, d -1 регистров, выходы которых являются выходами устройства, и генератор единиц, выходы которого являются вькодами устройства, при этом выходы каждого блока элементов И подключены к ne iBbiM входам соответствующего блока сумматоров, о т л ичающе ее я тем, что, с целью сокращения времени обработки информации при одновременном упрощении устройства, введены блок управления, дополнительный регистр, коммутатор и а-1 последовательно соединенных блоков умножения, при этом выход каждого :1-го блока умножения (, 2, ..., О-1) подключен к первым входам (i+1)-ro блока элементов И, причем входы первого блока умножения объединены с первыми входами первого блока элементов И, выходы i-ro блока сум 1аторов подключены к вторым входам (t + O-ro блока сумматоров, а выходы последнего блока сумматоров подключены к входам блока управления, первый выход которого подключен к управляющему входу коммутатора, а вторые выходы блока управления подключены к входам регистров, выходы i-го регистра (i,2,..., d-2) подключены к вторым входам (i+1)-ro регистра, а выходы последнего регистра подключега к вторым входам первого блока сумматоров и к входам дополнительного регистра, выходы которого подключены к первым входам коммутатора, к вторым входам которого подключены выходы генератора единиц, а выходы 3 коммутатора подключены к вторьм входам соответствующих блоков элементов И. 2.Устройство по п. 1, о т л и чающееся тем, что блок управления содержит распределитель, первый выход которого является первым выходом блока управления, и d -1 блоков элементов И, первые входы которых являются входами блока управления, а вторые входы соединены с соCb СП 4 4 ответствующими выходами распределителя, при этом выходы блоков элементов И являются вторыми выходами блока управления. 3.Устройство по п. 1, отличающееся тем, что регистры со второго по последний содержат на входе каждого разряда элемент ИЛИ, входы которого являются первым и вторым входами соответствующего раз ряда регистра, а выходы элементов ИЛИ подключены к входам соответствующих триггеров, выходы которых являются выходами регистров.

puS.

Выжо

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Экспресс-информация | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Блох Э.Л., Зяблов В.В | |||

| Обобщенные каскадные коды | |||

| М., Связь, 1976, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-30—Публикация

1983-04-27—Подача