4 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов | 1983 |

|

SU1116544A1 |

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для кодирования линейных полиномиальных кодов | 1989 |

|

SU1711338A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2013 |

|

RU2541869C1 |

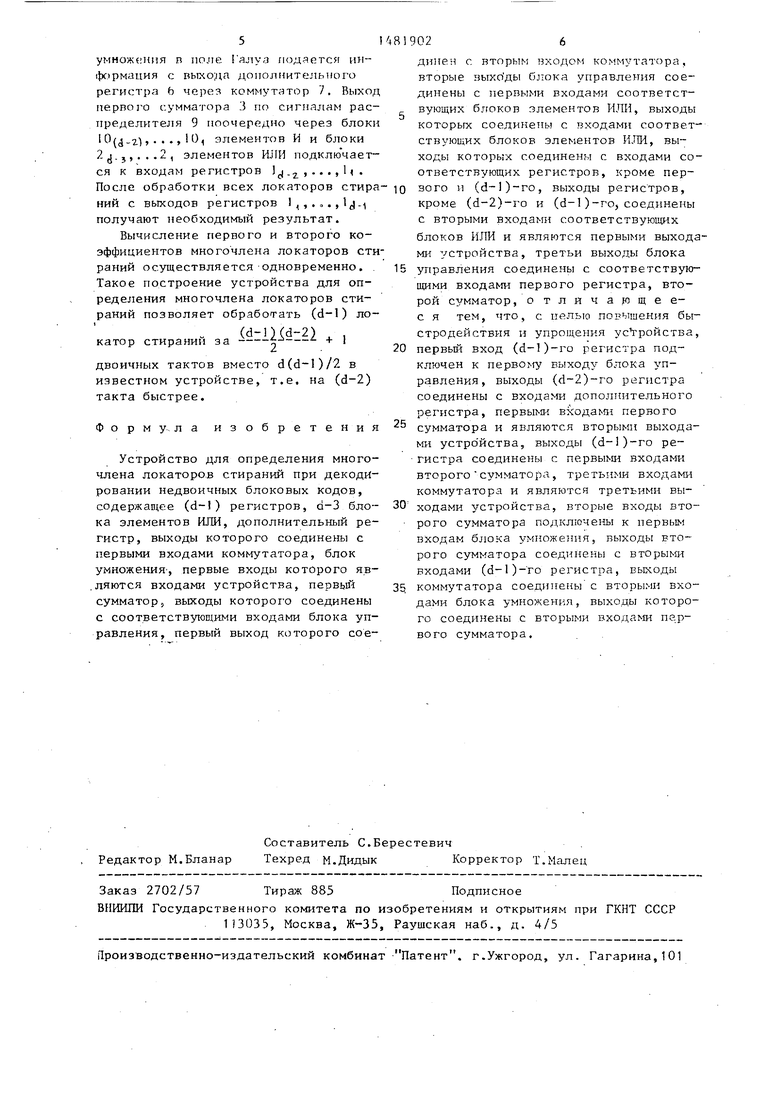

Изобретение относится к технике передачи дискретной информации и может быть применено в декодирующих устройствах аппаратуры передачи данных. Цель изобретения - повышение быстродействия и упрощение уа. Устройство содержит регистры 11÷1D-1, блоки 21÷2D-3 элементов ИЛИ, первый и второй сумматоры 3, 4, блок 5 умножения, дополнительный регистр 6, коммутатор 7 и блок 8 управления, содержащий распределитель 9 импульсов и блоки 10.1÷10. (D-2) элементов И. 1 ил.

СО О ГчЭ

Изобретение относится к технике передачи дискретной информации и мо- жег быть применено в декодирующих устройствах аппаратуры передачи данных .

Цель изобретения - повышение быстродействия и упрощение устройства.

На чертеже представлена структурная электрическая схема устройства.

Устройство для определения много-- члена локаторов стираний при декодировании недвоичных блоковых кодов содержит регистры 1,-lj., , блоки 2.,, элементов ИЛИ, первый 3 и второй 4 сумматоры, блок 5 умножения, дополнительный регистр 6, коммутатор 7 и блок 8 управления, содержащий распределитель 9 импульсов и блоки г) элементов И.

Устройство работает следующим образом.

Устройство вычисляет коэффициенты многочлена локаторов стираний

I

И Q(Z) П (1+X--Z).

) J Обрабатываемые локаторы стираний

/С последовательно поступают на вход устройства. Вычисления проводятся по реккурентным формулам. Если за (k-1) шагов определен многочлен локаторов стираний

,,

+а

-г

Z г+.. ,+a,Z+l ,

то коэффициент многочлена стираний на К шаге

- 1

а0

а

+

а,., ак, + X;K

аV X,K.«k , .

Для вычисления требуется провести k операций сложения и (k-1) операций умножения в поле Галуа„ Количество исправляемых стираний для кода не превышает (d-1), где d - кодовое расстояние. Количество двоичных тактов при обработке каждого локатора стираний определяется числом операций умножения. Первый локатор стирания обрабатывается за один такт, второй также за один такт, третий - за два двоичных шкта, четвертый - за три и т.д. В первый такт обработки каждого локатора стирания коммутатор

0

5

0

5

0

5

0

5

0

5

7 подключаем к лходу умножителя 5 в поле Ралуа выходы последнего регистра I ( , а в остальное время - выходы дополнительного ре:истра 6. Такой режим работы коммутатора 7 определяется управляющим сигналом с первого выхода распределителя 9 блока 8 управления. Также по этому сигналу с первого выхода распределителя

9,поданному на первый тактовый вход последнего регистра ,, , осуществляется тапись информации с выхода второго сумматора 4 в регистр

При обработке второго локатора стирания единичный сигнал с второго выхода распределителя 9 подан на первые объединенные входы последнего i блока 10 (j 2) элементов И. При обработке (d-2) локатора единичный сигнал с (d-2) выхода распределителя 9 подан на первые объединенные входы второго блока 10z элементов И. При обработке (d-l)-ro локатора единичный сигнал с (d-l)-ro выхода распределителя 9 подан на входы первого блока

10,элементов И. В исходной состоянии все регистры 1 обнулены. Значение первого локатора стирания через вход и выход второго сумматора 4 записывается в регистр ij, , В остальные регистры 1, , . f . 1 (j-a записываются нули, так как на первые входы блоков 10 i,.. . 1 О (j г) элементов И с выходов распределителя 9 подаютсй нулевые сигналы.

На первом такте обработки второго локатора его значение складывается в втором сумматоре 4 со значением первого локатора с выхода регистра 1j , и полученная сумма записывается в регистр Ij-f . Одновременно значение второго локатора умножается в блоке 5 умножения в поле Галуа на величину первого локатора, поданного с выхода ком 1утатора 7, полученное произведение складывается в сумматоре 3 с нулем с выхода регистра и через блок 10.2 элементов И запч- сывается в регистр Обработка второго локатора стирания закончена. Остальные локаторы стирания обрабатываются аналогичным образом. При этом при обработке остальных локаторов стирания на втором и следующих ыктах работы на второй вход блока 5

5

умножения п поле алуз подается информация с выхода дополнительного регистра Ь через коммутатор /. Выход первого сумматора 5 по сигналам распределителя 9 поочередно через блоки 1 0(,.), . . ., 10, элементов И и блоки 2 3,...2, элементов ИЛИ подключается к входам регистров Ij .2 , ... , 1 . После обработки всех локаторов стираний с выходов регистров l,..,lj-i получают необходимый результат.

Вычисление первого и второго коэффициентов многочлена локаторов стираний осуществляется одновременно. Такое построение устройства для определения многочлена локаторов стираний позволяет обработать (d-1) ло(d-l)(d-2) катор стирании заЈ + 1

двоичных тактов вместо d(d-l)/2 в известном устройстве, т.е. на () такта быстрее.

Формула изобретения

Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов, содержащее (d-) регистров, а-3 блока элементов ИЛИ, дополнительный регистр, выходы которого соединены с первыми входами коммутатора, блок умножения, первые входы которого являются входами устройства, первый сумматор, выходы которого соединены с соответствующими входами блока управления, первый выход которого сое819026

дине и г вторым чходом коммутатора, вторые выхо ды б::ока управления соединены с первыми входами соответствующих блоков элементов ИЛИ, выходы которых соединены с входами соответствующих блоков элементов ИЛИ, выходы которых соединены с входами соответствующих регистров, кроме пер- io зого и (,)-ro, выходы регистров, кроме (d-2)-ro и (d-1)-го, соединены с вторыми входами соответствующих блоков ИЛИ и являются первыми выходами устройства, третьи выходы блока

15 управления соединены с соответствующими входами первого регистра, второй сумматор, о тличающее- с я тем, что, с целью повышения быстродействия и упрощения устройства,

20 первый вход (d-l)-ro регистра подключен к первому выходу блока управления, выходы ()-ro регистра соединены с входами дополнительного регистра, первыми входами первого сумматора и являются вторыми выходами устройства, выходы (d-l)-ro регистра соединены г первыми входами второго сумматора, третьими входами коммутатора и являются третьими вы30 ходами устройства, вторые входы второго сумматора подключены к первым входам блока умножения, выходы второго сумматора соединены с вторыми входами (d-l)-ro регистра, выходе

35 коммутатора соединены с вторыми входами блока умножения, выходы которого соединены с вторыми входами первого сумматора.

25

| Устройство для определения многочлена локаторов стираний при декодировании недвоичных блоковых кодов | 1983 |

|

SU1116544A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-07-30—Подача