входного приемника, а третий и четвёртый входы - с выходом первого триггера и вторым входом четвертого триггера, третий вход которого подключен к выходу третьего триггера, а выход является выходом сигнала сбоя устройства.

3. Устройство по пп. 1 и 2, о т лич-ающееся тем, что узел

624

с.чета времени содержит генератор импульсов, счетчик и элемент задержки, причем информационны вход и вход начальной установки счетчика являются соответственно информационным и управляющим входами узла,тактовый вход соединен с 5ыходом генератора имггульсов, выход счетчика соединен с выходом узла и через элемент задержки с своим управляющим входом записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с общей магистралью | 1981 |

|

SU1022142A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБМЕНОМ ПО АСИНХРОННОЙ МАГИСТРАЛИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее входной приемник, вход которого подключен к входной шине синхронизации магистрали устройства, выходной усилитель, выход которого подключен к выходной шине синхронизации магистрали устройства, два элемента И и два триггера, причем первый вход первого триггера соединен с выходом первого элемента И, первый вход которого является входом синхронизации устройства, первый вход второго элемента И соединен с выходом входного приемника, отличающееся тем, что, с целью повышения пропускной способности системной магистрали, в него введены регистр управления, шифратор уставки времени, узел счета времени и три элемента И-ИЛИ, причем информационный вход шифратора уставки времени через регистр управления соединен с командным входом устройства, управляющий вход - с выходом первого триггера и входом выходного усилителя, а выход - с информационным входом узла счета времени, выход которого соединен с вторым входом первого триггера, а управляющий вход - с входом задания псевдоузсинхронного режима обмена устройства, первым входом первого элемента И-ИЛИ и первыми и вторыми входами второго и третьего элементов И-ИЛИ, третьи входы второго и третьего элементов И-ЙПИ подключены к выходу входного приемника, а выходы - соответственно к первому и второму входам второго триггера, выход которого является выходом синхронизации устройства, третий вход подключен к шине логического .нуля, а четвертый вход - к выходу второго элемента И, вторым вхо§ дом соединенного с четвертым и пятым входами третьего элемента И-ИЛИ, вхо(Л дом задания асинхронного режима обмена устройства, вторым входом первого элемента И и вторым и третьим вхрдами первого элемента И-ИЛИ, четвертый вход которого соединен с входом синхронизации устройства и шестым входом третьего элемента И-ИЛИ, а выход - с третьим входом первого триггера, четвертый вход первого элемента И-ИЛИ 9) N3 4 подключен к выходу первого триггера, а пятый и шестой входы - соответственно к входам режима приема и передачи устройства. 2. Устройство по п. 1, отличающееся тем, что, с целью повышения достоверности передачи информации, в него введен узел контроля, содержащий третий и четвертый триггеры, причем первый вход третьего триггера соединен с первым входом четвертого триггера и входом задания псевдоасинхронного режима обмена устройства, второй вход - с выходом

1

Изобретение относится к. вычигаительной технике и может быть использовано в вычислитепьных сисгсмах, построенных на .базе общей мат-исчра.чи

Изв-естно многоканальное устройство для подключе ия источников информации к обшей магчн-трали, содержащее в каждом канале i ри лереключительных элемента, пять тригтррон, семь элементов И, три элемента задержки, два элемента ИК, генератор сигналов опроса, три элемента Н111- i

Недостаток устро)(С1н ч состоит i; низкой пропускной способности.

Наиболее близким к предлагаемому является узел упранткмшн устроГк.тна для сопряжения с обшоГ магистралью вычислительной системой, содержащий четыре элемента И, два элементаИК, элемент ИЛИ, элемент зад.фжки, два триггера, приемные и передак)|цие , усилители, причем nepBi.ie входы п(рвого и второго элементов И соединены с первым входом синхронизации, второй вход которых соединен через первый элемент НЕ с первым входом первого элемента И и управляющим входом устройства, а выходы - соответственно с первым входом элемента ИЛИ и первым входом первого триггера, выходом подключешюго к второму входу элемента .ИЛИ, выход которого соединен черезэлемент задержки с входом передающего усилителя, выход которого подключен к соответствующей выходной щине синхронизации магистрали, вход приемного усилителя соединен с входной шиной синхронизации, а выход - с первым входом третьего тпемента И и вторым входом первого

триггера, первый вход четвертого элемента И с вторым входом синхронизации устройства, второй - с выходом синхронизации устpoiicTBa и выходом третьего элемента, И, вторым входом подключенного к выходу второго триггера. Устройство обеспечивает обмен по магистрали как в асинхронном, так и в синхронном

1)ежимах обмена 2j .

Недостатком устройства является низкая пропускная способность, так как поддержание пос.тоянного темпа обмена при работе в синхронном режиме осуществляется с задержками,

постоянными для всех абонентов, а не индивидуальными для каждого абонента. Кроме- того, при работе в синхронном режиме необходимо переключать в этот

режим и абонент.

Цель изобретения - повышение пропускной способности системной магистрали.

Поставленная цель достигается

тем, что в устройство для управления обменом по асинхронной магистрали вычислительной системы, содержащее входной приемник, вход которого подключен к входной шине синхрони-зации

магистрали устройства, выходной усилитель, выход которого подключен к выходной тине синхронизации магистрали устройства, два элемента И и два триггера, причем первый вход первого

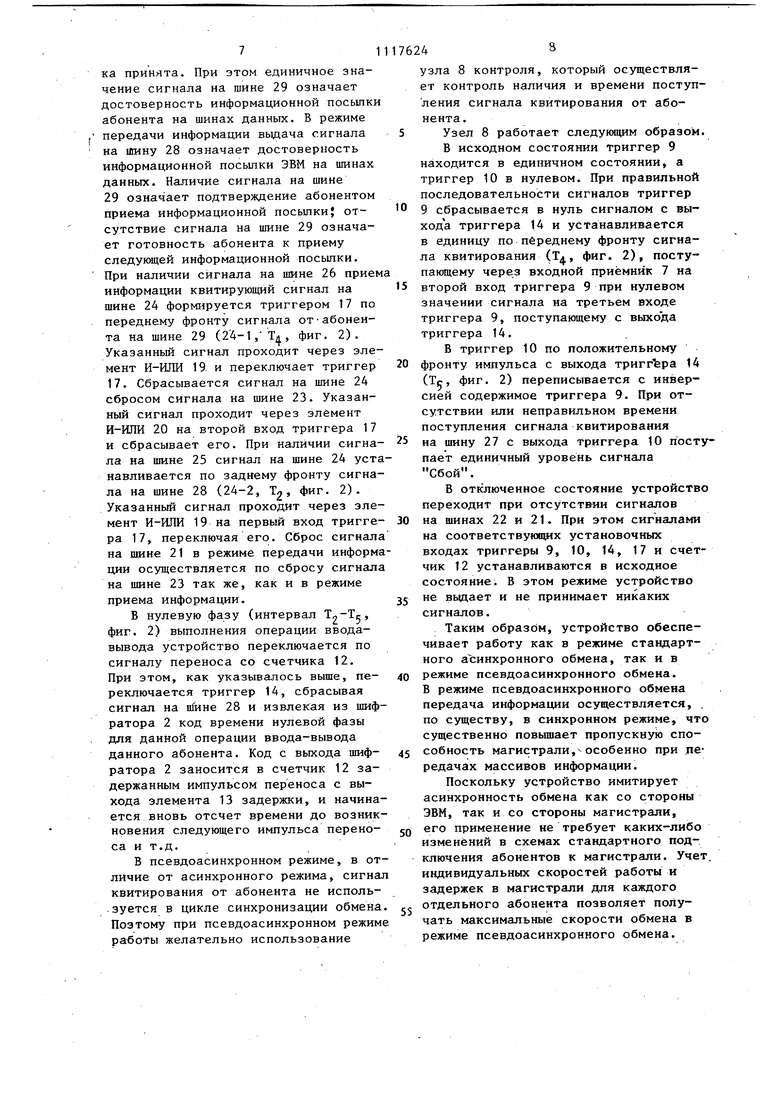

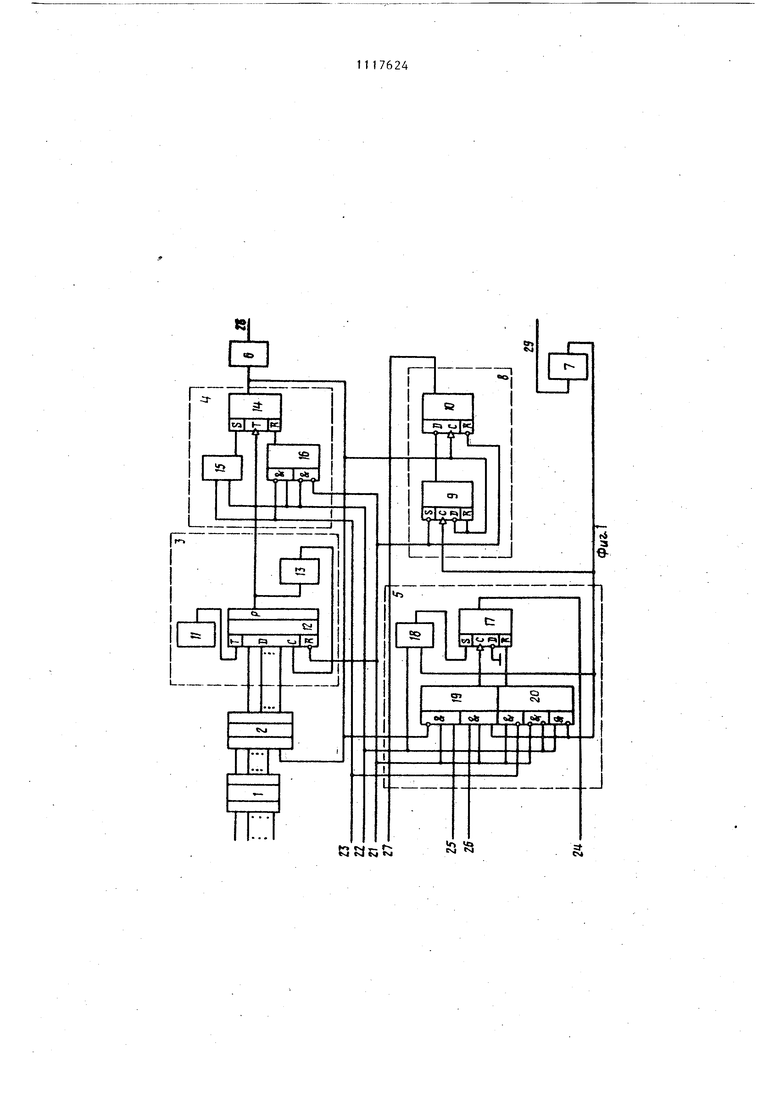

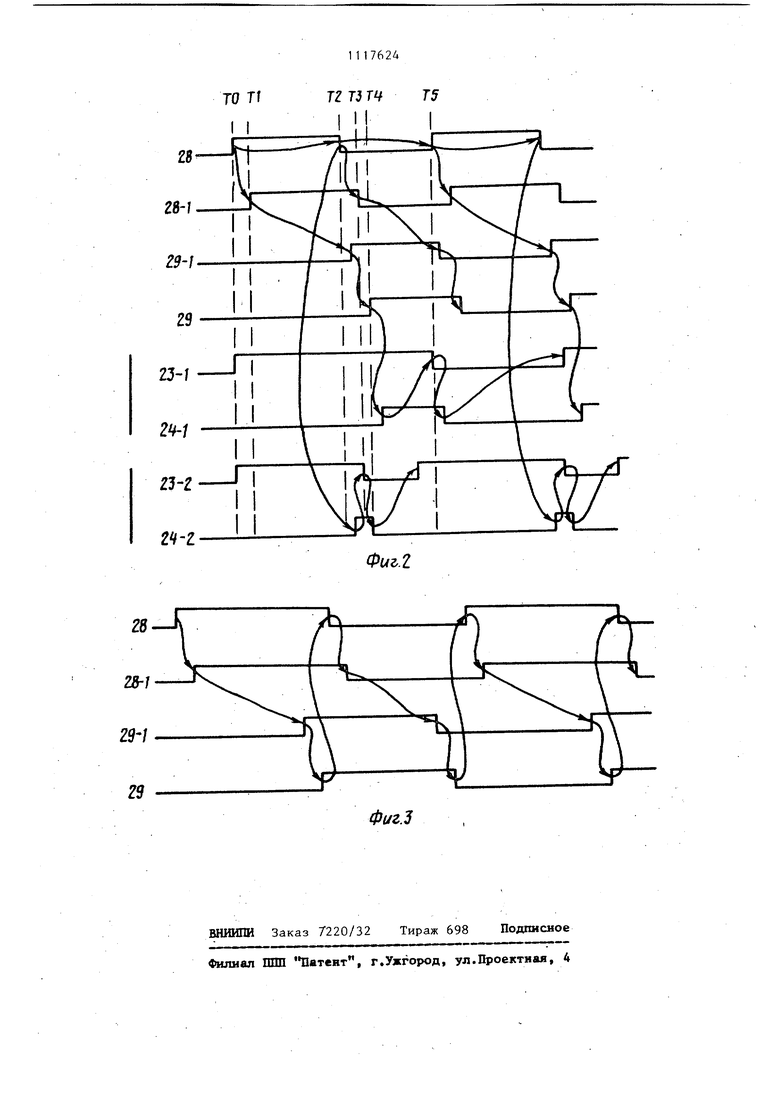

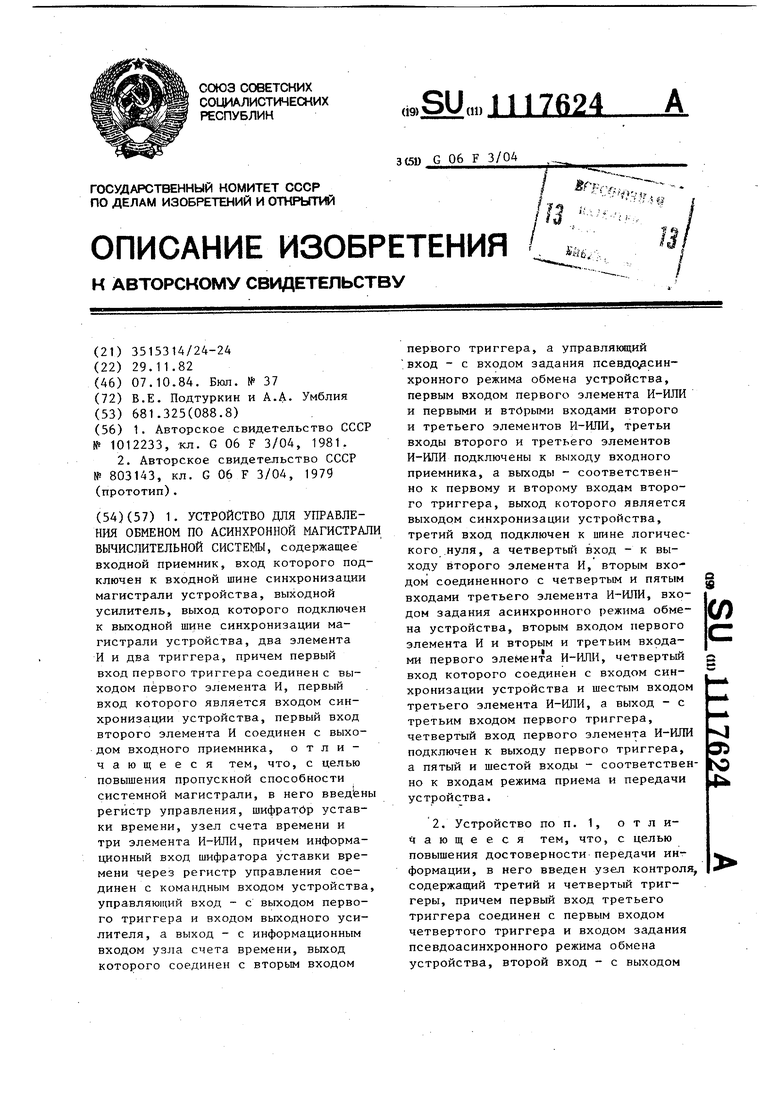

триггерасоединен с выходом первого элемента И, первый вход которого является входом синхронизации .устройства, первый вход второго элемента И соединен с выходом входного приемника, введены регистр управления. 3 шифратор уставки времени, узел сч та времени и три элемента И-ИЛИ, причем информационный вход шифратор уставки времени через регистр управ ления соединен с командным входом устройства, управляющи вход - с вы ходом первого триггера и входом вых ного усилителя, а выход - с информа ционным входом узла счета времени, выход которого соединен с вторым вх дом первого триггера, а управляющий - с входом задания псевдоасинхронного режима обмена устройства, первым входом первого элемента И-Ш1 и первыми и вторыми входами второго и третьего элементов И-1ШИ, третьи входы второго и третьего ijieMiMiTon И-ИЛИ подключены -к выходу входно ч:) приемника, а выходы - соответственно к первому и второму входам второ го триггера, выход которогч) янчжтс выходом синхронизации устройства, третий вход подключен к тине логического нуля, а четвертьЕй вход - к выходу второго элемента И, вторым входом соединенного с четвертым и пятым входами третьего элемента H-liTlH, входом задания асинхронного режима обмена устройства, BTOPI.IM входом первого элемента И и вторым и третьим входами первого элемента И-ИЛИ, четвертый вход которого соединен с входом синхронизации устройства и шестым входом третьего элемента И-Ш1И, а выход - с третьим входом первого триггера, четвертый вход первого э;темента И-ИЛИ подключен к выходу первого триггера, а пя тый и шестой входы - соответственно к входам режима приема и передач устройства. С целью повышения достоверности передачи информации, в него введен узел контроля, содержащий третий н четвертый триггеры, причем первый вход третьего триггера соединен с первым входом .четвертого триггера и- входом задания псевдоасинхронного режима обмена устройства, второй вход - с выходом входного приемника а третий и четвертый входы - с выхо дом первого триггера и вторым входом четвертого триггера, третий вход которого подключен к выходу третьего триггера, а выход является выходом сигнала сбоя устройства. Узел счета времени содержит гене ратор импульсов, счетчик и элемент 4, 4 задержки, причем информационньй вход и «ход начальной установки счетчика являются соответственно информационным и управляюш м входами узла, тактовый вход соединен с выходом генератора импульсов, выход счетчика соединен с выходом узла и через элемент задержки - с своим управляющим входом записи. На фиг. 1 приведена функциональная схема устройства;, ча фиг. 2 временная диаграмма работы устройства в пс(Вл1,оасинхронном режиме; на фиг. 5 - то же, в асинхронном режиме . Устройство (фиг. 1) содержит регистр 1 управления, шифратор 2 уставки времени, узел 3 счета времени, Олок 4 сопряжения с магистралью, блок 5 сопряжения с устройством, выходной усилитель 6, входной приемник 7, узел 8 контроля, содержащий третий 9 и четвертый 10 триггеры, узел 3 счета времени содержит генератор 11 импульсов, счетчик 12 и элемент 13 задержки. Блок 4 сопряжения с магистралью содержит первый триггер 14, первые элементы И 15 и И-ИПИ 16. Блок 5 сопряжения с устройством содержит второй триггер 17, второй элемент И 18 второй 19 и третий 20 элементы И-ИЛИ. На фиг. 1 ггоказаны также шины 21 и 22 входов задания ггсевдоасинхронного и асинхронного режимов устройства, шин(1 23 и 24 входа и выхода синхронизации устройства, шины 25 и 26 входов режима передачи и приема устройства и шина 27 выхода сигнала сбоя устройства, шины 28 и 29 синхронизации магистрали устройства. Через шины 28 и 29 устройство подключается к шинам синхронизации системной магистрали, к которой подключены абоненты (внешние устройства) системы, а через шины 21-27 - к устройству, обслуживающему системную магистраль, например ЭВМ. При комплектовании устройства в шифраторе 2, который может быть выполнен, например, на базе постоянной памяти, для каждого абонента кодируются времена выполнения операций ввода-вывода с учетом времени распределения сигналов в системной магистрали. Устройство работает следующим образом.

5

Устройство обеспечивает возможность работы в двух режимах - асинхронном и псевдоасинхронном. В асинхронном режиме работы устройство транслирует сигналы между ЭВМ и магистралью без преобразования. В псевдоасинхронном режиме устройство формирует последовательность сигналов синхронной передачи информации на шине 28, при этом сигналы на шинах как абонента, так и обслуживаемого вычислительного средства соответствуют временной диаграмме асинхронной обмена.

В асинхронный режим работы устройство переходит при поступлении сигнала на шину 22. Указанный сигнал поступает на элемент И 18 и элемент И-ИЛИ 20, разрешая прохождение через них на входы триггера 17 сигнала синхронизации с выхода входного приемника 7. При этом триггер 17 переключается при каждом изменении сигнала .на шине 29 и этот сигнал транслируется на шину 24 устройства. Кроме того, сигнал с шины 22, поступая на элементы И 15 и И-ИЖ 16, разрешает прохождение сигналов синхронизации с шины 23 на входы триггера 14. Триггер 14 переключается, при каждом изменений сигнала на шине 23. Таким образом, сигнал с шины синхронизации 23 без изменения транслируется на шину 28.

В псевдоасинхронный режим устройртво включается при поступлении сигнала на .шину 21, одновременно в зависимости от необходимости передачи или приема информации подается сигнал на шину 25 или 26. Кроме того, ЭВМ выставляет сигнал на шину 23, а в регистр 1 заносится код номера абонента, с которым производится сеанс обмена, и код операции вводавывода. После подачи сигнала на шину 21 на Входе начального установа счетчика 12 появляется разрешающий уровень, и счетчик 12 начинает обратный счет импульсов, поступающих с генератора 11. После первого же импульса на выходе счетчика 12 появляется сигнал переноса, переключающий триггер 14, с выхода которого сигнал поступает на шину 28 и через выходной усилитель 6 в шину синхронизации системной магистрали. Кроме того, указанный сигнал поступает на вход шифратора 2 и является призна76246

ком единичной фазы (интервал времени TQ-TJ на фиг. 2, в течение которого поддерживается единичное значение сигнала на шине 28) операции 5 ввода-вывода.

Помимо того, по сигналу переноса с выхода счетчика 12, поступающему через элемент 13 задержки на вход записи счетчика 12, в последний из

шифратора 2 заносится код времени выполнения единичной фазы операции ввода-вывода с данньм абонентом. Это соответствует моменту Т временной диаграммы фиг. 2.

5, На временной диаграмме (фиг. 2) приня.ты следующие обозначения: 28 и 29 - последовательность сигналов соответственно на шинах 28 и 29 28-1 и 29-1 - последовательность

0 сигналов на шинах 28 и 29 со стороны абонента, 23-1 и 24-1 - последовательность сигналов соответственно на шинах 23 и 24 устройства в режиме приема информации; 23-2 и 24-2 5 последовательность сигналов соответственно на шинах 23 и 24 в режиме передачи информации.

После установления начального кода времени счетчик 12 осуществляет

0 вычитание импульсов до появления следующего сигнала переноса, который переключает триггер 14, после чего на шине 28 устанавливается нулевой уровень, (интервал Т -Т ,

5 фиг. 2).

Сигнал на шине 28 достигает абонента через время ta, , требуемое для распространения сигнала по магИстрали (момент Т фиг. 2). Снимается сигнал на шине 28 со стороны абонента также с задержкой t . При этом длительность интервала выбирается (при кодировании в шифраторе 2) с таким расчетом, что

сигнал снимается с шины 28 абонента (28-1, Т-,.фиг. 2) через некоторое время ut (интервал , фиг. 2) после появления сигнала квитирования от абонента на шине 29 (29-1, фиг. 2). Сигнал квитирования на шине 24 для 5ВМ формируется по-разному в режимах: приема (сигнал на шине 26) и передачи (сигнал на шине 25) информации. В режиме приема ин5 формации выдача сигнала на шину 28 означает готовность ЭВМ к приему информации; снятие сигнала с щины 28 означает, что информационная посыл7ка принята. При этом единичное значение сигнала на шине 29 означает достоверность информационной посылки абонента на шинах данных. В режиме , передачи информации выдача сигнала на шину 28 означает достоверность информационной посылки ЭВМ на шинах данных. Наличие сигнала на шине 29 означает подтверждение абонентом приема информационной посыпки} отсутствие сигнала на шине 29 означает готовность абонента к приему следующей информационной посылки. При наличии сигнала на шине 26 прием информации квитирующий сигнал на шине 24 формируется триггером 17 по переднему фронту сигнала отабонента на шине 29 (24-1, Тл , фиг. 2). Указанный сигнал проходит через элемент И-ИЛИ 19. и переключает триггер 17. Сбрасывается сигнал на шине 24 сбросом сигнала на шине 23. Указанный сигнал проходит через элемент И-ИЛИ 20 на второй вход триггера 17 и сбрасывает его. При наличии сигнала на шине 25 сигнал на шине 24 уст навливается по заднему фронту сигнала на шине 28 (24-2, Ту Фиг. 2). Указанный сигнал проходит через элемент И-ИЛИ 19 на первый вход триггера 17, переключая его. G6poc сигнала на шине 21 в режиме передачи информ ции осуществляется по сбросу сигнала на шине 23 так же, как и в режиме приема информации. В нулевую фазу (интервал Yy-Tc, фиг. 2) выполнения операции вводавывода устройство переключается по сигналу переноса со счетчика 12. При этом, как указывалось выше, переключается триггер 14, сбрасывая сигнал на п1ине 28 и извлекая из шиф ратора 2 код времени нулевой фазы для данной операции ввода-вывода данного абонента. Код с выхода шифратора 2 заносится в счетчик 12 задержанным импульсом переноса с выхода элемента 13 задержки, и начинается вновь отсчет времени до возник новения следующего импульса переноса и т.д. В псевдоасинхронном режиме, в от личие от асинхронного режима, сигна квитирования от абонента не используется в цикле синхронизации обмена Поэтому при псевдоасинхронном режим работы желательно использование 48 узла 8 контроля, который осуществляет контроль наличия и времени поступления сигнала квитирования от абонента. Узел 8 работает следующим образом. В исходном состоянии триггер 9 находится в единичном состоянии, а триггер 10 в нулевом. При правильной последовательности сигналов триггер 9 сбрасывается в нуль сигналом с вы хода триггера 14 и устанавливается в единицу по переднему фронту сигнала квитирования (Т, фиг. 2), поступающему через входной приёмник 7 на второй вход триггера 9 при нулевом значении сигнала на третьем входе триггера 9, поступающему с выхода триггера 14. В триггер 10 по положительному фронту импульса с выхода триггера 14 (Тс, фиг. 2) переписывается с инверсией содержимое триггера 9. При отсутствии или неправильном времени поступления сигнала квитирования на шину 27 с выхода триггера 10 поступает единичный уровень сигнала Сбой. В отключенное состояние устройство переходит при отсутств-ии сигналов на шинах 22 и 21. При этом сигналами на соответствующих установочных входах триггеры 9, 10, 14, 17 и счетчик 12 устанавливаются в исходное состояние. В этом режиме устройство не вьщает и не принимает никаких сигналов. Таким образом, устройство обеспечивает работу как в режиме стандартного асинхронного обмена, так и в режиме псевдоасинкронного обмена. В режиме псевдоасинхронного обмена передача информации осуществляется, по существу, в синхронном режиме, что существенно повышает пропускную способность магистрали,особенно при передачах массивов информации. Поскольку устройство имитирует асинхронность обмена как со стороны ЭВМ, так и со стороны магистрали, его применение не требует каких-либо изменений в схемах стандартного подключения абонентов к магистрали. Учет, индивидуальных скоростей работы и задержек в магистрали для каждого отдельного абонента позволяет получать максимальные скорости обмена в режиме псевдоасинхронного обмена.

ЙЯйК

а

М

Фиг,.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1981 |

|

SU1012233A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 803143, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-07—Публикация

1982-11-29—Подача