Изобретение относится к измерительной технике, а именно к устройствам записи и воспроизведения однократных сигналов. Известно устройство для цифрового измерения и регистрации дискретных значений однократного сигнала, содер жащее аттенюатор, аналого-цифровой преобразователь, блок основной памяти, индикатор, синхронизатор, блок памяти предыстории, мультиплексор, два регистра, вычитатель, цифровой компаратор, два триггера, схему И, счетчики адресов памяти предыстории и основной памяти ij . Однако это устройство обладает низкой разрешающей способностью. Наиболее близким техническим реше нием к изобретению является-устройст во для 1ЩФРОВОГО измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса, содержащее аналого-цифрово преобразователь, выход которого подключен к входу л.ока определения границ сообщений и к первому входу первого блока памяти одновременно, а выход последнего соединен с первым входом мультиплексора, выход которог подсоединен к входу индикатора, при этом вьЕход блока определения границ сообщений соединен с первым входом триггера, а вторые входы первого и второго блоков памяти соединены с вы ходами первого и второго счетчиков адресов соответственно, семь элементов И, счетчик объема сигнала, первый и второй счетчики объема памяти формирователь импульсов и блок управ ления, причем выход аналого-цифрового преобразователя соединен с первым входом второго блока памяти, выход которого подсоединен к второму входу мультиплексора, управляющий вход которого соединен с первым выходом блока, управления, второй и третий выходы которого подключены к первым входам первого и второго элементов И соответственно, вторые входы которых объединены между собой и соединены с первьм выходом блока синхронизации и с управляющим входом аналого-цифрового преобразователя одновременно, а выходы первого и второго элементов И подключены к входам первого и второго счетчиков адреса соответственно, кроме того, второй выход синхронизатора подсоединен к первому 72 входу третьего злег-септа И;, второй .вход которого с.ое1-,Илен с Q-вьжпдом триггера, а - с входом счетчи ка объема сигнал.а, выход которого через формировате.пь подключен к второму входу триггера и первому входу блока упраЕ.пения одновременно,- причем второй зход блока управления соединен с управляюш:1;;м въкодом блока определения границ сообщений, третий - с клеммой Пуск, а четвертый - с выходом первого счетчика объема памяти, вход которого подсоединен к выходу четвертого элемента И, первый вход которого соединен с первым входом пятого элемента И и третьим выходом синхронизатора одновременно, а второй 13ХОД четвертого элемента И -- с четвертым выходом блока управленияэ пятый выход которого подключен к второму входу пятого элемента И, вь.гход которого соединен с входом второго счетчика объема павходом блока управления, при этом шестой и се.дьмой выходы блока управления подсоединены к первым входам шестого и седьмого элементов И, вторые входы которых соединены с четвертым и пятым выходаг м синхронизатора соответственно, а выходы шестого и седьмого .элементов И - с управляющими входаг.п второго и первого блоков памяти соответственно 2j. Однако в известном устройстве вывод дискретньЕх отсчетов однократ- кого сигнала начинаетсятолько после полной его записи в память, поэтому имеется некоторая задержка между срабатыванием блока определения границ сигнала и выводом сигнала на индикатор , что снижает быстродействие устройства. В некоторых случаях такая задержка нежелательна, например при работе с ЭВМ. Кроме того, при применении памяти, быстродействие которой выше, чем это требуется для записи информации с аналого-цифрового преобразователя, устройство неоправдано сложно. Целью изобретения является повыше ние быстродействия и упрощение устройства. Поставленная цель достигается тем, что в устройство для цифрового . измерения, запоминания и воспроизве-ения дискретных значений однократного сигнала, содержащее аналого.1

цифровой преобразователь, формирователь сигналов, блок памяти, блок синхронизации, блок индикации, мультиплексор, первый и второй счетчики адресов, элементы И, первьй триггер, счетчик считанных слов и блок управления, причем первый вход аналогоцифрового преобразователя является входом устройства, второй вход подключен к первому вых.оду блока синхронизации, а выход соединен с первым входом блока памяти и входом формирователя сигналов, выход которого подключен к входу блока управления, первый выход которого соединен с одним из входов первого триггера, выход которого подключен к первому входу первого элемента И, второй и третий выходы блока синхронизации подключены к второму входу первого и первому входу второго элементов И, выход) которых соединены соответственно, с входом первого счетчика адресов с первым входом второго счетчика адресов, введены вычитатель, регистр, блок сравнения и второй триггер, входы которого подключены соответственно к второму выходу блока управления и выходу счетчика считанных слов, первый вход которого соединен с третьим вькодом блока синхронизации, выход второго триггера подключен к вторым входам счетчика считанных слов и второго элемента И, выходы Счетчиков адресов соединены с первым и вторым входами мультиплексора и входами блока сравнения, выход которого подключен к другому входу первого триггера, выход формирователя сигналов соединен с первым входом второго счетчика адресов, второй вход которого подключен к выходу вычитателя, входы которого соединены соответственно с вькодом первого счетчика адресов и выходом регистра, четвертый выход блока синхронизатщи подключен к второму входу блока памяти и третьему входу мультиплексора, выходы которых соединены соответственно с входом блока индика1уи и третьим входом блока памяти,

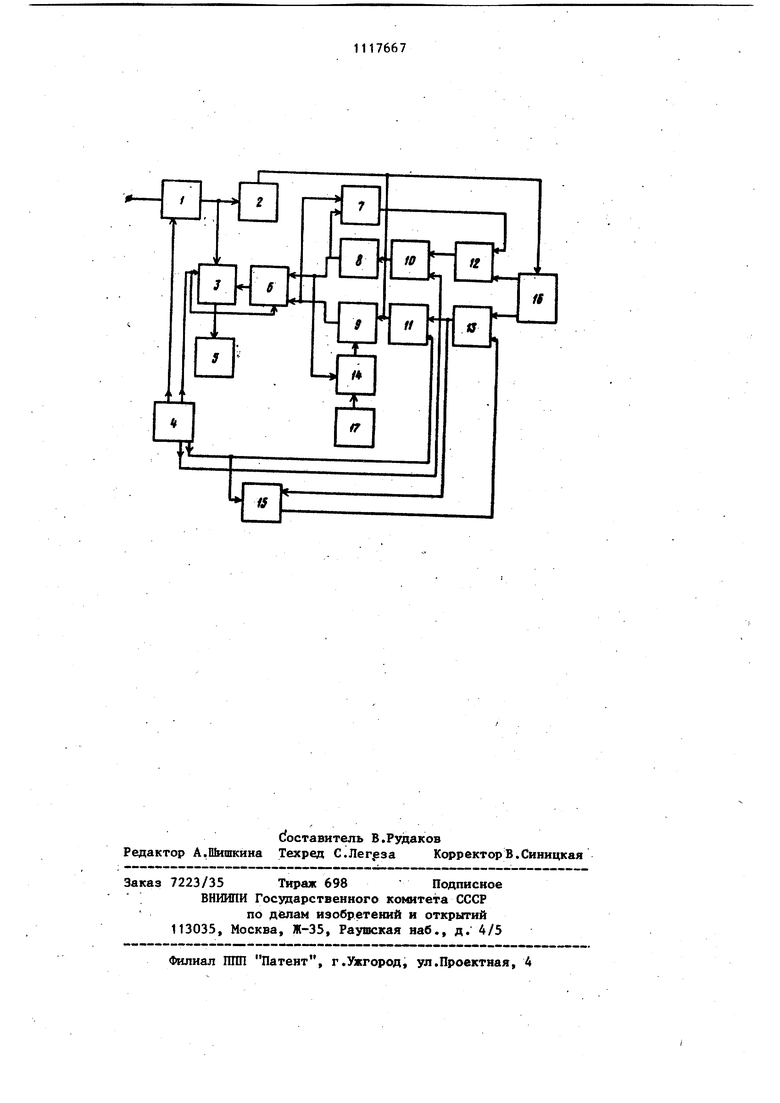

На чертеже изображена структурная схема -предложенного устройства.

Устройство содержит аналого-цифровой преобразователь (АЦП) 1, формирователь 2 сигналов, служащий для формирования импульсов, определяющих

76674

границы слова (сообщения), блок 5 памяти, блок 4 синхронизации, блок 5| индикации, мультиплексор 6, блок 7 сравнения, первый 8 и второй 9 счет5 чики адресов, первьй 10 и второй 11 элементы И, первьй 12 и второй 13 триггеры, вычитатель 14, счетчик 15 считанных слов, блок 16 управления и регистр 17, служащий для хранения

0 предыстории.

Устройство работает следуюпщм образом.

По сигналу Пуск от блока 16 устанавливается в единицу первый

5 триггер 12, и импульсы от блока 4 поступают через элемент И 10 на счетчик 8. Если в этот момент на блок 3 памяти подается сигнал Запись, то мультиплексор 6 подключает

0 выходы счетчика 8 к адресным входам блока 3 памяти и в выбранную ячейку записываются коды с выхода АЦП 1. В следующем такте (через интервал Т, меньший, чем интервал Тл, который

5 равен времени преобразования АЦП) на входе блока 3 памяти изменяется сигнал на Чтение, что приводит к подключению через мультиплексор 6 выходов счетчика 9 и из блока 3 счи0 тываются данные. В следующий такт блок 3 переходит снова в режим записи, а в счетчик 8 добавляется один импульс от блока 4 синхронизации, затем через интервал Tj блок 3 памяти

переходит в режим чтения, но содержимое счетчика 9 не изменяется, так как триггер 13 находится в исходном состоянии в нуле.

Таким образом происходит поочередная запись во все ячейки блока 3 памяти, при этом коды АЦП (К+1)-го преобразования записываются в блок 3 памяти на место первой ординаты и т.д.

При появлении на входе устройства электрического импульса на выходе АЦП 1 появляется код, резко отличающийся по величине от цифрового кода предьщущих моментов времени. Формирователь 2 вьфабатывает импульс, по переднему фронту которого в счетчик 9 записывается число, равное разности номера ячейки памяти, в которую в данньй момент записывается очередное дискретное значение входного сигнала, и числа, установленного на регистре 17. Одновременно импульс с выхода формирователя 2 посг }1 пает в блок 16 управления, где задерживается, если это необходимо по условиям согласования с блоком 5 прежде чем опрокидывает триггер 13 в состояние единишл. С этого момент импульсы от блока 4 синхронизации имеют возможность пройти через элемент И 11 на входы счетчиков 9 и 15 Импульсы от блока 4 синхронизации поступают на указанные сметчики только в момент, когда на входе блока 3 памяти имеется сигнал чтени При чтении адрес блока памяти определяется содержимым второго счетчика 9, начальное состояние кот рого равно разности, определяемой по выходу вычитателя 14, адресов памяти в момент срабатывания формирователя 2 и числа,.установленного на регистре 17. При таком решении скорость считьюания данных из блока памяти и скорость записи данньк в память может быть различна, поэто му при совпадении состояний счетчиков 8 и 9 появляется импульс на выходе блока 7 сравнения,который поступает на вход триггера 12 и опрокидывает его в нулевое состояние. Последзгкщее включение этого триггер возможно только от блока 16 по сигналу Пуск. Это.предохраняет наложение сигнала.на еще не считанную его часть. Даже при остановившемся 7 счетчике 8 на счетчик 9 адресов про должают цостУпать импульсы и происходит считывание информации из блока 3 памяти. В момент переполнения счетчика 15 считанных слов, объем которого устанавливается равным сум ме объема предыстории и сигнала, на его выходе появляется импульс, который опрокидывает триггер 13 в нулевое состояние, и на этом заканчивается процесс чтения инфсфмации из блока 3 памяти. Последунящй пуск возможен только по сигналу от блока 16. Таким образом, предложенное техническое решение позволяет записывать дискретные значения, однократного сиг- нала в блок памяти,, хранить их до вывода информашш, вывод дамвык из блока памяти ос пдествйять с минимальной задержкой после начала записи однократного сигнала, не ожидая его окончания, причем Ш|Шод осуществлять с предысторией сигнала. В устройстве имеется возмсякяость изменять как обь ем считываемой предыстории, так и объем сигнала, естествеиво, чтобы сумма объема предыстории и объема сигнала не превышала объема памяти. Уменьшение до минимума времени задержки между появле1&1ем сигнала и его выводом позволяет уяучоють разрешющую способность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса | 1980 |

|

SU868790A1 |

| Устройство запоминания и многократного воспроизведения электрических импульсов | 1976 |

|

SU617776A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1092567A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| Устройство для регистрации однократных электрических импульсов | 1982 |

|

SU1072070A1 |

УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ИЗМЕРЕНИЯ, ЗАПОМИНАНИЯ И ВОСПРОИЗВЕДЕНИЯ ДИСКРЕТНЫХ ЗНАЧЕНИЙ ОДНОКРАТНОГО СИГНАЛА, содержащее аналого-цифровой преобразователь, формирователь сигналов,.блок памяти, блок синхронизации, блок ивдикации, мультиплексор, первый и второй счетчики адресов, эле1Менты И, первый триггер, счетчик считанных слов и блок управления, причем первый вход аналого-цифрового преобразователя является входом устройства, второй вход подключен к первому выходу блока синхронизации, а выход соединен с первым входом блока памяти и входом формирователя сигналов, выход которого подключен к входу -блока управления, первый выход которого соединен с одним из входов первого триггера, выход которого пЬдключен к первому входу первого элемента И, второй и третий выходы блока синхронизации подключены к второму входу первого и первому входу второго элементов И, выходы которых соединены соотвеГтственно с входом первого счетчика адресов и первым входом второго счетчика адресов, отличающееся тем, что, с целью повьппения быстродействия и упрощения устройства, в него введены вычитатель, регистр, блок сравнения и второй триггер, входы которого подключены соответственно к второму выходу блока управления и выходу счетчика считанных слов первый вход которого соединен с третьим выходом блока синg хрониза1и1и, выход второго триггера подключен к вторым входам счетчика считанных слов и второго элемента И, выходы счетчиков адресов соединены с первым и вторым входами мультиплексора и входами блока сравнения, выход которого подключен к другому входу первого триггера, выход формирователя сигналов соединен с первым входом второго счетчика адресов, второй вход которого подключен к выходу вычита9 теля, входы которого соединены соота ветственно с выходом первого счетчика адресов и выходом регистра, четвертый выход блока синхронизации подключен к второму входу блока памяти и третьему входу мультиплексора, выходы которьос соединены соответственно с входом блока индикации и третьим входом блока памяти,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство запоминания и многократного воспроизведения электрических импульсов | 1976 |

|

SU617776A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для цифрового измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса | 1980 |

|

SU868790A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-10-07—Публикация

1983-07-11—Подача